在当今这个数字内容、互联网用户和物联网设备大爆炸的世界,人们对扩展通信网络能力的需求越来越高。为了满足这种需要,Teledyne e2v一直探索数字微波采样的前沿技术,最近已在实验套件上成功验证。它可支持K波段的直接数字下变频。这是今年的早些时候在ESA MTT workshop提出的使用EV12DS480宽带DAC实现直接K波段综合的工作的后续进展,在技术论文1和最近的网络研讨会2上有进一步的描述。

项目目的

这个项目的目标是实现24GHz的模拟前端,支持微波K 波段(即频率范围18到27GHz)信号能量的直接数字化。目标的无杂散动态范围(SFDR)优于50 dBc。

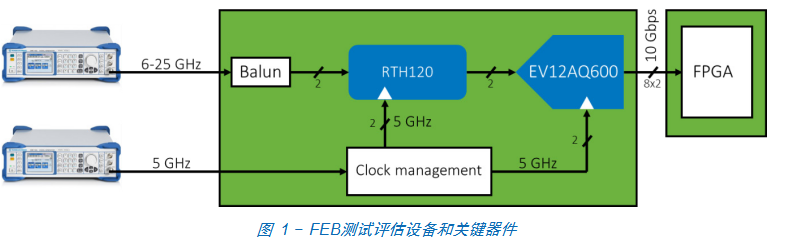

微波前端板(FEB)的开发和两个现有的GHz的高速器 件相关,这两个器件由Teledyne Scientific和Teledyne e2v分别开发。测试实验运行在高性能FEB上,整合了12位宽带数据转换器EV12AQ600和超高频双路追踪保持放大器(THA)RTH120。

前者的采样率高达6.4 Gsps,全功率输入信号带宽高达6.5 GHz。而追踪保持器的带宽高达24 GHz,并且拥有优异的线性度性能。因此,通过应用奈奎斯特定理并选择合适的采样频率,这套设备可直接从K波段下变频到 基带,从而使ADC直接采集有用的信号,无需额外的下变频电路。这一方案的指导原则是用途广泛的软件定义微波接收器,它提高了射频系统设计的敏捷度,同时简化了射频信号采集系统的设计,并潜在地降低了功耗。另外,我们也希望通过这个项目,在未来确实降低实际应用的功耗。

器件的核心参数

EV12AQ600 ADC

• 四核ADC,支持

1、2或4通道工作

• 交织模式的采样率高达6.4 Gsps

• 6.5 GHz 输入带宽(-3dB)

• 集成的宽带交叉点开关

• 支持多通道同步的同步链特性

RTH120 THA

• 24 GHz 输入带宽

• 双THA使得输出可保持超过半个时钟周期

• 全差分设计

这篇文档描述了研究的状态和最新的发现,并提出了需改进的部分。

我们将进行的一系列测试的目的是找出当今K波段(18到27GHz)直接下变频技术的不足。从下列初始的无杂散动态范围测试中可以发现三个问题:

• 输入信号功率对THA性能的影响

• 当工作在高奈奎斯特域时,低频校准对ADC交织性能的影响

• 在高奈奎斯特域采样时,ADC内部积分非线性(INL)错误的影响

最后,Teledyne e2v希望这个项目得出的结论对下一代K波段产品的设计有一些指导意义。

项目开始

前端板(FEB)的基本框图如图1所示。FEB被设计成包含宽带ADC和用作输入级的THA。仔细观察图2的FEB,会发现它包含了一些额外的支持器件,包括一个功分器、一个移相器和一些巴伦。板子还提供了两路独立的输入:一路绕过RTH120,优化第一和第二奈奎斯特域采样高达6GHz的性能(图中未画出);另一路用于6 到24GHz的宽带操作。在项目开始时,RTH120还是一 款正在经历优化的试生产产品。

这个实验系统初始的ADC默认配置如下:

• 输入带宽 (6.5 GHz)

• 一通道模式,所有四个核心交织成最大采样率(例如6.4Gsps)

• 采样频率设置成5Gsps

• 交织校准按照数据手册中标准默认的设置配置,在下文中都称之为CalSet0

第一次动态测试的结果

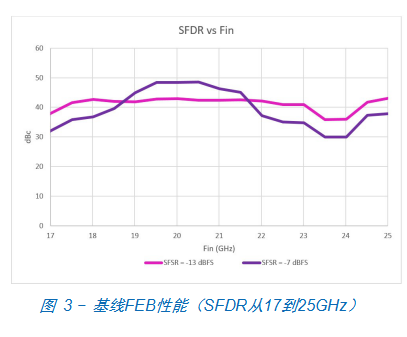

FEB的初始测试表现出波动的无杂散动态范围

(SFDR)响应(图3)。在不同的ADC信号满刻度范围

(SFSR)进行两次独立的扫频。扫频覆盖的信号频率超过30GHz。图3放大了17GHz到25GHz的范围。

检查初始结果

SFDR的特性有很大的分析价值,并为未来的动态性能提升提供了参考。从这些结果(图3)可以看出:

• 低输入信号功率的SFDR平坦度更好(图3比较了-7dBFS和-13dBFS的结果)

• 初始的实验配置难以实现我们预期的50dBc SFDR的目标

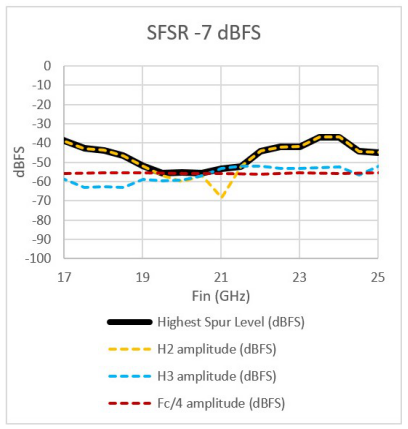

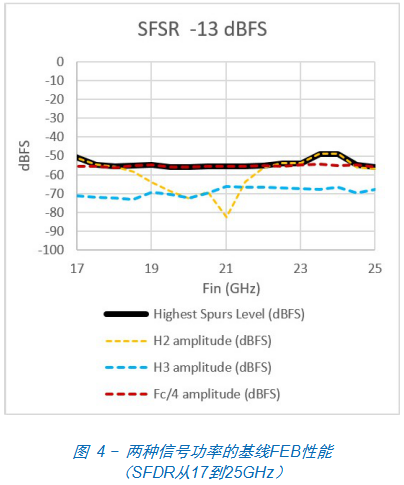

提高性能的第一步是找出限制SFDR的信号杂散。下图(图4)标出了输入电平-7dBFS和-13dBFS时主要的杂散,用dBFS表示。

从上图可以看出,对于不同的频率范围和输入幅度,变化的杂散频率分量可以看作SFDR波动的原因,请参考图中最大杂散的曲线。图中也标注了二次谐波(H2)和三次谐波(H3)以及采样时钟(Fc/4)的影响。仔细观察,您还会发现:

• 从最大杂散(深色曲线)可以看出,H2是最主要的影响因素,特别是对于-7dBFS。

• 如果H2可以被改进,下一个影响最大的因素显然是Fc/4 性能,它对小信号曲线(-13dBFS)的影响很大。但 是,对于上面两种信号功率,Fc/4限制SFDR大约在58dBFS(在18GHz到22GHz之间)。如果不改进这个问题,很难进一步提高动态性能。Fc/4的问题表明多个ADC核心交织可能产生的一些问题。杂散信号的根源是偏置不匹配。

• 通过优化,-13dBFS的SFDR有可能达到50到60dBc之间。

根据产品资料,唯一提升THA性能(通过降低H2)的方法是降低输入信号电平。这对SFDR受H2限制的场合很有用,例如-7dBFS的SFSR时19.5GHz以下或21.5GHz以上的范围。

优化数据转换器的性能

另一方面,ADC可提供默认工作方式以外的多种自由的配置。初始的测试表明核心交织的精度问题,这并不奇怪。标准的交织校准(ILG)是在工厂的产品测试时完成的。显然,它按照基带工作优化,并不适用于这种大带宽的应用。

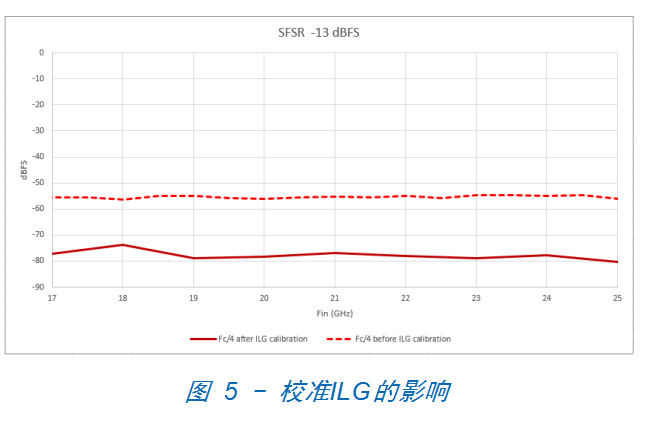

ADC交织的详细测试表明,杂散的最大的来源是偏置不匹配。 我们测量了一系列频率的偏置影响,通过仔细的调整,大幅地降低了Fc/4杂散(图5)。对于K波段的应用,21.5GHz的校准得到了非常好的结果。

校准前和校准后系统的K波段性能如图5所示。上面的曲线是默认设置(CalSet0)的结果,下面的曲线是改进的高频校准的结果。通过后者的校准,偏置、增益和相位不匹配都得到了补偿。在整个K波段,系统的SFDR提高了将近15dB,这是一个巨大的进步。

交织校准之后

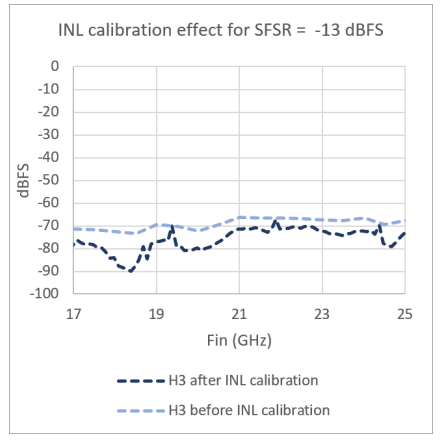

对于某些频点,H2较低而H3变成了主导因素,如图4中21GHz附近的点。在这种情况下,我们需要通过INL的校准进一步降低ADC的杂散。

图 6 - INL校准对H3的影响

虽然进一步提升性能的选项不多,但显然ADC积分非线性(INL)的性能会影响H3。和交织(ILG)类似,产品测试时的INL校准通常是针对基带工作优化的。Teledyne 的测试工程师认为,如果针对高奈奎斯特域重新校准INL,将进一步改善动态性能。

调整INL并不是用户可以通过程序完成的工作,也不应当是。这种调整极具挑战性。从原理上说,提升理想转换器模型的INL有可行且有限的方法。工程师需要搭建测试设备以实现这些调整方法。

通过尽可能降低高频INL,我们把17到25GHz范围里的H3优化了3到5dB(图6)。

INL是什么?对ADC而言,INL量化了器件和理想直线转换函数之间的最大偏差。按照电子器件的精度,转换器全刻度范围的INL期望达到优于0.5LSB。事实上,这对于宽带交织系统而言是不可能实现的。以EV12AQ600为例,全交织模式的INL在Fin=100MHz时是+/-4.5LSB。

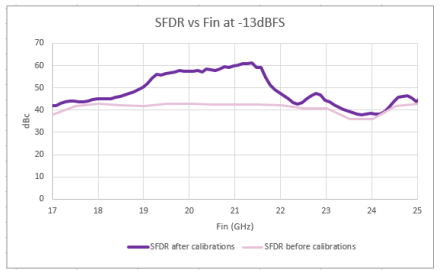

图 7 - 校准前和校准后的K波段SFDR

测试结论

如前所述,这个项目的目的是评估是否可以达到K波段的理想的动态采样性能。更确切地说,我们能否在18到22GHz之间实现最少50dBc的性能?尽管我们在测试的前期遇到一些硬件问题,初始的测试结果也不尽如人意, 但我们最终通过合理的方法大幅提升了性能。最终的曲线(图7)展示了目标输入频率范围内的SFDR性能。可以看出:

• 在19.2到21.5GHz之间SFDR的显著提升(最多提升了15到18dBc)

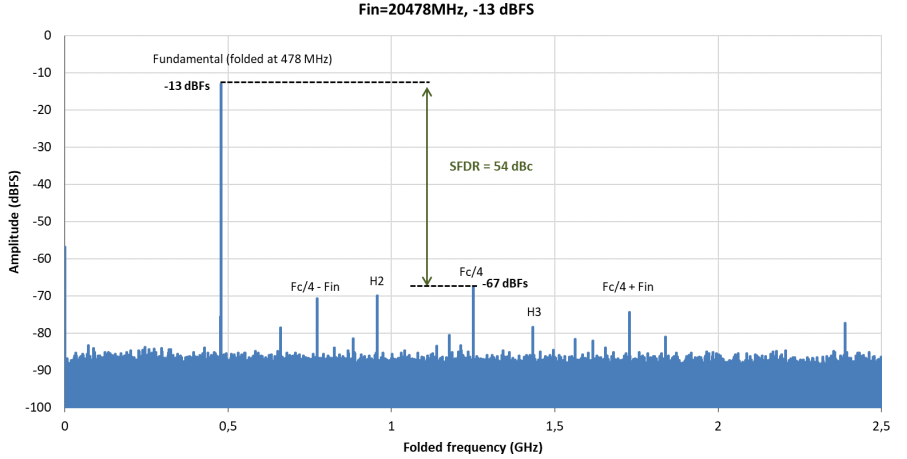

• 在19到21.5GHz之间SFDR超过50dBcFEB上来自20.478GHz下变频的单音信号的频谱特性如下图所示。

图 8 - 实验板FEB的下变频到基带的20.478GHz的频谱

这些结果表明:

• 对于-13dBFS的输入信号功率,在20.478GHz处能达到大约54dBc的SFDR

• Fc/4和相关的杂散依然是影响采样频谱的主要因素(@-67dBFS),其他的杂散(Fc/4±Fin, H2和H3)降低到小于-69dBFS

• 我们已经超过预计的目标,即在19到21.75GHz之间实现最小50dBc的SFDR

未来的展望

上述的结果是从FEB样机上得出的,而FEB样机有一些已知的缺陷。显然,时钟分配的问题可能降低THA的动态性能。我们正在研发一款改进的FEB,预计提供更好的动态性能,并降低H2杂散。另外,这块板子会提供直接的输入并绕过THA,以优化基带性能。预计在2020年,在完成新板子的进一步的测试之后,我们会公布这个实验的后续进展。

这个项目是Teledyne e2v迈向整合的K波段直接采样方案的第一步。除了提供新的能力,这个项目也帮助我们提升了项目的工程经验。这次的工作使我们深入了解了复杂交织模拟数字转换器核心的高频优化问题,特别是高奈奎斯特域校准的折中方案和INL、ILG的优化。Teledyne e2v也提高了其未来高端宽带数据转换器的性能上限。

参考文献:

• 1 Teledyne e2v, “Microwave DAC simplifies direct digital synthesis from DC to 26.5 GHz covering X-, Ku-, and K-bands”, 2016.

• 2 IEEE Webinar: “12-bit 8 GSps DAC enabling signal generation up to K-band”, by R. Pilard. 2019

我要赚赏金

我要赚赏金