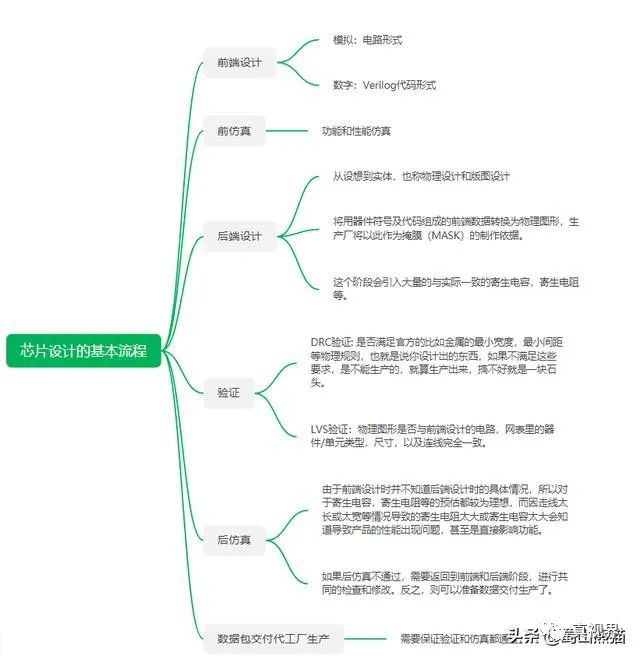

1)EDA的选择做了张脑图,大家先看下芯片的大致流程:

当然实际设计中会更为复杂,并随着制程的变小,会进一步加剧流程各环节的复杂度以及增加环节内部的新的验证项目,但大体还是以下步骤:前端设计和仿真——后端设计及验证——后仿真——signoff检查——数据交付代工厂(以gds的形式)

稍微解释一下几个重要概念:Signoff, 中文翻译叫签核,比较抽象,简单说就是按厂家的默认设置要求做最后一次的规则验证,通常我们在设计的时候,会将厂家要求的标准提高一些来做。后端设计:可以理解为将电路从器件符号形式转为几何图形形式,以指导掩膜版的设计。

然后,我把设计流程里各个环节能用且好用的软件列一下(可以看到基本都是Cadence, Synopsys, Mentor三家的产品):

模拟及混合信号类(包括模拟前端设计及仿真,模拟后端设计及验证,芯片后仿真):电路及版图设计工具:Virtuoso (Cadence), 0.18um,0.35um等老工艺可以用L-edit.(这个不受限)

版图物理验证工具:Calibre(Mentor),老工艺还能用Assura(Cadence),dracura(Cadence更老,十几年前刚毕业那会儿用过)

版图参数提取工具:Star-RC(synopsys),Calibre XRC(Mentor),QRC(Cadence)

电路仿真工具:Hspice(Synopsys) ,Spectre(Cadence), ALPS

数字及SOC类(数字前端,数字后端,验证,仿真):

RTL综合工具 :DC(Design compiler,Synopsys)

仿真验证工具:VCS(Synopsys), ModelSim(Mentor),Incisive,Indago, MDV,VIP(Cadence)

数字后端设计工具:ICC(Synopsys),Innovus/Encounter(Cadence) 还有180nm制程可用的老掉牙的Astro( synopsys).

DFT工具:DFT Compiler (Synopsys)

物理验证工具:ICV(Synopsys)PVS(Cadence), Calibre(Mentor)

signoff 时序/噪声/功耗分析工具:Prime time, PT(synopsys),PrimeRail(Synopsys) ,redhawk Fusion(Synopsys, 这套flow产品的核心redhawk是ansys的产品,ansys为s家战略合作),Totem(Ansys, 美国)

PCB:

Allegro(Cadence) :这个还好,不更新也没太大个问题。

这里再简单说下国内的EDA情况,反向提图抄袭软件其实是走在世界前列的,芯X景(据说还要上市圈钱),客户除了早就被拉黑的外,都不敢说用了他家产品,怕吃官司,这种不值得提倡,因为他们干的事早已超出了他们所宣称的只用于合理学习的底线;

正向设计里目前真正得到认可的只有华大九天(我为他们点个赞),但主要是模拟产品上,具体的说是模拟电路的仿真工具(ALPS),再细化下是电源类产品的仿真上,有他们的独到及NB之处,他们也有对标 virtuoso的兼容性产品Aether,但是得在成熟工艺下用。国内的EDA依然处于一个辅助角色状态,还有很长很长的路要走。

可以这么说,世界上所有的芯片设计公司,不管你是5nm还是350nm吧,无论你多NB,多逆天,肯定采用了这三家的至少一种软件,哪怕是盗版 。

2)设计平台化产品闭环

Synopsys和Cadence一贯的发展战略是平台性发展,也就是说并不是某个环节的设计软件强,而是从前端设计-前仿真/验证-后端设计-后端验证仿真直到流片的整套产品都很强,并形成设计的闭环,比如synopsys的Milkway, Cadence的OA(OpenAccess)。

粗略的说,模拟/数模混合芯片设计用cadence平台,数字芯片设计采用synopsys平台,当然实际并非如此绝对,有一定的交叉使用情况。。对于客户来讲,他们自然会倾向于平台化的EDA的采购,而不是分门别类的买,因为省事就意味着省钱啊,除非你的某项产品极其NB,

比如Mentor的功能或物理验证产品,Ansys家的功耗分析软件,那确实厉害,尤其是物理验证C,S两家真干不过,已经是全球所有代工厂公认的金标准,也迫于垄断压力收不了,那只能战略合作。

3)与工艺厂的捆绑 (EDA联盟+IP联盟)

然后呢,EDA的垄断还体现在于工艺厂的捆绑上,工艺厂早期要进行工艺研发,势必也要进行器件,简单功能芯片的设计,要设计就得基于eda设计平台支持,这时候Synopsys, Cadence等EDA公司就来送温暖了,他们甚至会免费直接帮你设计多种基础IP, 各种规模的功能IP以扩充你的IP库,IP库越大越全,对客户的吸引力也就越大,win-win;

在功能验证,物理验证环节,则有Mentor的一席之地,物理验证会贯穿并频繁往返于后端设计的全流程,对于软件的效率和可视化要求很高,这点calibre做得非常好。另外EDA供应商还会给学校客户优惠价甚至免费,其目的也很明显,培养用户习惯,除非学校也是光荣的上了美帝黑名单。

也就是:EDA 工具+IP授权的捆绑。

这样一整,进入投产阶段后,工艺厂发给客户的PDK设计包自然也只能支持 Synopsys, Cadence,Mentor的了,其他的EDA替代品,多在兼容性上做功,并且无法提供平台化产品,加上兼容和原生,在时效及使用上都有很大的差异。

一旦做强了还面临着Cadence,Synopsys的收购/绞杀威胁。还是那句话,人家提供的是平台,除非你能像Mentor那样提供整套验证平台也可。

共6条

1/1 1 跳转至页

EDA辅助设计的那些事

关键词: 辅助设计 那些 设计

共6条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |