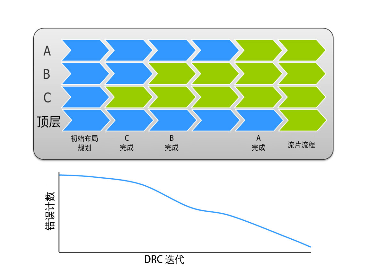

鉴于先进工艺设计的规模和复杂性,而且各方为抢先将产品推向市场而不断竞争,片上系统(SoC) 设计团队没有时间等到所有芯片模块都全部完成后才开始组装芯片。因此,SoC 设计人员通常会在模块开发的同时开始芯片集成工作,以便在设计周期的早期捕获并纠正任何布线违规,从而帮助缩短至关重要的上市时间。错误在早期阶段更容易修复,而且对版图没有重大影响,设计人员在此阶段消除错误,可以减少实现流片所需的设计规则检查 (DRC) 迭代次数(图 1)。

图 1:识别和解决芯片集成问题与模块开发并行进行,可最大程度地减少整个设计实现流程中的 DRC 迭代次数。

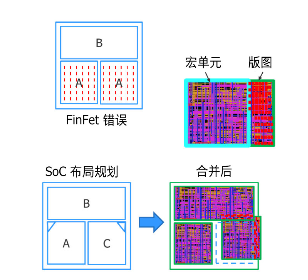

但是,早期阶段芯片级物理验证面临许多挑战。通常,在布局规划的早期阶段,未完成模块中报告的违规数量非常多,导致此现象的原因是许多系统性问题可能广泛分布在整个设计中。系统性问题的典型例子包括:SoC 级别的模块布局偏离网格、SoC MACRO 封装外发生IP 合并、保留布线层上发生 IP 布线、时钟网络上的过孔类型不正确,以及 SoC 中 IP 布局方向不匹配,如图 2 所示。在这个阶段区分模块级违规和顶层布线违规并非易事。

图 2:系统性错误常常导致早期芯片级验证中出现大量违规。

对初始 DRC 运行使用晶圆代工厂规则集中的默认设置,通常会导致运行时间非常长,还会报告非常多的违规,并产生极其庞大的结果数据库,所有这些都使得调试极其困难且耗时。

在此早期阶段,SoC 设计人员的目标通常是最大限度地减少每次 DRC 迭代的运行时间,并且仅关注此时相关的违规情况。除了将模块违规与需要调试的布线违规区分开来之外,SoC 设计人员还可以将模块违规送回模块所有者进行调试和更正。从早期的布局规划到最终的产品流片,SoC 设计人员的终极目标是发现并修复 SoC 系统性问题。

我要赚赏金

我要赚赏金