声学相机是一种将空间视频信息与声场测量信息结合并可视化显示的技术,主要由传感器阵列、数据采集系统、数据处理系统三部分组成,广泛应用于战略军工、工业降噪、无损检测等领域。目前,德国CAE公司Bionic112Array系列声学相机拥有112个传声器阵元、24bit的分辨率以及48kHz的采样率,实现了距离大于0。2m远场声源的二维成像;丹麦B&K也研制出了30阵元的便捷式声学相机PULSEReflex系列。国内,其高科技基于32通道的优化曲面阵推出了高性能的KeyVES-U系列,实现了对300kHz~12kHz声源的定位成像,并通过PXI总线完成数据的传输。

声学相机对采集系统的自噪声非常敏感,并且需要同步地获取大量传声器接收到的声学信号,以及实现大带宽下的数据传输,因此一款高性能的声学相机就对采集系统的采样精度、本底噪声、通道数量等性能指标提出了较高的要求。本文针对这一问题设计了一款基于FPGA控制的数据采集模块,解决了不同声学相机所需通道数不同的难题,满足对不同种类传声器阵元的信号进行数据采集的需求,并且论述了该模块的整体设计过程与扩展性分析,通过实际测试给出了采集模块性能指标。

1硬件设计

1.1总体架构设计

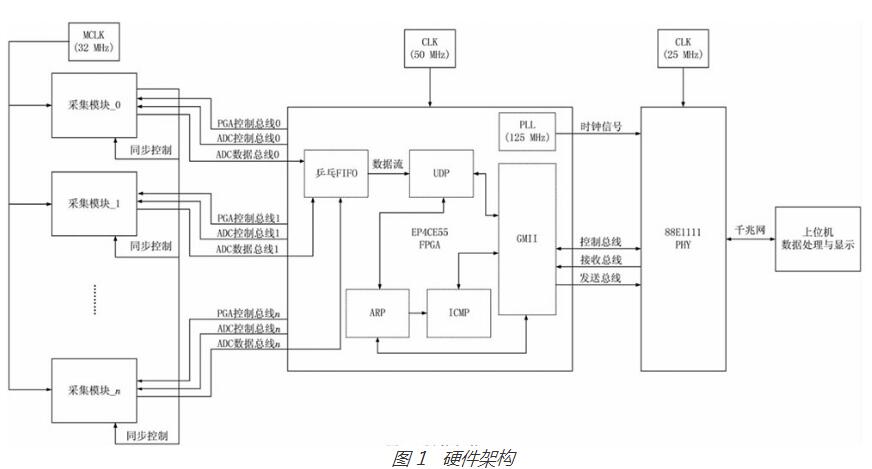

随着半导体工艺的发展,FPGA的性能和容量在逐年地提升,其价格和功耗却持续降低,越来越多嵌入式仪器仪表的开发都采用了FPGA作为最优解决方案。本次设计的采集系统主要由FPGA、采集模块组以及千兆以太网通信三部分构成,如图1所示。

图1硬件架构

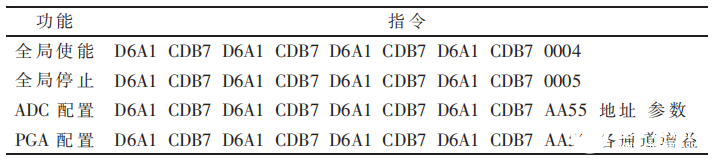

上位机通过千兆以太网发送的命令帧格式如表1

表1命令帧格式

所示,数据传输的帧格式如图2所示。

图2数据帧格式

1.2采集模块设计

1.2.1器件的选型

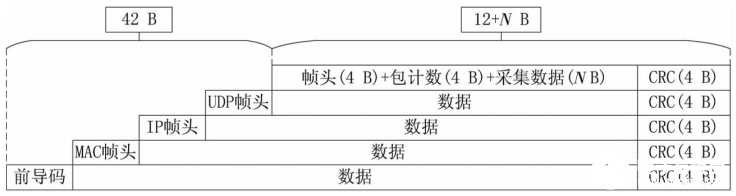

采集模块中ADC芯片的选取需要考虑其转换类型、量程、分辨率、采样率、通道数、动态范围、输入输出接口等参数,表2列举了工程中常见的几款ADC芯片的性能指标,本次设计择优选择了ADI公司推出的AD7768芯片。

表2ADC芯片性能指标

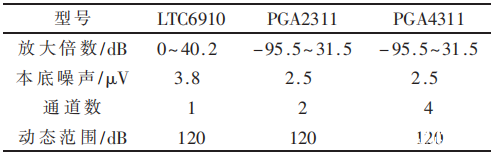

由于传声器的输出电压信号通常是毫伏级别,其远远小于ADC芯片的量程范围,因此,需要对输入的电压信号进行放大处理,选取PGA芯片作为整个采集系统的输入级,使得采集模块的输入阻抗大于1GΩ,并且通过改变PGA的增益系数可灵活匹配不同种类传声器的信号放大需求。表3列举了几款常见的PGA芯片性能指标,择优选择了TI公司推出的PGA4311芯片,通过LTC6363芯片将PGA输出的电压信号完成单端转差分的操作,以匹配了AD7768芯片的差分输入接口。

表3PGA芯片性能指标

1.2.2可扩展性分析

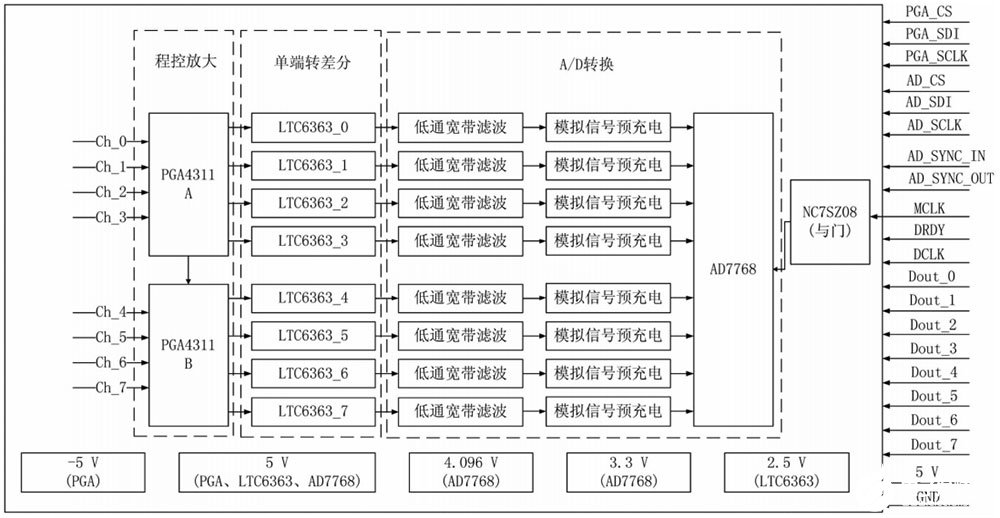

图3模块硬件构成

采集模块硬件构成如图3所示,总共消耗FPGA的I/O资源数为16个。由图2可知,单个采集模块每个网络包占用42B固定包头、4B的帧头、4B的包计数以及4B的CRC校验,单个模块1次采样有32B数据,上位机要求一个数据报中包含M个采集模块N次同步采样的数据,则发送个包的时间T为:

T=(54+MN×32)/125(1)

设采样频率为fs,则采集系统实现连续数据传输需要满足的条件为:

T《N/fs(2)

EP4CE55型FPGA拥有的用户I/O数量为374个,即M还需满足:

16M《374(3)

通过硬件上增添采集模块,并根据式(2)和式(3)调整AD采样率fs以及单次发送的采集点数N即可实现通道数可调的功能。例如,fs设置为125kHz,128通道同步采集(M=16),一个数据报中包含8次采集数据(N=8),可以求得发送时间T=33。2μs,缓存N次的时间为64μs,消耗I/O数量256个,满足了通道数扩展的条件。

2软件设计与实现

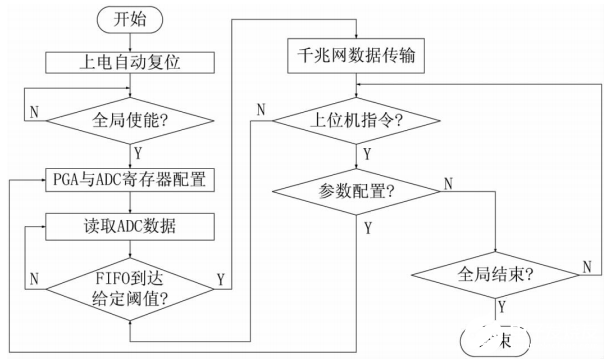

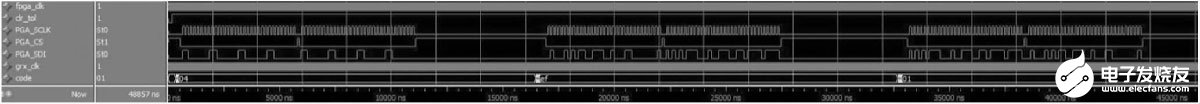

程序流程图如图4所示,程序上实现了上位机与FPGA之间的千兆以太网通信、FPGA对上位机指令的响应与校验以及采集数据高速缓存与实时上传。

图4程序流程图

2.1指令校验模块设计

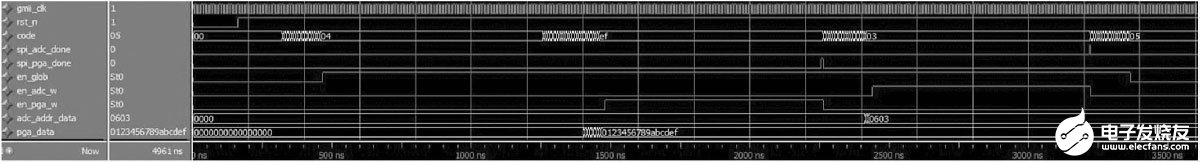

图5校验模块逻辑波形

FPGA通过同步于以太网时钟信号上升沿对数据总线进行连续地判断,该模块的逻辑仿真波形如图5所示,实现功能如下:

(1))识别出上位机的全局启动指令,并将全局使能信号(en_glob)置“1”,随后,当接收到全局停止指令后,清零全局使能信号;

(2))识别出上位机的PGA配置指令,将PGA的配置使能信号(en_pga_w)置“1”,并寄存配置信息到寄存器“pga_data”中,当PGA配置完成后将使能信号置“0”;

(3))识别出上位机的ADC寄存器配置指令,置“1”ADC的配置使能信号(en_adc_w)后寄存配置信息到寄存器“adc_addr_data”中,当ADC配置完成后清零使能信号。

2.2PGA控制模块

PGA4311芯片通过SPI接口实现与FPGA芯片的数据交互。对级联的PGA芯片进行配置时,需要对第一片PGA连续进行两次增益系数的配置,PGA通道寄存器输入的数据L(1~255十进制)与实际增益系数K的关系如式(4)所示:

K(dB)=31.5-[0。5×(255-N)](4)

PGA控制模块实现的功能如下:

(1))当采集系统接收到上位机发出的全局使能指令时,对所有通道写入十六进制数“C0”,实现下位机的默认配置功能;

(2))当系统识别到上位机发送的在线修改指令时,将指定参数写入PGA芯片,并返回等待指令状态。

如图6的逻辑仿真图所示,首先,全局使能后通过两次SPI通信完成了8个通道增益系数的默认配置,随后,分别实现了两次在线修改各通道增益寄存器的操作。

图6PGA配置模块逻辑波形

2.3ADC控制模块

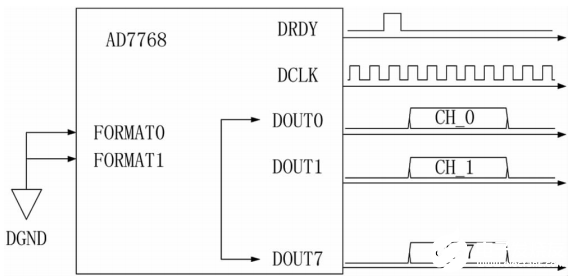

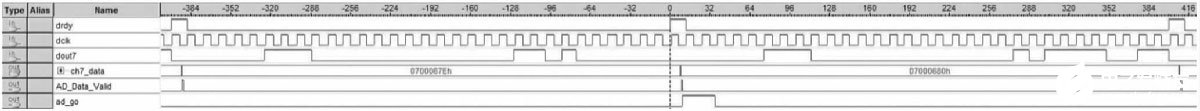

AD7768芯片的数据输出形式如图7所示,其中“DRDY”信号的频率代表了ADC的采样率,FPGA根据每个“DCLK”的下降沿对“DOUT”进行读取。

图7通道并行数据输出模式

图8为系统工作在125kHz采样率下,FPGA读取单个采集模块ADC通道7数据的实际逻辑波形图,其中“AD_Data_Valid”信号作为FIFO的写时钟信号,另外,“ad_go”为后级以太网传输的发送使能脉冲。

图8数据读取波形

2.4千兆以太网控制模块

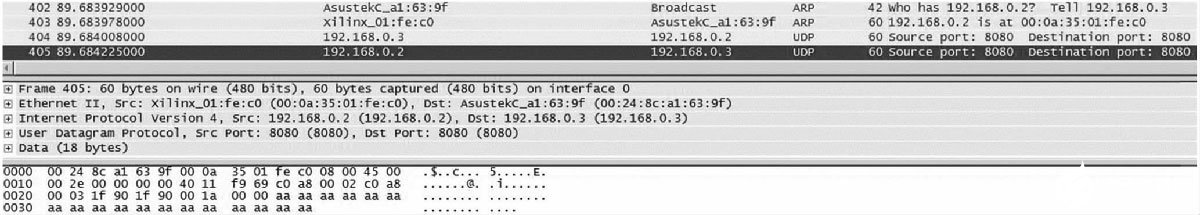

千兆以太网控制模块的主要功能如下:

(1))ARP协议获取并缓存上位机的MAC地址与IP地址;

(2))UDP协议实现指令回馈与数据传输功能;

(3))通过ICMP协议实时观测网络连接是否畅通。

上位机发送18B的“AA”对采集系统进行网络抓包测试,ARP应答与指令响应功能如图9所示;上位机通过DOS系统,输入ping指令对ICMP协议进行测试,其结果如图10所示。

图9ARP与UDP协议的实现

我要赚赏金

我要赚赏金