近几年基于MPEC-2的DVB普通数字电视在美国、南美、亚洲、大洋洲和非洲通过卫星进行广播。基于MPEG-2/DVB的多路节目复用器是数字电视传输系统的关键设备之一,因此,它的研发显得尤为重要。目前,复用器的设计方案主要基于DSP(数字信号处理器)的实现技术,这种设计方法在理论上也能实现对传送流的复用,考虑到实现复用器诸多高速、复杂的逻辑功能,同时,FPGA(现场可编程门阵列)理论上可以无限次地重新配置,这样在一定程度上为系统的升级或局部功能的改进留下了余地。所以,从今后专用芯片的设计和开发的角度来讲,基于FPGA的设计无疑是最佳的选择。本文提出了一套基于FPGA的复用器输入部分的设计方案。

1 复用器组成

整个传送流的复用器分为复用预处理、输入和复用3部分。预处理部分是对多路传送流的PSI(节目特殊信息)提取并修改,重新生成新的PSI表的过程;输入部分是给各路经预处理的不同速率的传送流提供缓存,并将半满信号发送给后续的复用模块;复用部分是将n路传送流复合成一路传送流的过程,控制对各路传送流进行选择性发送,适时插入空包和其他业务信息。复用器的数据缓存包括输入FIFO和输出FIFO,它为n路传送流提供缓存,便于复用器随时提取某一路传送包进行处理。因此,复用器FIFO是否具有高速性和可靠性将直接影响复用器的性能。

2 FIFO设计方案

2.1 异步FIFO结构

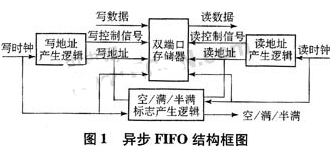

首先,由于输入通道和输出通道的时钟频率不同,所以用来实现输入接口的FIFO必须支持异步读写功能,其结构如图1所示。

其次,考虑到输入通道和输出通道的时钟频率相差很大,为了避免数据溢出,FIFO的大小设计也需要考虑。FIFO的大小一方面与输入传送流的码率和路数有关;另一方面,FPGA的处理能力也是影响缓冲器的一个因素。本设计中充分考虑了满足产生半满信号和节省系统资源的要求,FIFO的参考长度设计为一帧传送流长度的2倍,即为376 B。n路传送流以不相关的码流速度写入FIFO中,由于时钟之间周期和相位完全独立,因而数据的丢失概率不为O,如何设计一个高可靠性、高速的异步FIFO电路便成为一个难点。

由图1可以看出,FIFO的存储介质为一块双端口RAM,可以同时进行读写操作。在写时钟域部分,由写地址产生逻辑产生写控制信号和写地址;读时钟部分由读地址产生逻辑产生读控制信号和读地址。在空/满/半满标志产生部分,当FIFO里的数据超过188个字节时,产生一个半满信号,并将该信号送给复用控制模块,由复用控制模块产生一个读使能,控制FIFO读出数据。也就是说写过程是连续的,而对于一个FIFO来说读过程是间断的。

2.2 异步时钟同步电路

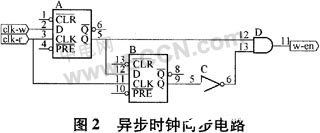

设计的过程中,首先要同步异步信号,使触发器不产生亚稳态。采取的方法是以读时钟为基准时钟控制读写数据,由读时钟触发,将写时钟变为写使能来控制FIFO写入数据。如图2所示的触发器电路可以同步异步时钟。

由图2可以看出clk-r和clk-w分别是读时钟和写时钟,两者异步且频率相差很大。通过两级D触发器对这两个时钟进行同步,把写时钟clk-w转变为一个由读时钟clk-r上升沿触发的写使能w-en,由w-en控制写入数据。

2.3 信号控制电路

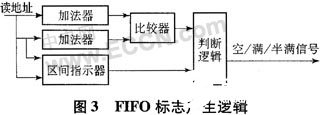

同步了读、写时钟后,下一个问题就是如何正确设计空/满/半满信号的控制电路。这些标志的产生是FIFO的核心部分,如何正确设计此部分的逻辑,直接影响到FIFO的性能。MPEG-2/DVB的传送流复用的特殊性,决定着空/满/半满标志产生的原则。FIFO的标志产生逻辑如图3所示。

系统定义了写指针wp和读指针rp,在FIFO写入或者读出数据时开始记数。通过比较wp与rp来产生标志信号。具体实现方法是:定义一个计数器(count)对存人FIFO的数据字节数计数,产生半满信号hf-flag,当FIFO写入一个数据时,计数器加“1”,当从FIFO中读取一个数据时,计数器减“1”,当计数器值大于187时,该FIFO输出一个半满信号。另外,附加了一个并行的区间判断逻辑来控制同步字节的写入。当同步字节syn到来时,写指针wp开始计数,FIFO开始写入数据,这时需要同步判断计数器的值,而这个值应为0或187,从而给wp赋初值,这保证了FTFO中写入的前4个字节即为传送包的包头。与此同时,半满计数器也在计数,当其值大于187时,半满信号HF跳变为1,表明FIFO接收到读使能r-en时,读指针rp开始计数,系统开始从FIFO中依次读取数据,读取完1帧(188 B)数据后,读使能关闭,系统不再读取数据,此时hf-flag也变为0,FIFO的状态又回到了初始状态。

2.4 缓存功能模块

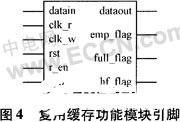

图4给出了FIFO的引脚定义:syn为传送流同步字节;rst为复位信号;clk-r为读时钟;r-en为读使能信号,当系统执行读操作时,该信号为“1”,clk-w为写时钟;datain为并行8位数据输人;hf-flag为半满信号,当FIFO中数据个数大于187时,该引脚输出一个高电平;emp-flag为空标志;full-flag为满标志;dataout为并行8位数据输出。

3 结束语

本文基于FPGA的复用器输入部分设计方案,程序调试简单,通过实践验证,运行效果良好,达到了设计的要求,具有较高的实用价值。

我要赚赏金

我要赚赏金