众所周知,电磁兼容的3要素是电磁干扰源、被干扰对象和传播电磁干扰的途径。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见而又非常重要的辐射源。尽管时钟信号与其他数据信号、控制信号的逻辑电平一般都是一样的,翻转速率一般也没有太大的差别(大多数总线数据率与时钟信号翻转速率之比是1:1或者1:2),但由于时钟信号之所以更容易接近或者超过辐射****的限值,主要原因是时钟信号是比较严格的周期信号,其在频域的能量主要集中在某些频点上,而数据信号是非周期信号,在频域上的能量也是比较分散的。因此,良好的时钟电路设计是PCB板的电磁兼容设计的关键。

1时钟信号的频谱

根据傅里叶展开可以得到,一个幅度为A,周期为T,脉冲宽度为t0,上升下降时间为tr的梯形时钟波形,其在n次谐波处的谐波分量为:

式中C(n)为n次谐波处的谐波分量,单位:V或dBμV。

从上面梯形时钟波形的傅里叶级数可以看出,影响时钟信号辐射强度的因素有时钟波形的幅度A、占空比(t0+tr)/T、时钟周期T(或者时钟频率f)、以及时钟波形的上升时间和下降时间。其中时钟信号的幅度与其产生的干扰直接线性相关,上升时间和下降时间对时钟高次谐波的影响至关重要。

2时钟频谱的影响因素

2.1时钟上升时间对辐射的影响

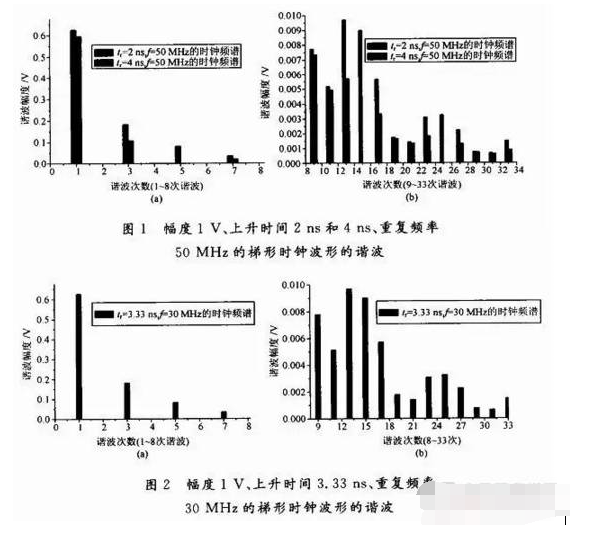

假设有2个时钟信号,幅度都为1V,频率都为50MHz,上升时间分别为2ns和4ns。根据上面的傅里叶变换可以得到2个时钟信号的频谱分布,如图1所示。

2.2时钟频率对辐射的影响

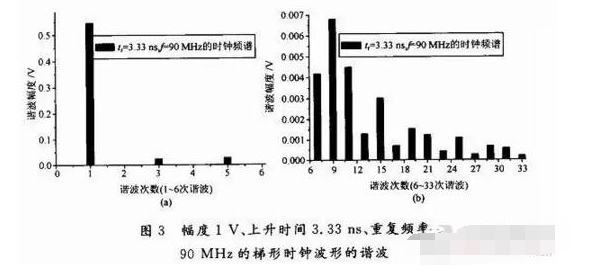

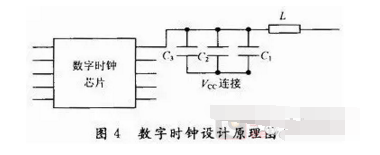

假设有2个时钟信号,幅度都为1V,上升时间都为3.33ns,重复频率为30MHz和90MHz,根据上面的傅里叶变换可以得到2个时钟信号的频谱分布,如图2和图3所示。

2.3时钟频谱的比较

从图1可以看出,时钟谐波干扰尤其是高次谐波干扰的强度会随着上升和下降时间的降低而大大加强,2ns上升时问的时钟的高次谐波比4ns上升时间的对应谐波高出1~2倍。

当上升下降时间相同时,周期T(或者基频f)的高低对时钟产生的高次谐波干扰的影响非常大,图2和图3分别是重复频率30MHz和90MHz,上升时间都为3.33ns,幅度为1V的梯形时钟波谐波干扰的大小。从图中可以看出,2种时钟在270MHz的谐波干扰,90MHz时钟在270MHz(3次谐波)的谐波干扰比30MHz时钟在270MHz(9次谐波)的谐波干扰高出15dB左右;再比较90MHz时钟在810MHz(9次谐波)的谐波干扰比30MHz时钟在810MHz(27次谐波)的谐波干扰高出12dB左右。

因此在进行时钟系统设计时,在条件允许的情况下优先选用较低的时钟频率,比如在设计以太网的PHY芯片时既有采用125MHz外部时钟的也有采用25MHz外部时钟的,如果在其他技术条件允许应优先选用外部时钟为25MHz的芯片,而且在各方面技术条件都满足的情况下优先选择上升和下降时间比较长的时钟或者时钟驱动电路。

3时钟电路的电磁兼容设计

在PCB板上实现时钟电路的电磁兼容设计主要从下面的几个方面来考虑:时钟晶振及其驱动器的电源处理;在PCB板上晶振及其驱动器的下面做局部的覆铜处理;时钟信号线的布线;时钟信号的端接和滤波等。

3.1电源设计

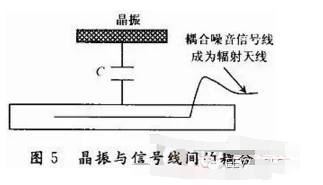

当时钟电路的输出同时发生状态变换时,会对电源系统产生较大的瞬态电流,或灌电流,为了避免时钟芯片对单板电源系统的冲击,抑制单板电源的电磁干扰,就需要对时钟电源部分进行滤波和隔离设计。其设计原理图如图4所示。

3.2铺铜及布线设计

晶体振荡器内部的电路会产生射频电流,如果晶体是金属外壳封装的,直流电源脚是直流电压参考和晶体内部射频电流回路参考的依据。不同的晶体(CMOS,TTL,ECL等)内部产生的射频电流对金属外壳的辐射大小不同,如果晶体金属外壳不与大的地平面连接,则不能将晶体金属外壳上大的瞬态电流泻放到地平面上。

在晶振和时钟电路下面的局部地平面可以为晶振及相关电路内部产生的共模RF电流提供通路,从而使RF****最小。为了承受流到局部地平面的共模RF电流,需要将局部地平面与系统中的其他地平面多点相连。即表层的局部地平面与系统内部地平面相连的过孔提供了到地的低阻抗。同时要注意的是要保证晶振底下地平面的完整性。使用完整地平面的信号的回流和信号本身方向相反,大小相等,能够很好的互相抵消,可以保证其良好的信号完整性和电磁兼容特性。但是,如果地平面不完整,回流路径中的电流与信号本身的电流不能相互抵消时(尽管这种电流不平衡有时候是不可避免的),就会产生一部分共模电流。产生的共模电压就会激励连接的外围结构,造成较大的辐射。

如果布线从晶振下面穿过,特别是传输到连接器的布线,不仅破坏局部地平面的作用,而且还会将晶振产生的噪声通过容性耦合的方式耦合到穿过它下面的信号线,使这些信号线带有共模电压噪声,如果这些信号线通过连接器又延伸出PCB,就会将噪声带出。这是一种典型的共模辐射问题,原理如图5所示。

3.3端接设计

时钟驱动芯片不用的输出管脚,比如:空载(开路),由于管脚开路全反射可能会引起时钟高次谐波的电磁干扰问题。在单板上加备用端接是解决这个问题的一种方案,但是备用端接采用电阻还是电容或者其他的端接方式时主要看空载所引起的电磁干扰的频点。如果采用电阻端接,就要考虑由此带来的功耗和驱动器的驱动电流;如果采用电容端接,可能会增加某些其他频点的电磁干扰,因此电容的大小时要优化电容值;如果不用管脚没有端接,但是已经通过试验证明了电磁干扰有足够的裕度,就没必要对未用管脚进行额外的备用端接处理。

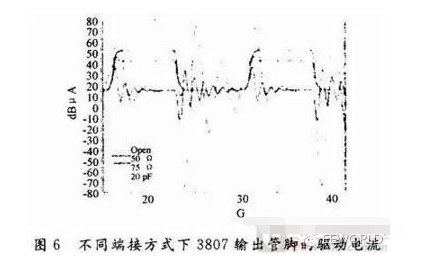

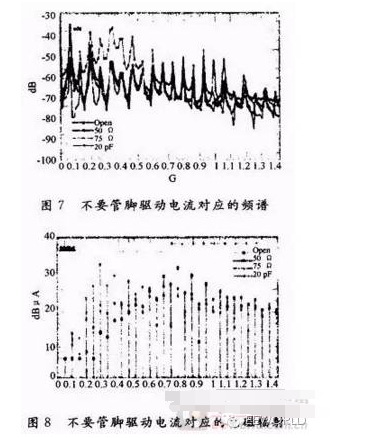

下面以3807数字时钟芯片为例,用仿真试验的结果来解释备用端接的作用。图6~图8表示了芯片不用的输出管脚时在开路、接50Ω对地电阻、接75Ω对地电阻、接20pF对地电容等方式时,驱动脚的电流、频谱分布及驱动电流所产生的电磁辐射。

从上面的结果可以看出:

(1)开路时的驱动电流最小,但有明显的窄脉宽振铃。就说明如果驱动器不用管脚空载(开路),驱动器的功耗最小。但是由此会带来一个不利的方面,那就是驱动电流的频谱中高频分量会变大,有可能导致高频的电磁干扰问题。这一点通过图7和图8中的开路驱动电流的频谱和电磁干扰曲线(蓝色曲线)也可以得到验证。

(2)如果驱动器不用管脚用电阻端接,驱动电流会变大,但是驱动电流中的振铃现象明显减弱。采用小电阻端接,可以改善驱动电流的振铃,但是会增加驱动电流,功耗变大;如果采用大电阻端接,可以减小驱动电流,但是会使得驱动电流出现振铃现象(开路是电阻端接的一个极限)。通过仿真结果看,选择75欧姆端接电阻一方面可以使得驱动电流不会很大,另一方面驱动电流的振铃也不是很明显。

(3)如果驱动器不用管脚采用电容端接,驱动电流的峰值变大,同时驱动电流脉冲的宽度也变大。这就表示驱动电流中的低频分量会明显变大,这就要注意低频段谐波的电磁干扰问题。图7和图8中对应电容端接的驱动电流的频谱曲线和电磁干扰曲线的低频分量明显变大也验证了这个问题。

4结语

本文主要就对如何降低时钟(干扰源)的干扰进行了分析和总结,因此可以得出以下如何切断时钟干扰的传播途径的结论。一是将时钟电路的基波和谐波能量最大程度的约束到指定的范围之内(这些能量传输需要的电路包围的面积越小越好);其二是有效建立时钟电路区域与输入输出接口线路的隔离。由此可以在时钟电路设计时可以通过布局和布线来达到优化电磁兼容设计的目的。

我要赚赏金

我要赚赏金