Vivado提出了UFDM(UltraFastDesignMethodology)设计方法学,其核心思想是尽可能在设计初期发现潜在问题并解决。毕竟,越是在后期发现问题,越难发现关键问题,解决起来越费力,甚至会出现牵一发而动全身的被动局面。这是因为在Implementation阶段,Vivado在每个子步骤或多或少都会做一些优化,这些优化可能会掩盖一些问题。那么就时序收敛而言,在综合之后要分析什么呢?

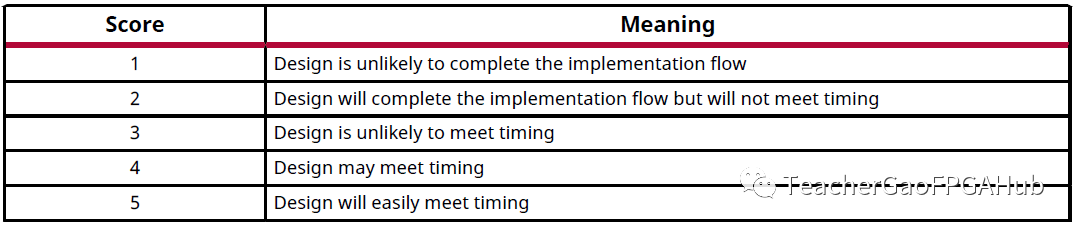

首先,很明确的是在综合之后就要着手对设计进行分析,需要分析逻辑级数、资源利用率、时钟拓扑结构、时钟资源利用率和控制集,此外,还要分析BRAM/URAM/DSP的使用是不是最优的(例如,是否使用输出寄存器或者级联寄存器等),这些要素都会影响设计时序。这里重点要说的是Vivado提供的一个很好的命令report_qor_assessment。该命令可对设计进行整体的评估,并给出一个分数,以表征时序收敛问题的严重程度。Xilinx建议最好在综合后就开始执行此命令。具体分数及其含义如下表所示(表格来源:Table5,ug949)。

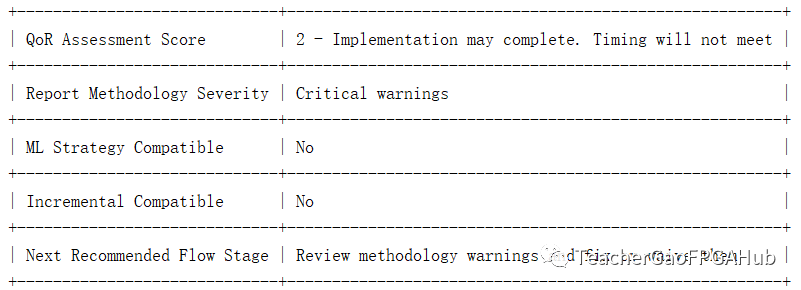

这个命令使用方法很简单,只要打开综合后的设计,在VivadoTclConsole中输入report_qor_assessment回车即可。生成的报告第一部分如下图所示,可以看到第一行就是评分结果。如果这个分数是1/2/3,那么基本上可以不用执行后续流程,时序很难收敛,此时要把精力放在综合阶段所发现的问题上。

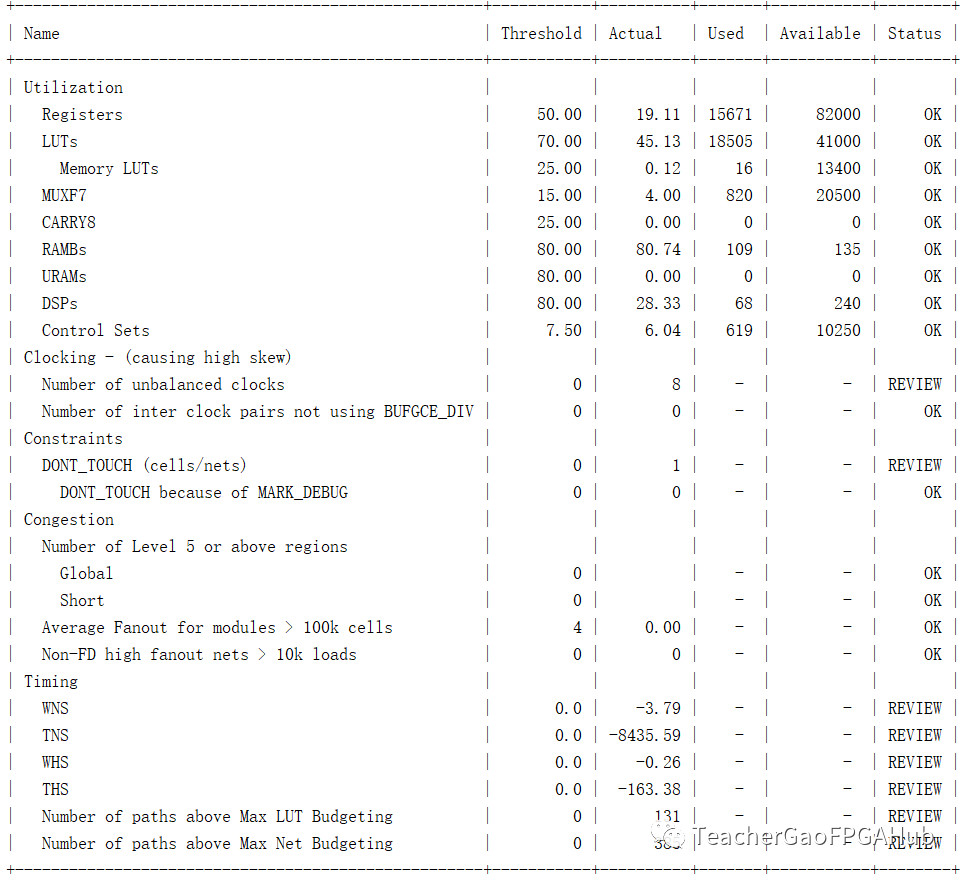

这个命令的第二部分是关键部分,如下图所示。一方面给出了资源利用率,重要的是给出了资源利用率的真实值和指导值,一旦超过指导值,Status一栏会显示为REVIEW。超过指导值不是不可以接受,而是会很大程度上给时序收敛带来麻烦。另一方面,该报告也会分析逻辑级数、控制集、拥塞和扇出等。凡是Status标记为REVIEW的,需要格外关注,可接着用相应的命令进一步分析。例如,这里发现unbalancedclock,那么可以用report_clock_networks再进一步分析。

由此可见,分析的过程是先运行report_qor_assessment,再从中发现Status为REVIEW的条目,接着用相应的命令进一步分析。这会提高分析的效率,做到有的放矢。

我要赚赏金

我要赚赏金