今天收到了活动邮寄来的罗姆SiC MOSFET半桥评估板,下图为外包装,很大一盒。

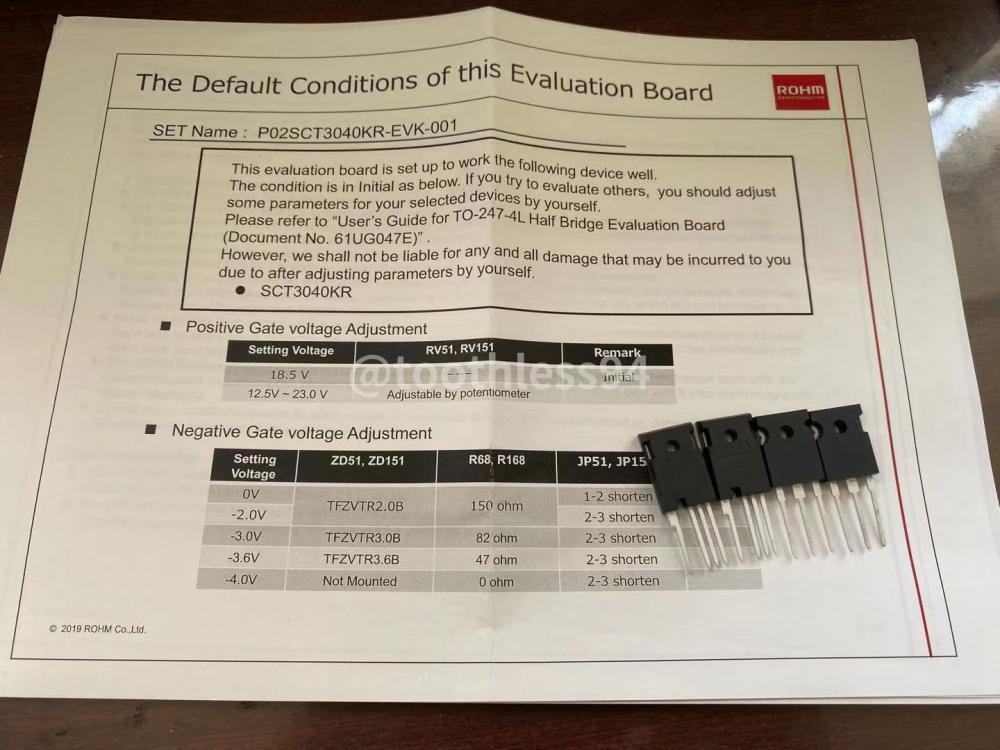

第二张图为开箱后图片,里面有静电袋包装的评估板、4片SiC MOSFET以及纸质说明书一份。

今天来细看下评估板~

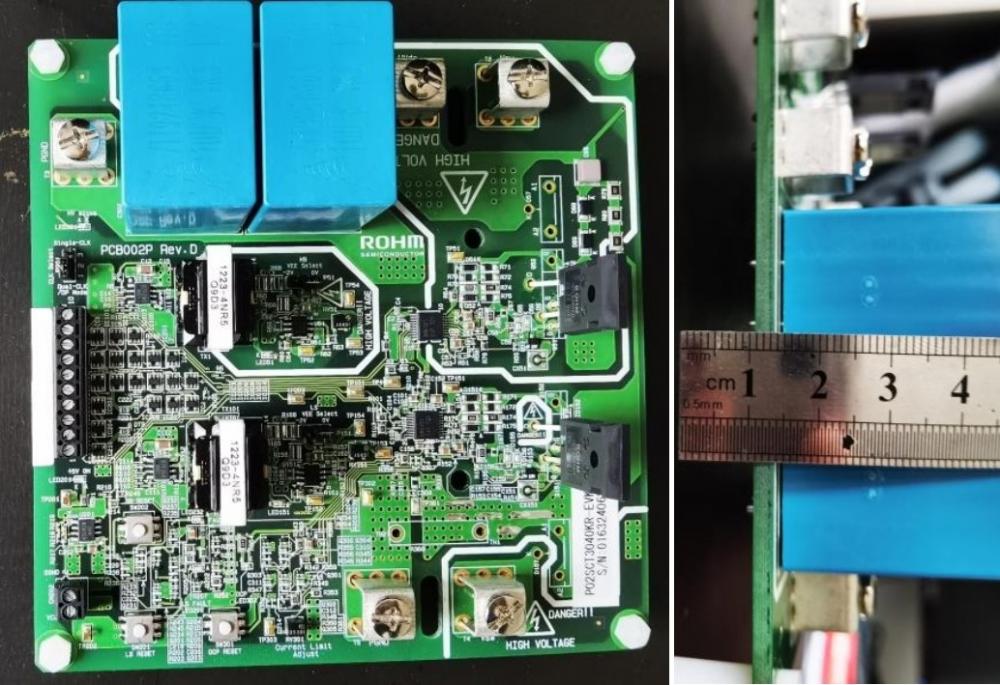

评估板的做工非常棒,驱动电路部分占据了一大部分,由于SiC MOSFET的驱动电压与Si MOSFET的不同,每个厂家不同型号的SiC MOSFET驱动电压也有差别,因此该评估板的驱动电压是在一定范围可调的。蓝色的应该为直流侧的滤波电容,从接线端口可以看出,该板子的功率不小。通过查询网站可以发现,P02SCT3040KR-EVK-001板子的最大支持电压为800V,并设置有过流保护。

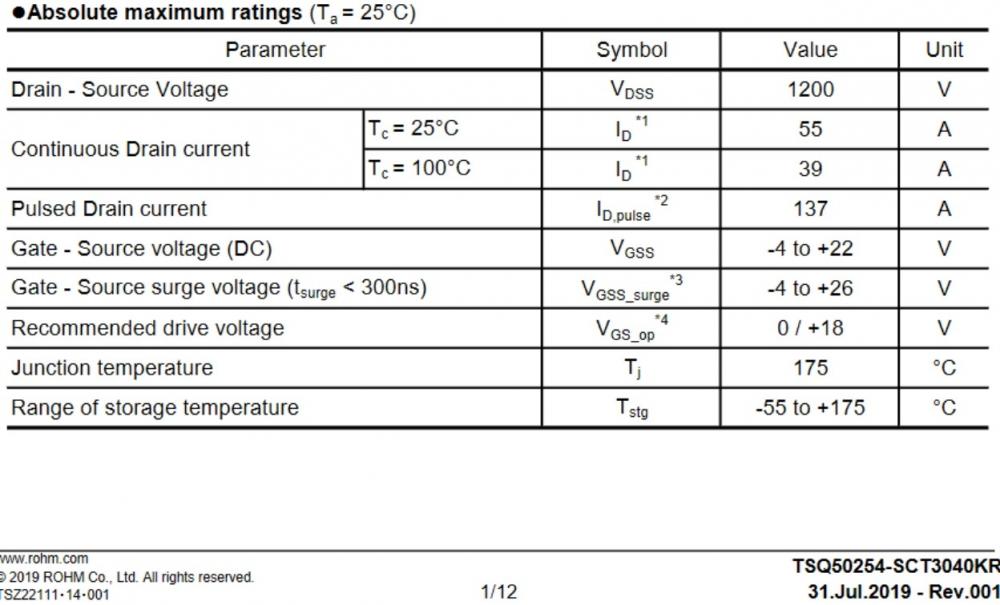

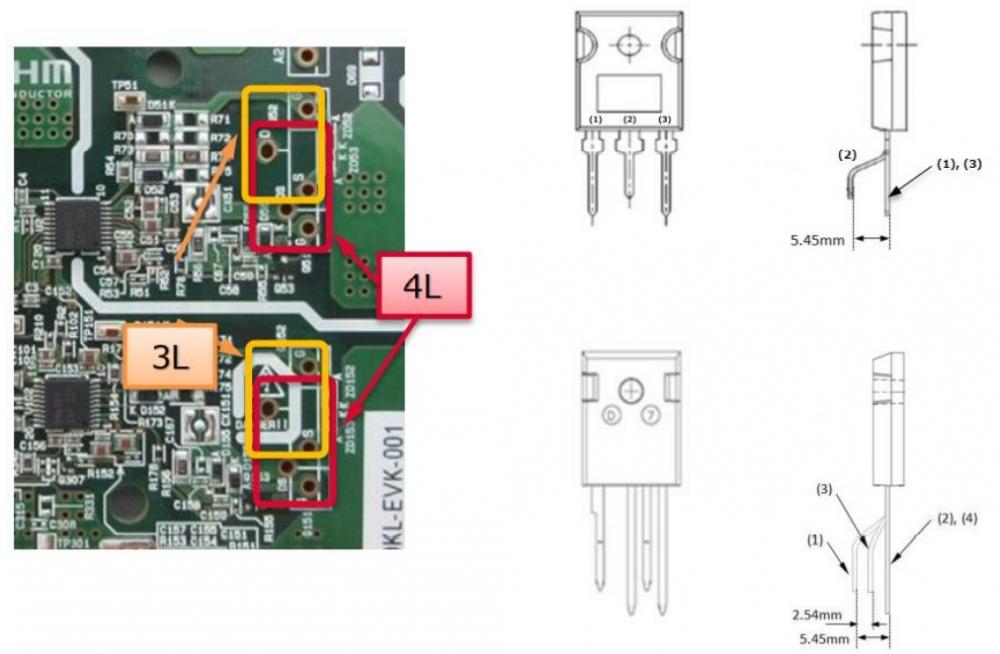

该评估板兼容市面上常见的3引脚和4引脚TO-247封装的SiC MOSFET。赠送的4只SiC MOSFET分立器件型号为罗姆的SCT3040KR和SCT3040KL,其参数为1200V/55A。

下图为盒内的纸质说明书,可以从官网下载对应的英文操作手册。

下图为3引脚SiC MOSFET的安装效果,引脚需要适当分开,注意管子的栅极引脚G的序号为1号(正面左数第1)。焊接好两个SiC MOSFET后,利用该评估板构成的半桥电路就可以方便的进行测试与评估了。

更新

感谢ROHM公司提供的P02SCT3040KR-EVK-001评估板,有幸参与评估板的测试。拿到评估板的第一感觉就是扎实,评估板四层PCB的板子厚度达到了30mm;高压区域也有明显的标识。

随箱附赠了四颗SiC MOSFET,分别是TO247-3封装的SCT3040KL和TO247-4封装的SCT3040KR,器件都是1200V、55A的管子,驱动电压可以达到22V和-4V,推荐驱动电压是18V和0V,这个相比于现有的需要负压关断的SiC而言,可以简化电源结构,好评。

由于SiC MOSFET的导通关断时间会相对较短,因为采用开尔文源极的封装,可以消除功率电流回路对驱动回路的干扰,减小振荡,降低驱动损耗。对于提升SiC MOSFET的可靠性。该套评估板在设计时候提供了两类封装的安装位置,方便比较两类封装的差别。

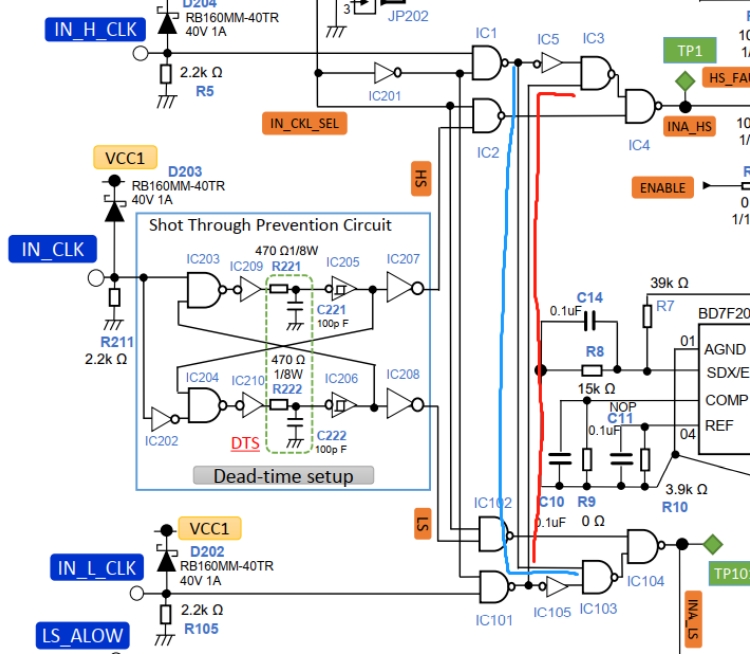

首先看一下控制信号的逻辑关系,该评估板提供了两种信号控制方式,Single-CLK和Dual/DP-CLK两种输入,利用JP201接线端进行选择。

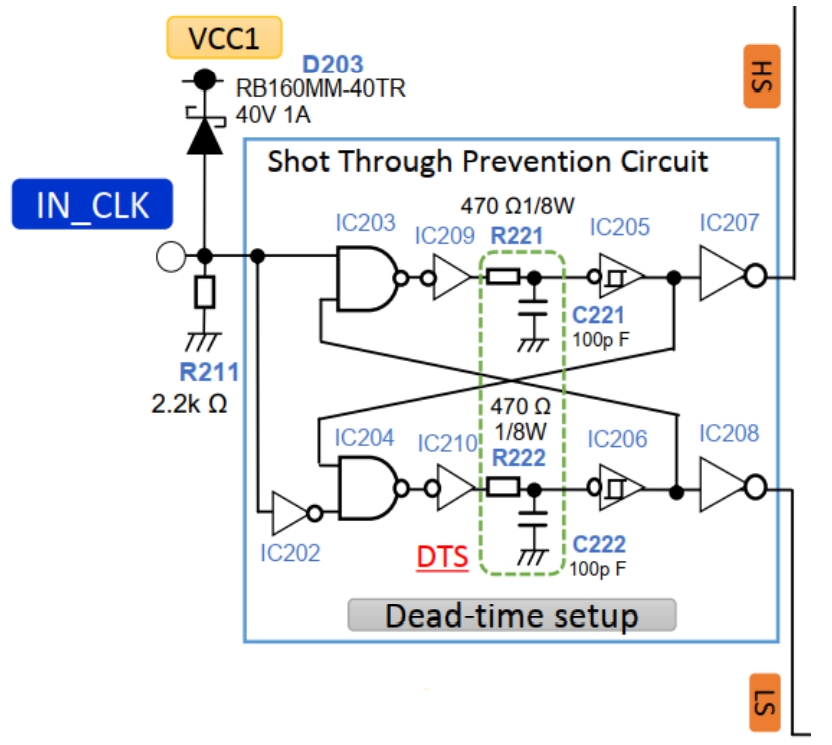

Single-CLK模式是,仅需要将EMABLE引脚使能,给IN_CLK输入驱动信号即可,通过图中的逻辑转换生成HS和LS的驱动信号,而且通过加入RC电路实现延迟触发,提供驱动信号的死区时间。

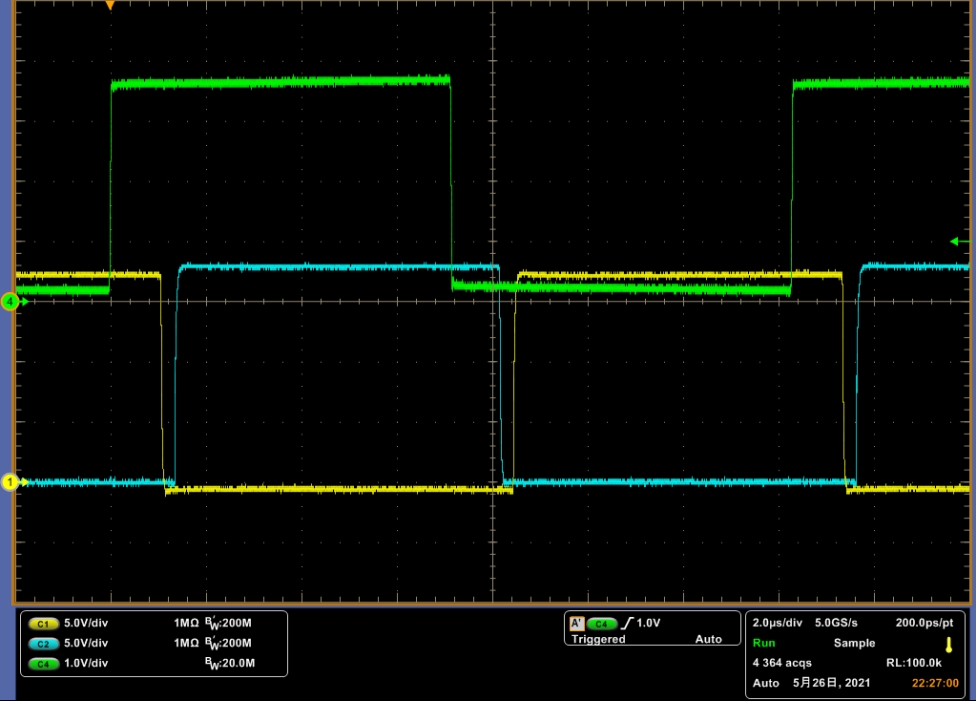

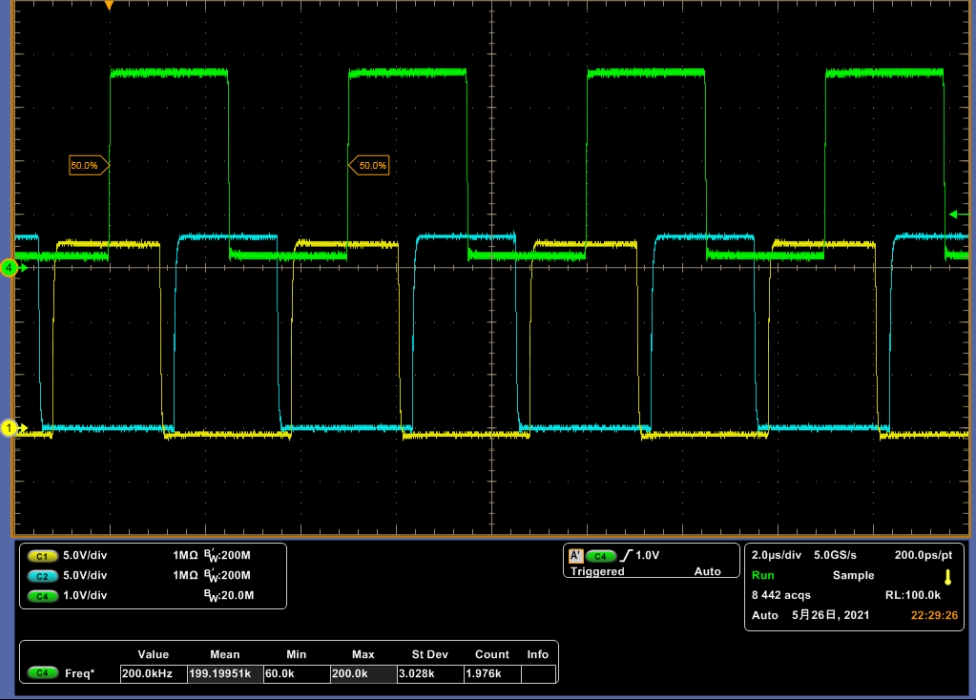

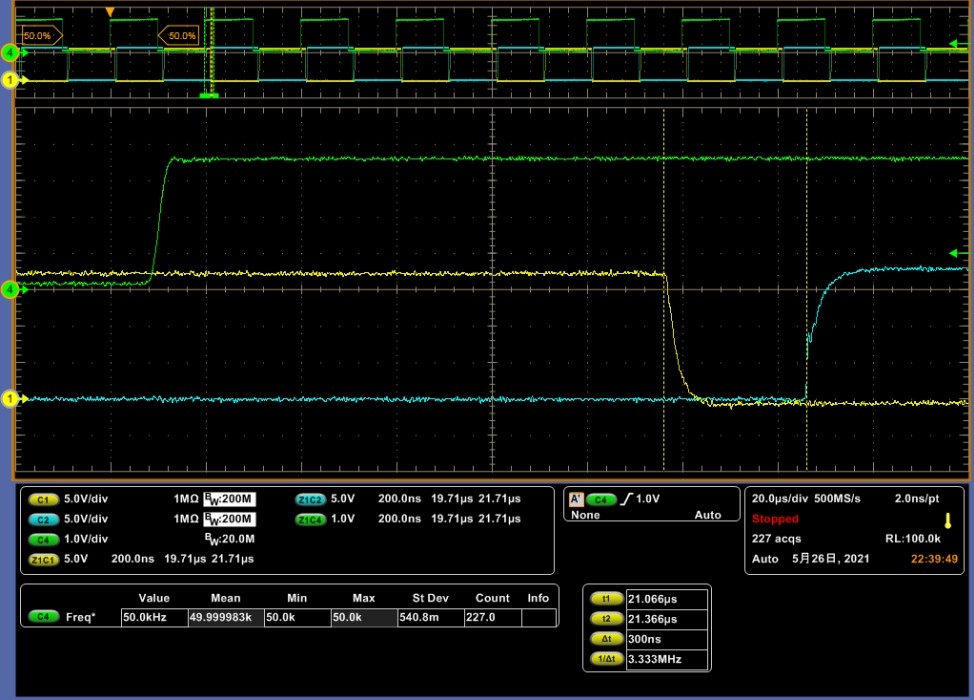

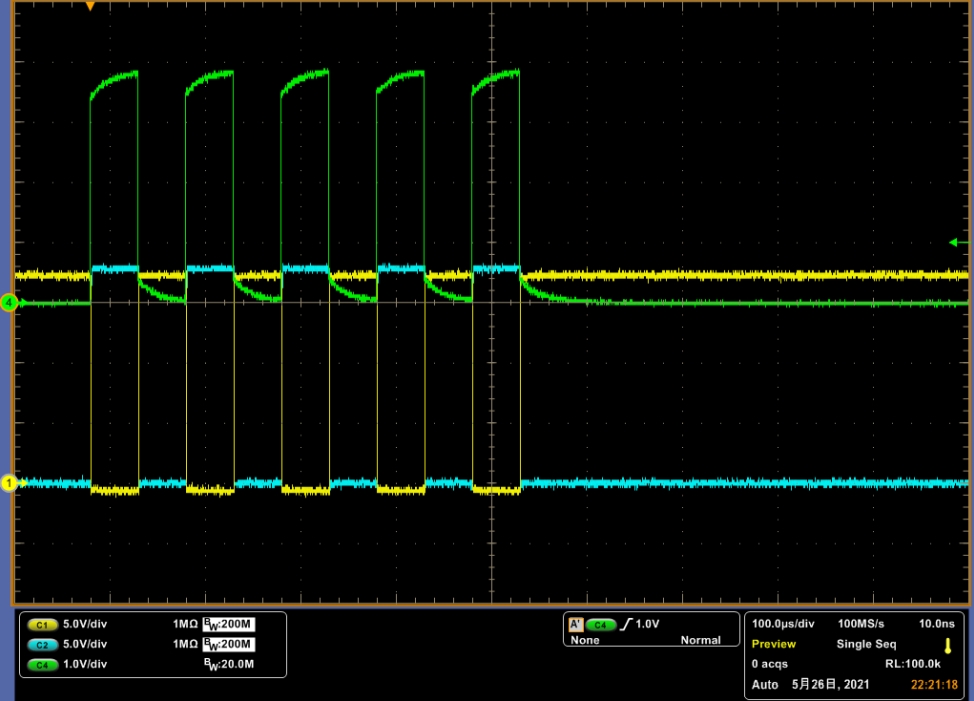

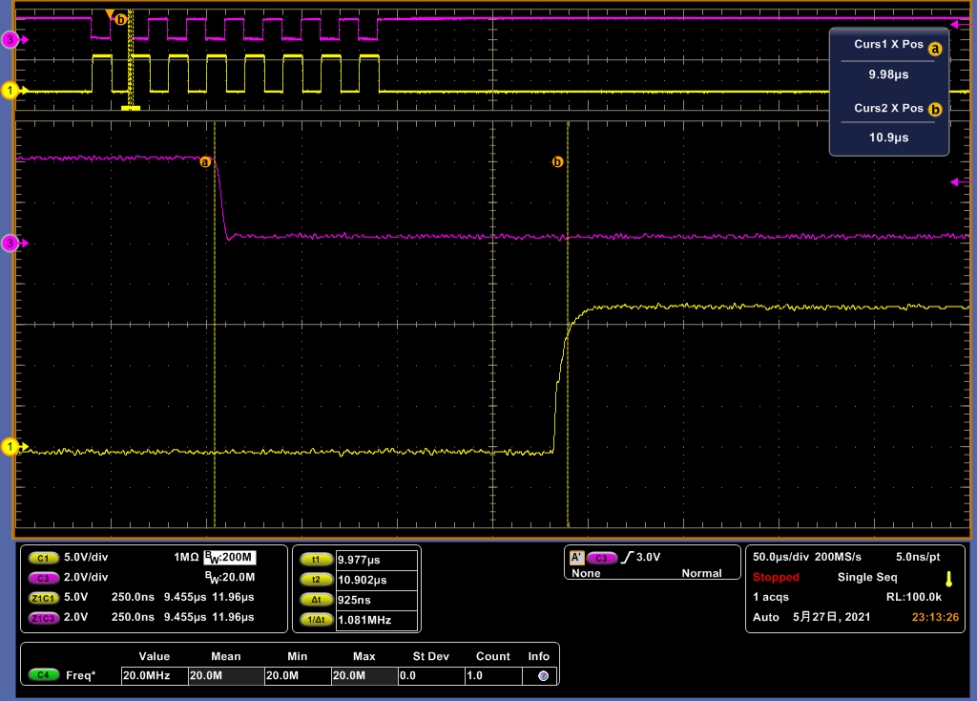

下图为Single-CLK模式下的驱动电压测试波形。其中Ch1:Vgs_LS,Ch2:Vgs_HS,Ch4:IN_CLK。测试频率从20kHz测试到200kHz,驱动信号上升沿到驱动电压Vgs_HS的上升沿时间间隔为1.7μs。

Single-CLK的出厂的死区时间大约为300ns。

此外实际测试中也发现,在采用Single-CLK的控制模式,由于HS和LS是经过延迟触发生成的,所以在INCLK没有信号输入时,LS的驱动电压是一直导通的状态。

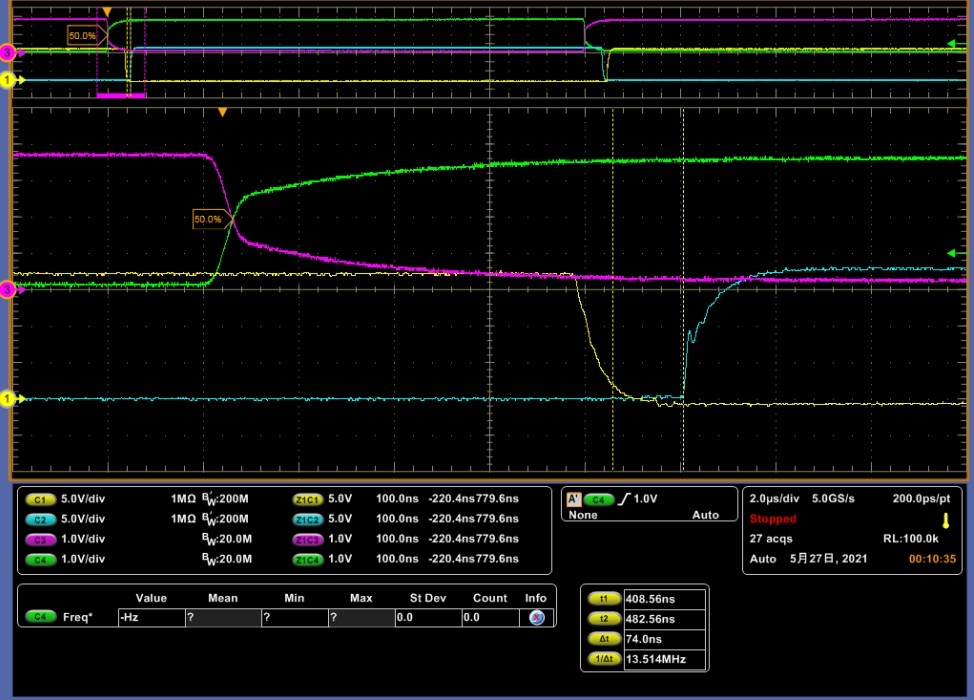

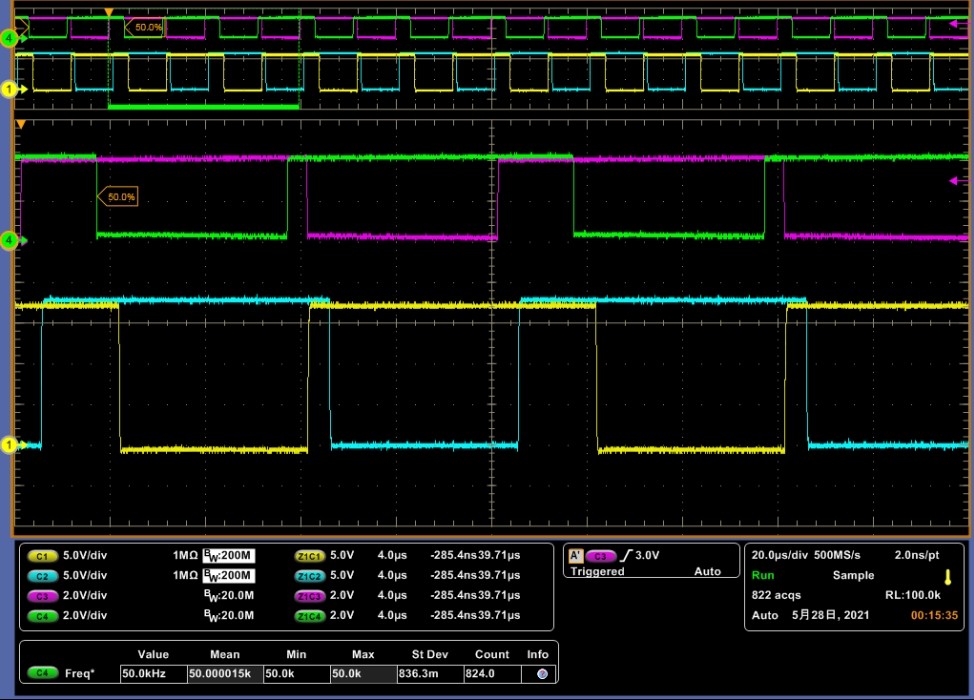

下面测试一下,Dual/DP-CLK模式的信号输入。在使用Dual/DP-CLK模式下,需要通过H(L)S_ALOW和IN_H(L)_CLK共同控制,在手册中的描述为:

所以,这里可以使用两种控制模式,一是ALOW直接默认下拉,IN_H_CLK输入高电平,HS导通,相当于正逻辑控制;另一种是ALOW接到”H”电平,IN_H_CLK在低电平时HS导通,此时IN_H_CLK相当于反逻辑控制。

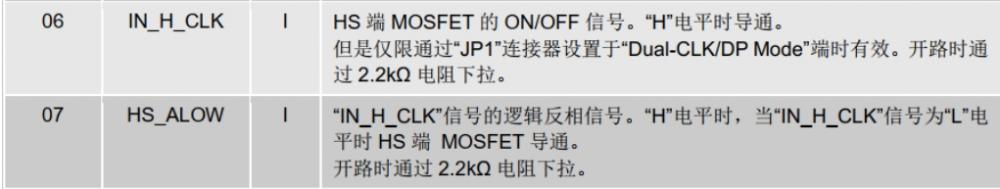

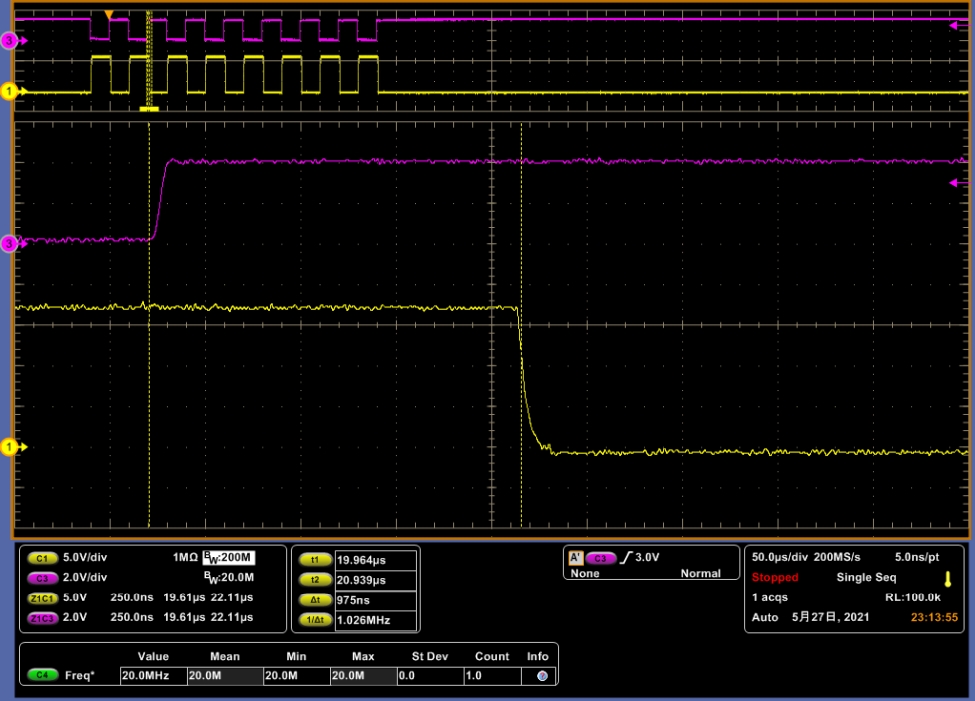

下图是ALOW下拉,IN_H(L)_CLK输入驱动信号后的输出驱动电压。其中Ch1:Vgs_LS,Ch2:Vgs_HS,Ch3:IN_L_CLK,Ch4:IN_H_CLK。

看了一下信号延迟,在直接用IN_H(L)_CLK输入驱动信号下,传输延迟时间在400ns左右。

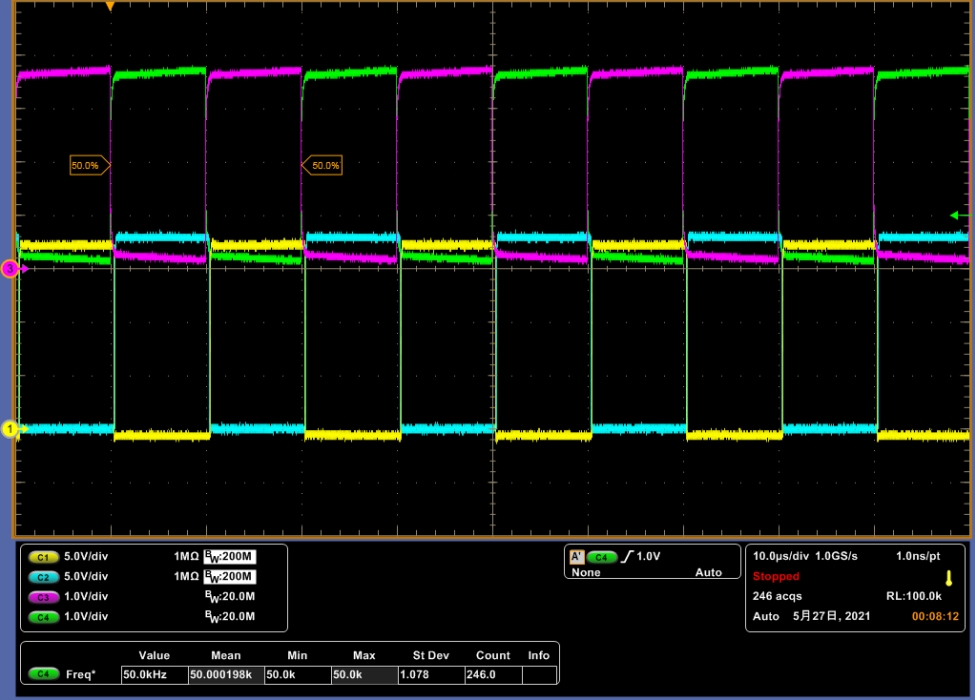

下面是才采用反逻辑的驱动测试,这也是手册推荐在做双脉冲采用的控制方式。Ch1:Vgs_LS,Ch3:IN_L_CLK。开通和关断过程的传输延迟有所增加,达到近1μs的时间。

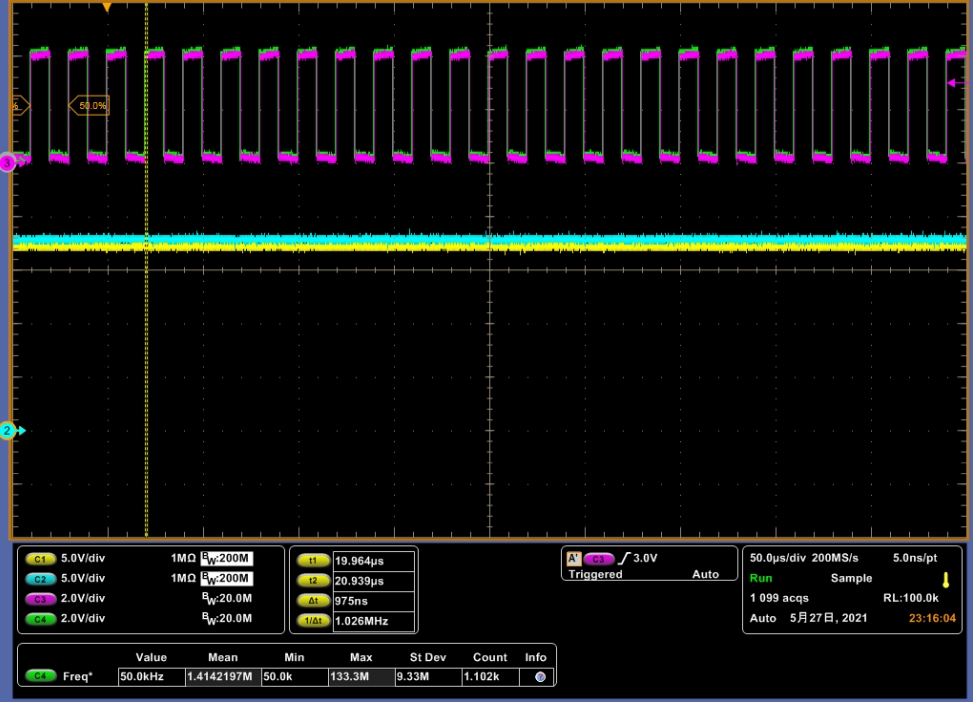

在实际测试的时候发现,如果采用这种ALOW和IN_H(L)_CLK的驱动逻辑,会存在上下桥臂直通的现象。包括IN_H_CLK和IN_L_CLK的输入信号一致、IN_H_CLK和IN_L_CLK存在信号重叠部分时,都会导致半桥桥臂直通的现象。

针对上面的问题,查看了一下驱动信号的逻辑控制电路,发现在产生给后级驱动芯片BM6101FV-CE2的INA引脚的INA_HS和INS_LS的信号是经过多次与非运算得到的,其信号逻辑是 和 ,所以在输入信号完全一致相同时,会导致INA引脚信号直接的拉低,因此Dual/DP-CLK模式只适合单器件工作控制。

因为时间较为仓促,只进行了先相关驱动电路的测试,后续也将针对ROHM的SiC MOSFET器件性能和评估板的运行保护功能做更为详尽的测试。非常感谢ROHM公司提供的P02SCT3040KR-EVK-001评估板,为后续应用SiC MOSFET器件进行产品设计,提供参考和设计经验,让我们对SiC MOSFET器件的性能有了更为直观的体验。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |