也许在电子领域中能够排在 欧姆定律[2] 之后,处于老二地位的就得 摩尔定律[3] 了:芯片中可以集成的晶体管每经过两年左右就会增加一倍。既然芯片的物理尺寸大体保持不变,那么就意味着单个晶体管随着时间就要变得更小。我们习惯于看到新一代芯片中的特征尺寸稳定持续变得更小,但这种小究竟意味着什么呢?是否小就等同于好呢?

在过去的一个世纪中,电子技术得到了飞速发展。在1920年,当时最好的中波收音机内包含有多个中真空管、很多体积硕大的电感、电容以及电阻,几十米长的电线作为接收天线,用于供电的电池组的体积占据了很大的空间。

如今,可以收听十几个电台的收音机可以轻松装在你的口袋里,辅助的功能也极其丰富。但尺寸的减小并不仅仅为了便于携带:而是实现我们期望高性能的关键因素。

元器件尺寸的减小的最为明显的好处就是可以在同样体积内实现更多的功能,这对于数字电路尤其关键:更多的元器件,使得你可以在相同的时间内做更多的事情。比如一个64位的处理器,理论上可以在同样的时钟频率下完成8位处理器的八倍的信息处理,为实现这一点,它也同样需要八倍的电子元件:包括寄存器、累加器、总线宽度以及其他部件都会有八倍数量的提升。所以你需要有一个八倍尺寸的芯片,或者组成电路的元器件的尺寸小八倍。

对于存储器也是相同的:更小的电子元器件可以在相同的体积存储更多的信息。现在的显示器的像素是由薄膜三极管制作,所以减少器件的尺寸可以提高显示器的分辨率。然而除此之外还有更加关键优势来自于更小的晶体管,那就是它们的性能也随着体积的减小而的更显著的提高。这是为啥呢?

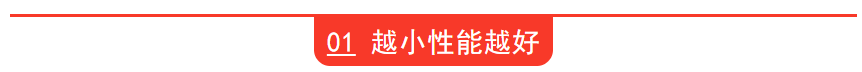

你制作一个三极管的同时还免费得到一些附加的器件。在每个三极管引脚都会有电阻。然后流过电流的通路都会有寄生电感。任何两个相对的导体之间也会有寄生电容。这些寄生元器件会消耗更多的电能,减缓晶体管运行速度。寄生电容对速度的影响最为重要:在晶体管开关状态过程中,都会引起寄生电容的充放电,这都需要时间和消耗电源电流。

两个导体之间的寄生电容与它们的体积相关:小的尺寸意味着寄生电容更小。更小的寄生电容则意味着更快的运行速度和更低的电能消耗,所以更小的晶体管可以运行在更高的时钟频率,同时所消耗的电能也越小。

降低晶体管的尺寸不仅仅减少了寄生电容,一些怪异的量子现象也会涌现,这在大尺寸晶体管中并不明显。通常小的晶体管可以运行更快,但除了三极管之外,还有其他器件影响电路的运行,当其他器件体积减小时,情况会变的怎样?

一般情况下,一些无源器件,比如电阻、电容、电感等,它们并不会因为体积减小而变得更好,反而在某些方面情况变得更糟。减少它们的体积很大原因是为了在更小的空间内放进更多的器件,节省PCB空间。

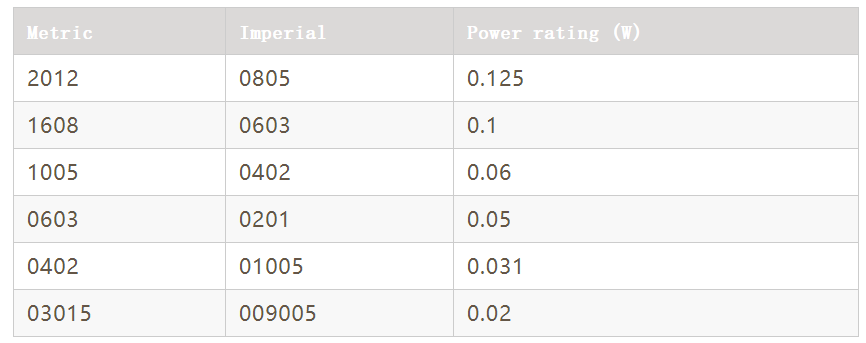

电阻的尺寸减小往往不会到来麻烦。一块物质的电阻是由决定,其中是长度,是横截面积,是材料的电阻率。你可以将电阻的长度和横截面积等比例减小,材料不变,就可以获得相同阻值的电阻。唯一的坏处就是小尺寸的电阻消耗同样的功率,比起大尺寸的电阻所引起的温度的升高更大。下面表格给出了表面封装电阻的最大功耗随着它们的尺寸降低而减小。

现在最小封装的表贴电阻是03015(0.3mm×0.15mm),允许最大功耗仅有20mW,它们只能应用在功耗非常低以及尺寸要求非常苛刻的场合。更小封装的电阻0201(0.2mm×0.1mm)也已上市,但并没有量产,虽然已经出现在供应商产品手册中,但别指望它们派上实际用场。一些自动贴片机器人甚至都无法准确摆动这些微小的电阻,所以现在它们仍属于井中月亮。

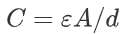

电容的尺寸减少,电容容量也减小,两块平行电极之间的电容容量为: ,其中

,其中 是电容极板面积,

是电容极板面积, 是极板间距离,

是极板间距离, 是绝缘材料的介电常数。你减小了电容尺寸,对应的面积也减小了,所以造成了电容容量降低。如果你还想得到相同nF的电容,你只有将多个小电容堆叠一起来增加容量。幸亏电容材料的改进和工艺的发展,使得极板间距变得更小,材料介电常数增加,这使得过去几十年间,电容的体积变得非常微小了。

是绝缘材料的介电常数。你减小了电容尺寸,对应的面积也减小了,所以造成了电容容量降低。如果你还想得到相同nF的电容,你只有将多个小电容堆叠一起来增加容量。幸亏电容材料的改进和工艺的发展,使得极板间距变得更小,材料介电常数增加,这使得过去几十年间,电容的体积变得非常微小了。

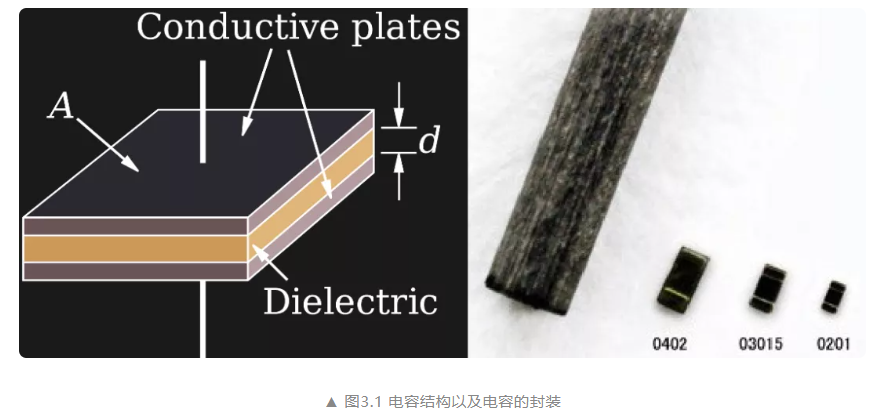

如今的电容封装可以小到0201, 只有0.25mm×0.125mm大小,它们的容量可以达到100nF,耐压最大超过6.3V,这可以满足大多数电路中的要求。同样,微小的体积要求更加精密的自动贴片机械装置,这限制了小型电容的推广使用。

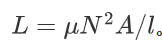

对于电感,减小体积变得棘手。一个线圈的电感为: 。其中N是线圈匝数,A是线圈的横截面积,l是线圈长度,

。其中N是线圈匝数,A是线圈的横截面积,l是线圈长度, 是磁性材料的导磁率。如果你将尺寸都缩减到原来的一半,电感容量也会降低一半。然而线圈的等效串联电阻保持不变:这是因为线圈的横截面积与长度都减小到原来的四分之一,所以电感量减半,电阻不变,电感的品质因数(Q)也减半。现在商用的最小分立电感器件的封装为01005,(0.4mm×0.2mm),对应的电感为56nH,电阻是几个欧姆,早在2014年就宣布上市的0201封装的电感现在连毛都没有见到。

是磁性材料的导磁率。如果你将尺寸都缩减到原来的一半,电感容量也会降低一半。然而线圈的等效串联电阻保持不变:这是因为线圈的横截面积与长度都减小到原来的四分之一,所以电感量减半,电阻不变,电感的品质因数(Q)也减半。现在商用的最小分立电感器件的封装为01005,(0.4mm×0.2mm),对应的电感为56nH,电阻是几个欧姆,早在2014年就宣布上市的0201封装的电感现在连毛都没有见到。

可以在某些石墨烯制作的线圈中观察到动能电感(kinetic inductance)物理现象,这可以形成更加微小的电感。但如果想真正到商用化,这也只能将现有电感体积减小50%。在高频电路中,比如GHz频率范围,几个nH的电感就可以使用了。

还有一个未被人注意到的因素使得推动着几个世纪以来元器件小型化的进程,那就是电路工作频率的提升,对应着信号的波长的减小。早期无线电广播使用中波调幅信号,频率大约1MHz,电磁波长为300米。1960开始,调频广播开始流行,它则使用100MHz,对应的波长为3米。如今我们所使用的4G通讯,使用的1 ~ 2GHz的电磁波,波长之后20厘米。高的频率对应可以传输更多的信息,器件体积降低使得成本下降,可靠性以及功耗都得以改善。

减小波长也可以缩小天线尺寸,这是因为天线尺寸正比于发送和接收电磁波信号的波长。现在的手机不再需要突出的天线得益于它所使用的GHz信号频段,此时天线只需要一个厘米大小。所以现在一些可以接收调频广播的手机仍然需要用户佩戴耳机收听,它需要耳机的引线来作为广播天线来接收电台的电磁信号,它的波长大约3米。

连接天线的电路板,也因为尺寸变小而容易生产。这不仅因为晶体管的速度变快,同样是因为在小体积小信号连线的传输线效应减小,电路中如果引线的长度超过信号波长十分之一的时候,就需要考虑引线传输所带来的信号相位变化的影响。在2.4GHz的电路中,一位置一个厘米长的电路引线就能够影响电路工作,这会使得你将分立器件焊接起来变得令人头痛,但在一个几个毫米见方内使用微小封装器件构成的电路中就不会有太大的影响了。

现在技术杂志中经常反复出现的说法就是摩尔定理的失效,或不断给出这些预测出错的原因。但事实上,半导体中的三巨头,英特尔、三星和台积电仍然在努力将更多的器件压缩进方寸之中,并筹划未来更多芯片改进工艺。虽然比不上20年前改进步伐那么显著,但晶体管尺寸的降低一如既往。

但对于其它分立器件我们好像到了它们的自然极限:尺寸的降低非但不能带了性能的提高,而且也超出了大多数应用场合的需求。

似乎对于分立器件来说,并没有什么摩尔定律,如果有的话,我更愿看到有谁能完成焊接这些标贴器件的挑战。

转帖自网络

我要赚赏金

我要赚赏金