异构计算已经成了半导体业界不得不思考的一个话题,传统通用计算的性能捉襟见肘,过去承诺的每隔一段时间芯片性能翻倍的豪言壮语已经没有人再提了。如今我们用到的手机中,各种除CPU以外的计算单元层出不穷,无论是神经网络处理器还是图像处理器。

异构计算的存在可以说创造了另一个维度,这个维度上我们又有了堆性能的空间,小至手机SoC、汽车芯片,大到服务器芯片和超算处理器,异构带来了更大的算力。但与此同时,异构计算也带来了一些潜在的问题。

异构计算的崛起

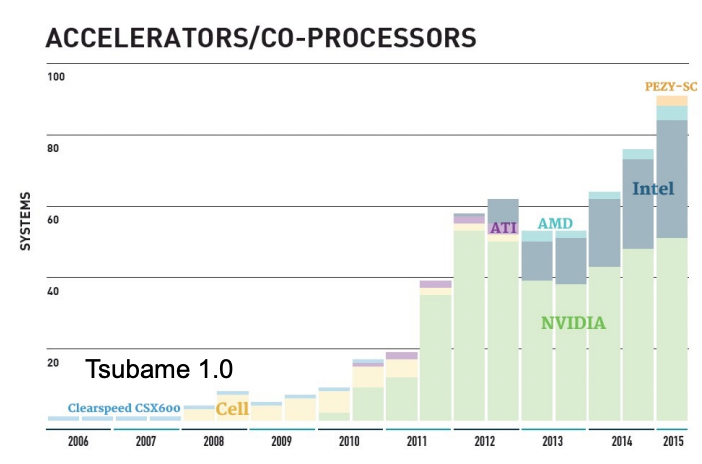

异构计算其实早在计算机时代的早期就开始零星出现了,比如英特尔在80年代推出的浮点协处理器(FPU)i487,Inmos./ST在1996年推出的多媒体加速器Chameleon等等。转眼进入了新世纪,异构出现的频率也越来越高,2010年苹果推出了首个自研的处理器A4,将CPU、GPU和其它加速器集成至一起。在超算领域,加速器和协处理器也数量也在逐步增加。

全球超算系统加速器/协处理器的应用趋势 / TOP500

2020年以后,各国的超级计算机计划都定位在了Exascale的百亿亿级别,要想实现目标,要么靠堆核心规模来堆性能,要么就是选择异构计算。如今前十的超算系统中,有一半以上都采用了CPU+GPU的异构设计。

明眼人都能看出,这种CPU+GPU的异构设计也开始变得愈发紧密,比如英伟达今年宣布的Arm CPU Grace,该处理器靠着英伟达专利互联技术NVLink的加持,成功将CPU与GPU之间的互联速度做到了夸张的900GB/s,是传统PCIe的10倍以上,CPU更是靠LPDDR5X实现了500GB/s的内存带宽。

异构计算真就完美无缺?

异构计算就真的如此完美吗?并非如此。异构计算的存在其实也引出了不少隐患,比如极度差异化的编程模型,从过去的单向编程转为了多向编程。因为异构系统中存在多个计算设备,又有着不同的系统架构、指令集和编程模型,因此异构系统的编程与传统的CPU编程相比有很大的差距。通常来说,异构混合计算系统需要多套不同的代码,这增大了应用开发的难度,纸面参数是好看了,却苦了软件开发者。

IPU / Graphcore

其次,GPU、FPGA和AI处理器厂商都推出了截然不同的加速器方案,这些方案不仅仅采用了自己专用的处理器架构,还有自己的执行指令和编译器。在这样不统一的架构下,将并行程序移植到异构处理器上需要的可不只是重新编译,还有代码重写。也正因如此,HPC的代码生态虽然不弱,但近半数以上可能永远都不会被移植到其他加速器上,甚至这一部分工作量还分摊到了加速器厂商的软件开发工作量上。

所以,必须得使用优秀的软件栈,这样才能让开发者充分利用异构处理器的计算资源,而不用在编程时考虑复杂的硬件细节。现在已经有了不少跨平台的编程标准,比如C++++/Fortran、OpenMP、SYCL和Kokkos等。

最后是复杂的数据存取过程,异构带来的不仅是不同层级的计算架构,还有不同层级的存储架构,比如主存储、主缓存、设备主存、设备缓存和寄存器等等。数据要在多种存储类型之间移动,程序执行要在同时对多种存储进行存取,这些存储方式的带宽和延迟也不尽相同。

异构计算的未来

在近期举办的CIUK 2021大会上,HPC研究组的Simon McIntosh-Smith教授发表了他自己对异构计算未来的看法。他认为异构计算的趋势还将继续发展下去,差异化不会消失,但也不会出现极度差异化的情况。

其次CPU与GPU的关系将更加紧密,比如缓存一致和封装集成等,其他加速器在特定场景下声称的性能数据都很优秀,但要说通用计算性能,GPU还是要略胜一筹。而且依目前的趋势来看,CPU也在慢慢汲取GPU上的优点,比如HBM、宽矢量处理器的核心、核心内部的加速器等等。编程的困境固然已经有了改善的迹象,但还有一段长路要走。

异构计算的前世今生

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |