FPGA 的用途

在介绍 FPGA 的用途之前,先给大家讲一个笑话:

话说一个资深工程师出国的时候带了一块 FPGA 开发板。

海关问道:“这是什么东西?”

工程师说:“FPGA 开发板”。

海关又问:“FPGA 是什么?”。

工程师回答说:“你想让它是什么,它就是什么(It can be whatever you want)”

能看懂这个笑话就说明你已经对 FPGA 有了一定的了解。作为一种可编程器件, FPGA 能实现任何数字 器件的功能,上至高性能 CPU ,下至简单的 74 电路,都可以用 FPGA 来实现。 FPGA 就像一张白纸,任由 你在上面涂鸦或者作画;FPGA 又如同一堆积木,随便你用来搭建城堡或者玩“过家家”。

FPGA 是什么这个问题可能不太好回答。但是如果说 FPGA 用来干什么,那么答案就显而易见了。你可 能都还没意识到,在我们的生活中,FPGA 已经无处不在了。从你家里使用的高清电视,到附近的无线电接 收塔;从****门口的 ATM 机,到微软数据中心的服务器,都可以看到 FPGA 的身影

如上图所示, FPGA 广范应用在汽车、军用装备、图像处理、有线和无线通信、医****,以及工业控制等 诸多领域。 可编程逻辑天生就为并行地实现算法提供了理想的资源。比如在图像处理中,要同时对大量的像素点 进行数学运算,而 FPGA 就很适合像这种像素点级别的图像处理所需的快速、并行的操作。

FPGA 并行 的特性决定了它在某些特定行业应用上具有得天独厚的优势,例如在医疗领域。医学影像比 普通图像纹理更多,分辨率更高,相关性更大。因此,为严格确保临床应用的可靠性,对图像的压缩、分 割等预处理、图像分析及图像理解等要求更高。这些要求恰恰可以充分发挥 FPGA 的优势,通过 FPGA 加 速图像压缩进程、删除冗余、提高压缩比、并确保图像诊断的可靠性。

在金融领域,由于采用流水线逻辑体系结构,数据流处理要求低延时,高可靠性。这在金融交易风险 建模算法应用中是重要的关键点,而 FPGA 正具备了这种优势。类似的行业和领域还有很多,特别是在深 度学习和神经网络,以及图像识别和自然语言处理等领域,FPGA 正显示出其独有的优势。

1.3 ZYNQ PL 简介

ZYNQ PL 部分等价于 Xilinx 7 系列 FPGA ,因此我们将首先介绍 FPGA 的架构。

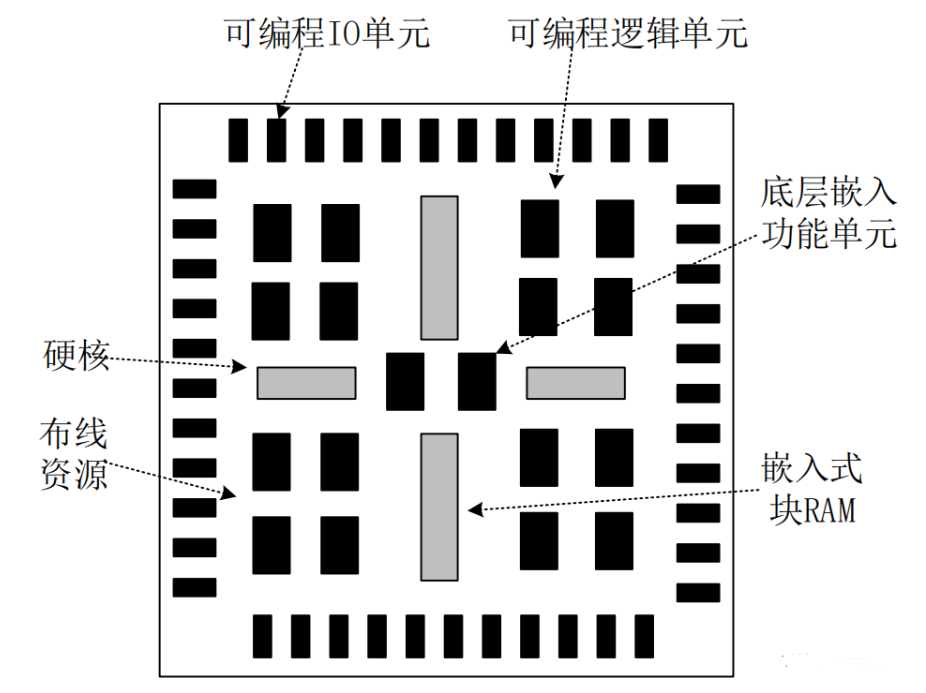

简化的 FPGA 基本结构由 6 部分组成,分别为可编程输入 / 输出单元、基本可编程逻辑单元、嵌入式块

RAM 、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等,如下图所示

每个单元的基本概念介绍如下。

1) 可编程输入 / 输出单元

输入 / 输出( Input/Ouput )单元简称 I/O 单元,它们是芯片与外界电路的接口部分,完成不同电气特性 下对输入/ 输出信号的驱动与匹配需求,为了使 FPGA 具有更灵活的应用,目前大多数 FPGA 的 I/O 单元被 设计为可编程模式,即通过软件的灵活配置,可以适配不同的电气标准与 I/O 物理特性;可以调整匹配阻抗 特性、上下拉电阻、以及调整驱动电流的大小等。 可编程 I/O 单元支持的电气标准因工艺而异,不同芯片商、不同器件的 FPGA 支持的 I/O 标准不同,一 般来说,常见的电气标准有 LVTTL , LVCMOS , SSTL , HSTL , LVDS , LVPECL 和 PCI 等。值得一提的是, 随着 ASIC 工艺的飞速发展,目前可编程 I/O 支持的最高频率越来越高,一些高端 FPGA 通过 DDR 寄存器 技术,甚至可以支持高达 2Gbit/s 的数据数率。 ZYNQ 上的通用输入 / 输出功能( IOB )合起来被称作 SelectIO 资源,它们被组织成 50 个 IOB 一组。每 个 IOB 有一个焊盘,是与外部世界连接来做单个信号的输入或输出的。每个 IOB 还包含一个 IOSERDES 资 源,可以做并行和串行数据的可编程转换。

2) 基本可编程逻辑单元

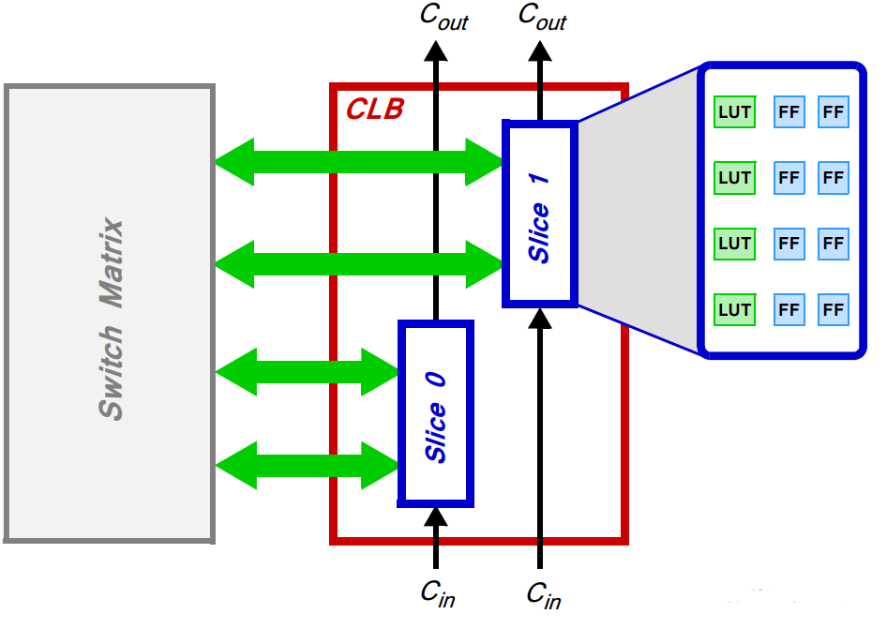

基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的 逻辑功能。FPGA 一般是基于 SRAM 工艺的,其基本可编程逻辑单元几乎都是由查找表( LUT , Look Up Table ) 和寄存器(Register )组成。 Xilinx 7 系列 FPGA 内部查找表为 6 输入,查找表一般完成纯组合逻辑功能。 FPGA 内部寄存器结构相当灵活,可以配置为带同步 / 异步复位或置位,时钟使能的触发器,也可以配置成 锁存器,FPGA 依赖寄存器完成同步时序逻辑设计。 一般来说,比较经典的基本可编程逻辑单元的配置是一个寄存器加一个查找表,但是不同厂商的寄存 器与查找表也有一定的差异,而且寄存器与查找表的组合模式也不同。当然这些可编程逻辑单元的配置结 构随着器件的不断发展也在不断更新,最新的一些可编程逻辑器件常常根据需求设计新的 LUT 和寄存器的 配置比率,并优化其内部的连接构造。 例如,Altera 可编程逻辑单元通常被称为 LE ( Logic Element ),由一个寄存器加一个 LUT 构成。 Altera 大多数 FPGA 将 10 个 LE 有机地组合在一起,构成更大的功能单元——逻辑阵列模块( LAB , Logic Array Block)。 LAB 中除了 LE 还包含 LE 之间的进位链, LAB 控制信号,局部互联线资源, LUT 级联链,寄存 器级联链等连线与控制资源。 Xilinx 7 系列 FPGA 中的可编程逻辑单元叫 CLB ( Configurable Logic Block ,可配置逻辑块)每个 CLB 里包含两个逻辑片(Slice)。每个 Slice 由 4 个查找表、 8 个触发器和其他一些逻辑所组成的。CLB 示意图 如下所示:

3) 嵌入式块 RAM

目前大多数 FPGA 都有内嵌的块 RAM ( Block RAM ), FPGA 内部嵌入可编程 RAM 模块,大大地拓展了 FPGA 的应用范围和使用灵活性。不同器件商或不同器件族的内嵌块 RAM 的结构不同,Lattice 常用的 块 RAM 大小是 9KBIT;Altera 的块 RAM 最灵活,一些高端器件内部同时含有 3 种块 RAM 结构,分别是 M512 RAM,M4K RAM,M9K RAM。

我要赚赏金

我要赚赏金