对于电源类产品怎么做差异化是研发,应用和市场必须一起坐下来探讨的话题。

如何做到性能优异,die size又比竞品小,成本又比竞品低呢?

我从以下2个方面去探讨工艺的改善:

Fab厂(晶圆工艺的改善)

封测厂(封装工艺的改善)

一 晶圆工艺改善

工艺制程的迭代:模拟电源类产品目前主要用的工艺制程是180nm,110nm等等,已有厂商开始尝试90nm的新工艺,用先进工艺的好处是可以减小晶体管的线宽,相同面积下可以塞下更多的晶体管。但是由于主功率管占了芯片大部分的面积(如DCDC,LDO等),那么一味的减小线宽不一定是最优解,反而带来了成本的提高,如mask成本和制造成本。但是对于数字+模拟的混合电路芯片,确实可以有效减少数字部分所占的面积(如Register,I2C,I2S, MIPI RFFE等接口)。

晶圆尺寸的升级:模拟电源类产品目前主力是放在8寸晶圆上,但是如TI等厂商都已开始在12寸晶圆上生产,晶圆边角浪费会大大的减少,单晶圆能产出更多的芯片,可以有效降低Die的成本。缺点也很明显,成本会提高不少,但是折算到单颗Die就不好说了。

晶圆厚铜工艺:最早用到厚铜工艺的是TI,它带来的好处是可以有效减小功率管的Ron,增加芯片的散热能力。缺点是受制于Fab的工艺能力,在调试的过程中有可能会有裂片的风险。目前看TI的Fab在这方面做得是比较好的。

自有工艺团队配合Fab一起调工艺:可以有效改善功率管的Ron,VGS,VDS,QG等等的性能。由于FAB的BCD标准工艺有很多限制也会变相提高晶圆的成本,比如需要开发一颗车规级42V耐压的buck产品,通常的做法是选用标准BCD工艺的60V耐压管子,但是如果自有工艺团队能够开发45V~50V耐压的器件可以大大的减小主功率管的尺寸,从而降低成本。目前看下来MPS和TI在工艺改善上是做得比较好的。

二 封装工艺改善

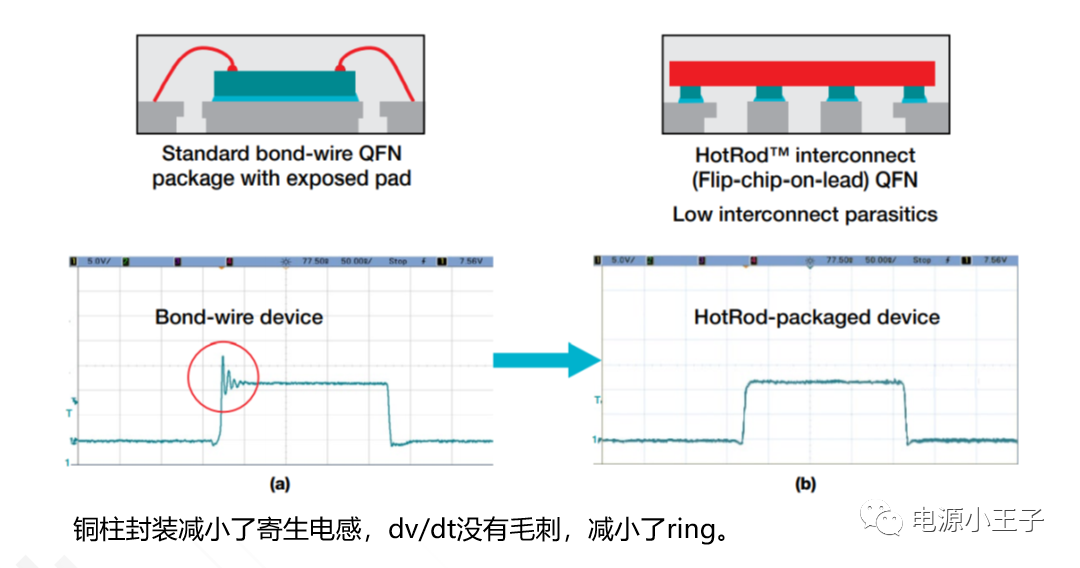

FC铜柱倒装工艺:很多新出来的电源产品目前都采用了铜柱倒装工艺。这种工艺可以有效减小杂散寄生电感。Ron和散热也会比打线有了很大的改善。

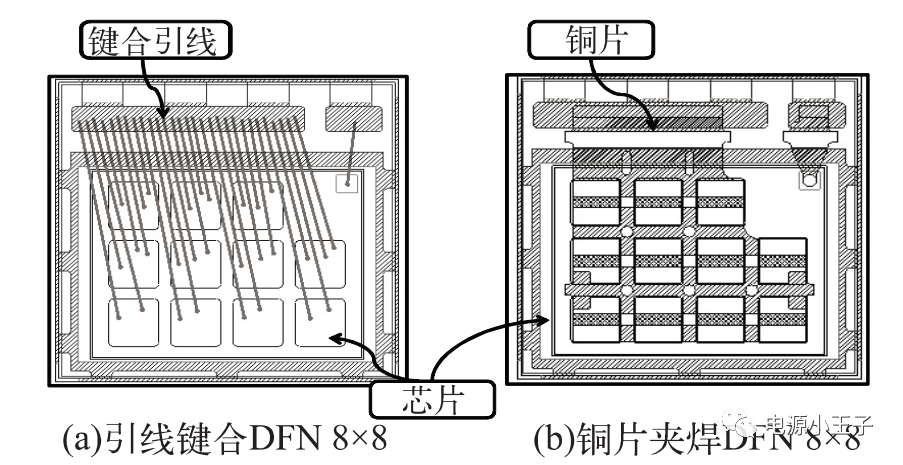

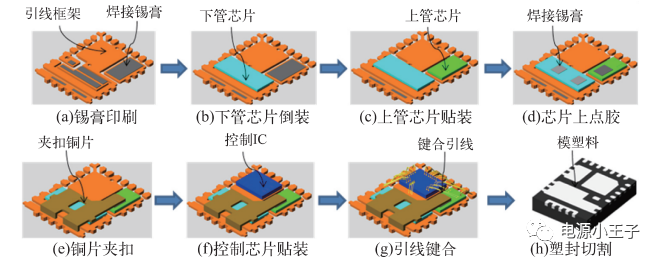

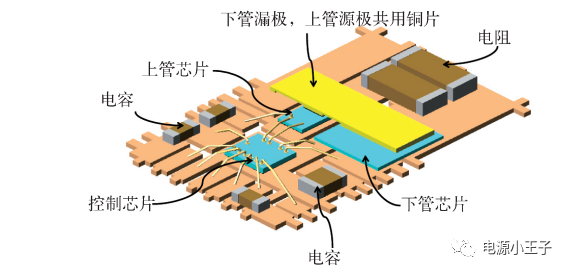

2. Clip bond:传统引线键合会产生寄生电感、电阻并增加线路延迟,限制热传导,铜片夹扣键合相比传统的引线键合方式提升了电流传输能力,提高了产品整体效率,降低了元器件功耗,提升 了产品的散热性能,降低封装寄生参数,且其工艺简单,综合成本相对低廉。铜片夹扣键合工艺被广泛应用于低压大电流元器件上,其终端产品有网络服务器、充电器、笔记本、配置器高端显卡等,这些产品对元件散热、效率要求较高

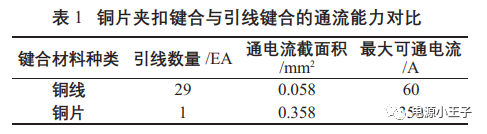

两种封装方式的最大可通电流如表所示,其中铜线键合产品每根铜线的最大通流能力在 2.0~2.1 A, 29根引线加总最大通流能力为60A,铜片夹扣键合产 品最大通流能力为350A。

Drmos by Clip Bond

3. 烧结银工艺:这个工艺适合于电源模块的合封。

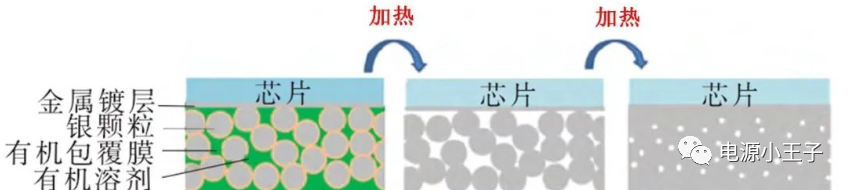

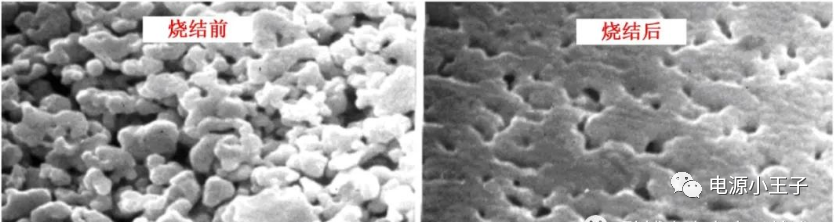

首先让我们先看一下什么是烧结技术?烧结是一种零件加工技术,通过硬化金属粉末,在低于金属熔化温度下进行烘烤,使"零件成型"的一种技术,这种工艺称为粉末冶金,硬化成型零件称为"烧结金属"或"烧结产品"。烧结本质上是一个固态的扩散过程,是一个在固体颗粒的熔点以下,分散的颗粒变成完全互连的整体的过程。在这个过程中,烧结材料可以与界面上部和下部的基材表面形成结合,最终形成一个良好的连接。

目前功率半导体封装中常说的低温银烧结就是用很细的银粉做焊剂,在250℃和高压作用下烧结成成极低孔隙率的银层,由于银高达962°C的熔点,所以也叫低温烧结,功率半导体芯片与DBC基板的烧结过程如下:

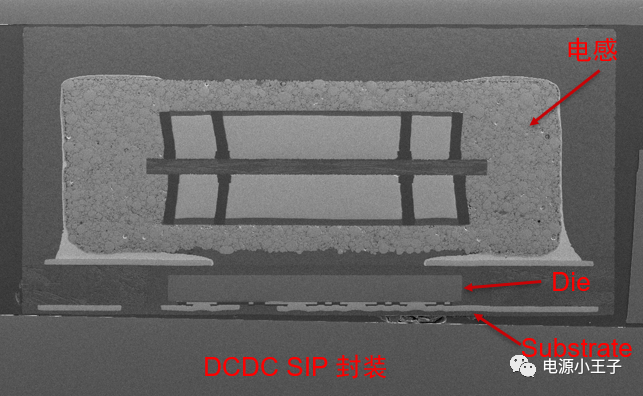

4. SIP封装工艺(System in package):是通过基板埋Die来合封MOSFET, Driver,电感等器件的方案。如下图是典型的叠层合封结构。

我要赚赏金

我要赚赏金