对于现今的FPGA芯片供应商,在提供高性能和高集成度独立FPGA芯片和半导体知识产权(IP)产品的同时,还需要提供性能卓越且便捷易用的开发工具。本文将以一家领先的FPGA解决方案提供商Achronix为例,来分析FPGA开发工具套件如何与其先进的硬件结合,帮助客户创建完美的、可在包括

独立FPGA芯片和带有嵌入式FPGA(eFPGA)IP的ASIC或者SoC之间移植的开发成果。

随着人工智能、云计算、边缘计算、智能驾驶和5G等新技术在近几年异军突起,也推动了FPGA技术的快速发展,如Achronix的Speedster7t独立FPGA芯片不仅采用了7nm的工艺,而且还带有二维片上网络(2D NoC)和机器学习处理器(MLP)来支持高通量数据的流动和处理。同时,Achronix的

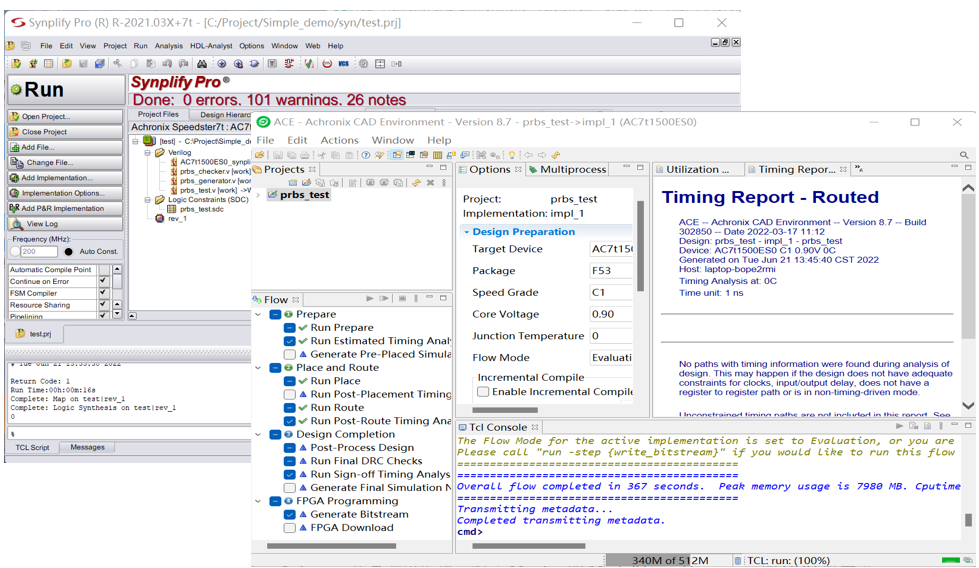

Speedcore eFPGA IP也被很多全球领先科技公司集成到其ASIC或者SoC中。Achronix也推出了其ACE开发工具套件来同时支持这些产品,如图1所示。它不仅提供了先进的开发功能和资源管理能力,还集成了最新的Synplify Pro软件。

图1 Achronix ACE开发工具套件

Achronix的ACE开发工具套件是一套最先进的设计工具链,可为Achronix的所有硬件产品提供支持。ACE与业界标准的逻辑综合工具配合使用,可支持FPGA设计人员便捷地将其设计映射到Speedster7t FPGA、Speedcore eFPGA中。这也意味着Achronix的用户可以根据其应用的规模,在Speedster7t、搭载该芯片的VectorPath加速卡、以及带有Speedcore的SoC或者ASIC中选择最佳的产品形态和路线图。

ACE包括了为Achronix优化的Synopsys的Synplify-Pro工具。Achronix仿真逻辑库也获得了Mentor的ModelSim、Synopsys的VCS等主流仿真工具的支持,设计人员还可以使用功能强大的布局规划工具(floorplanner)进行设计优化,并且在进入时序驱动的布局布线之前为所有设计模块实例分配区域或位置。

ACE还包括一个关键的时序路径分析工具,可以分析时序以确保设计符合性能要求。设计人员还可以使用ACE强大的Snapshot嵌入式逻辑分析器来创建复杂的触发条件,并显示在Speedster7t器件中运行的信号。

总之,ACE开发工具套件可以覆盖FPGA设计开发、编译到调试所有的必备功能。

2. ACE中集成的时序路径分析工具

时序分析是FPGA开发中一个十分关键的过程,也是复杂FPGA系统开发必须进行的一步。时序问题是所有FPGA设计者绕不开的经常会出现的问题。如何能让FPGA设计跑在更高的频率,如何能更快地解决时序问题,对于FPGA设计至关重要。

好的时序路径分析工具能够帮助设计者更快地定位时序问题。Achronix ACE开发工具套件集成了功能强大的时序路径分析工具,相信能够有效地帮助FPGA设计者解决各种各样的时序问题。

3. 时序报告的产生

FPGA的基本开发流程中,有多处可以进行时序分析的地方。ACE开发工具套件可以提供综合以后、布局以后、布线以后等各个阶段的时序分析。对于大多数设计者,只做布局布线以后的时序分析即可,因为带了布局布线信息的时序分析最为精确,下面我们重点介绍布局布线以后的时序分析。

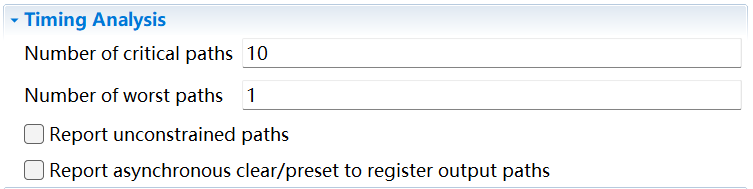

在利用ACE工具生成时序报告之前,我们先设置时序分析的相关参数,ACE会根据设置的参数自动生成一个时序分析报告。如图2所示,第一项设置关键路径的打印条数,默认是10条。第二项是设置每条关键路径中最坏路径的打印条数,因为在每条关键路径的两个端点中可能包含多条路径。

第三个单选框是打印未约束的时序路径,这个信息可以帮助设计者查看时序约束是否覆盖了设计中的所有路径,报告中出现的未约束的路径是不是用户有意不想让工具去分析的路径。最后一个单选框是打印异步clear和preset信号到寄存器数据输出的路径。

图2 时序报告相关参数

在ACE跑完布局布线时序分析以后,工具会根据参数设置产生相应的时序报告。时序报告有三种格式,html,csv和txt。三种文件格式不同,内容完全一样。

除了可以自动生成时序报告以外,ACE开发工具套件也支持用户用Tcl命令去生成指定路径的时序报告。ACE开发工具套件支持的时序分析相关的Tcl命令如下:

check_setup:对设计做一些时序方面的检查。

prepare_sta:做静态时序分析的准备,进入时序分析模式。

report_checks:用于报告具体路径的时序分析结果。

report_clock_properTIes:用于报告设计中用到的时钟属性。

reset_sta:用于退出时序分析模式。

通过上面五条Tcl命令可以灵活地对设计进行时序检查和分析,具体使用可参见Achronix ACE User Guide UG070。

4. 时序报告详解

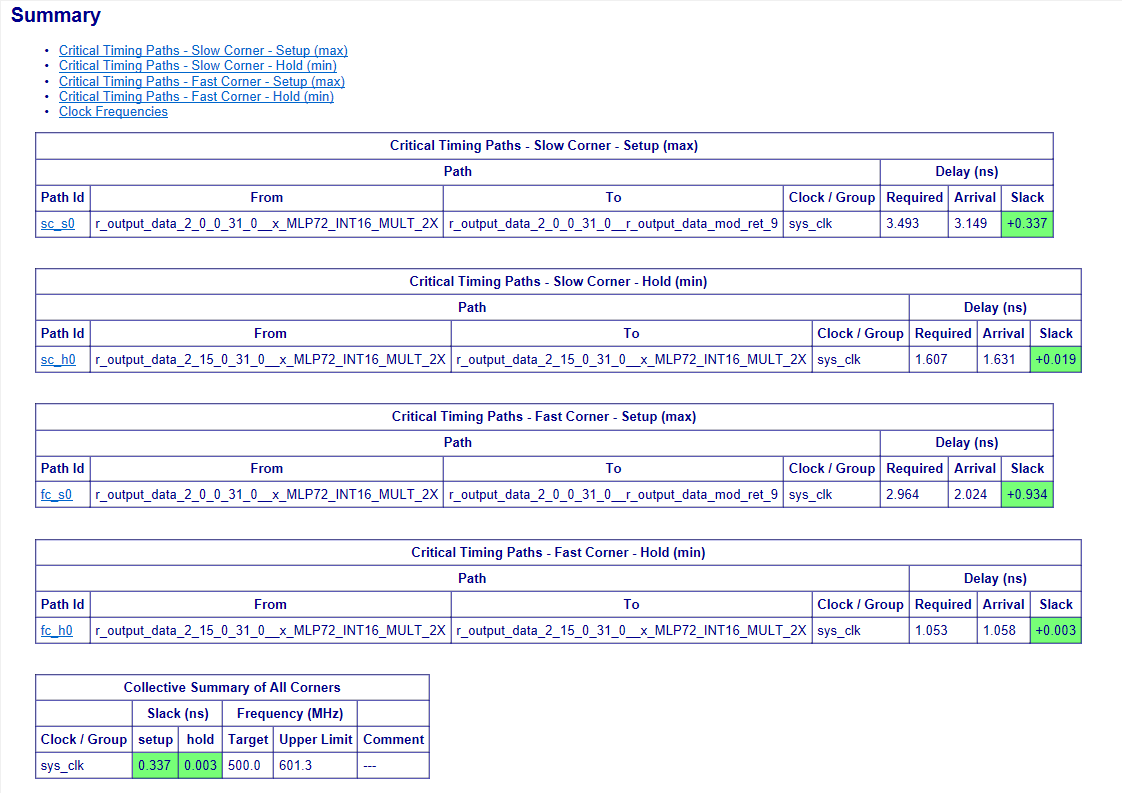

打开时序报告,文件开头会有一个summary,如图3所示。

图3 时序报告Summary

在Summary里面会显示在fast corner和slow corner下的setup和hold分析的关键路径。同时在Summary的最下面,系统会报告每个时钟的目标约束和实际能跑到的频率。

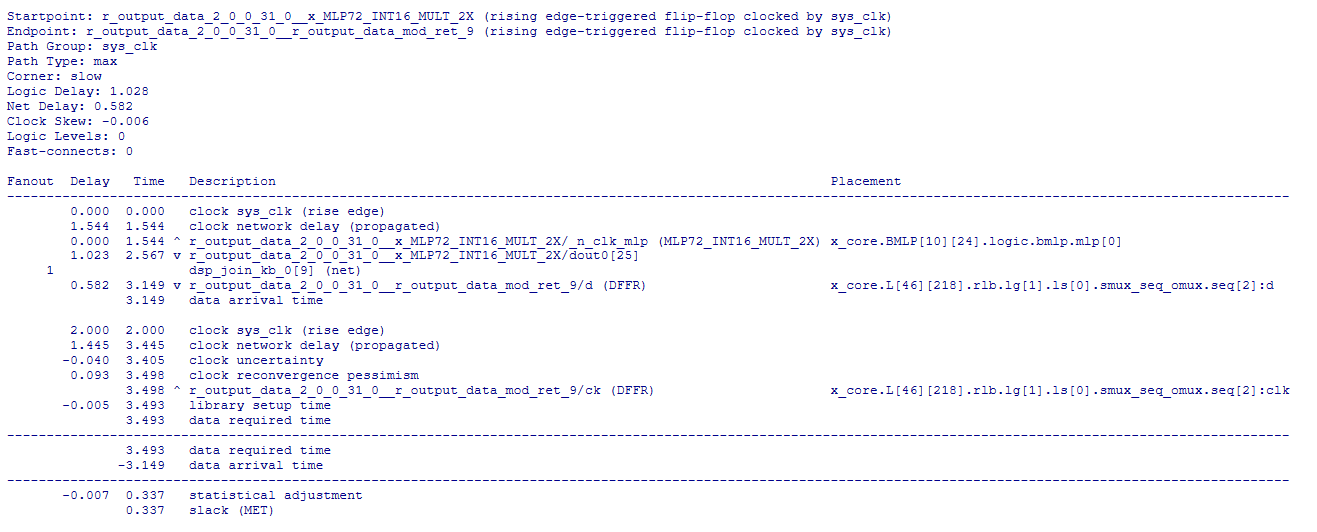

在Summary页面中,关键路径前有一个path id,这个path id同时又是一个超链接,用鼠标点击后会自动跳转到具体的时序路径分析页面,如图4所示。

图4 具体的时序路径分析

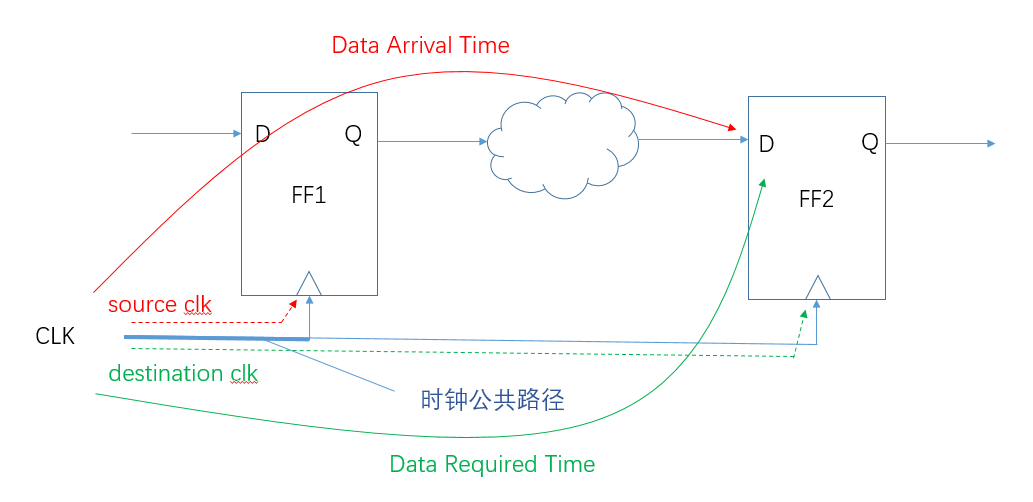

图5所示是一条分析setup的路径。

图5 setup TIming路径分析

数据从FF1发送出去被FF2捕获,这里的Data Arrival TIme等于时钟launch edge到FF1的CLK端口需要的时间T_launch,加上源时钟的路径延迟,即CLK端到数据Q端需要的时间Tco,再加上数据的传播延迟T_delay:

Data Arrival TIme = T_launch + Tco + T_delay = 1.544 ns + 1.023 ns + 0.582 ns = 3.149 ns

Data Required Time等于CLK到达FF2所需要的时间T_capture,加上clock uncertainty,减去CLK路径悲观补偿,再减去FF2的建立时间T_setup, 最后不要忘了加上一个时钟周期:

Data Required Time = T_period + T_capture - T_clock_uncertainty +

T_clk_reconvergence_pessimism – T_setup = 2.000 ns + 1.445 ns - 0.040 ns

+ 0.093 ns – 0.005 ns = 3.493 ns

这样Setup slack就可以计算得出:

Setup Slack = Data Required Time - Data Arrival Time – Statistical Adjustment= 0.344 ns – 0.007ns(时序调整值) = 0.337ns

这里要提到时钟公共路径悲观补偿,因为时钟到达FF1和FF2开头一段路径是重合的,在这段路径里我们还是用最大时延差和最小时延差去进行时序分析的话是很悲观的,所以需要用这个参数补偿回来。

5. 图形化界面辅助时序分析

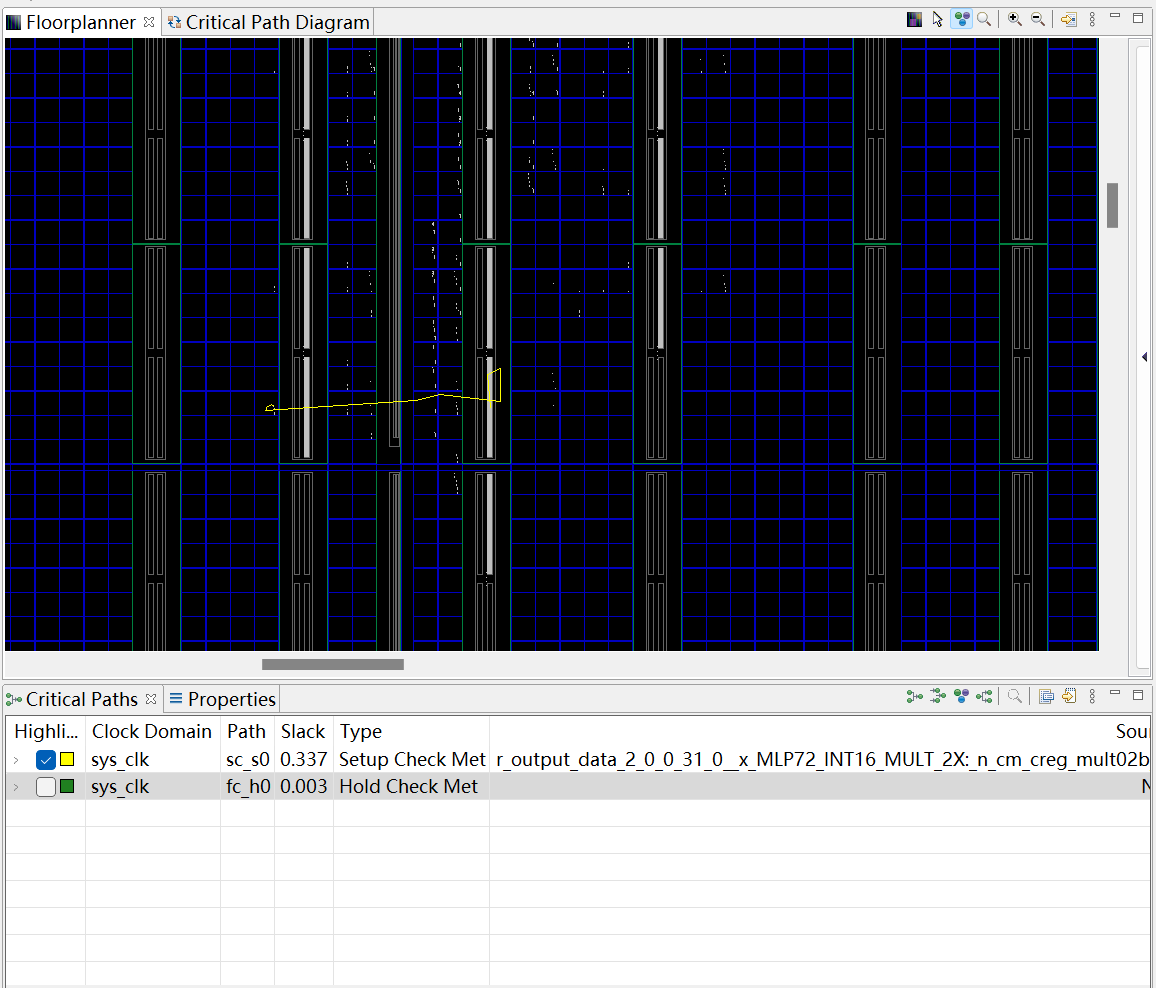

在ACE的floorplanner界面中,可以通过图形界面辅助进行时序分析,如图6所示。

图6 floorplanner界面的时序路径分析

ACE工具会在Critical

Paths页面把时序报告中的时序路径全部列出来,不满足时序的路径用红色高亮显示,满足时序的路径用绿色表示。用户选中其中一条路径,在floorplanner界面里这条路径的走线就会自动高亮显示出来,便于用户看到这条路径在FPGA内部具体的连接,以及源寄存器和目的

寄存器在器件中的具体位置。

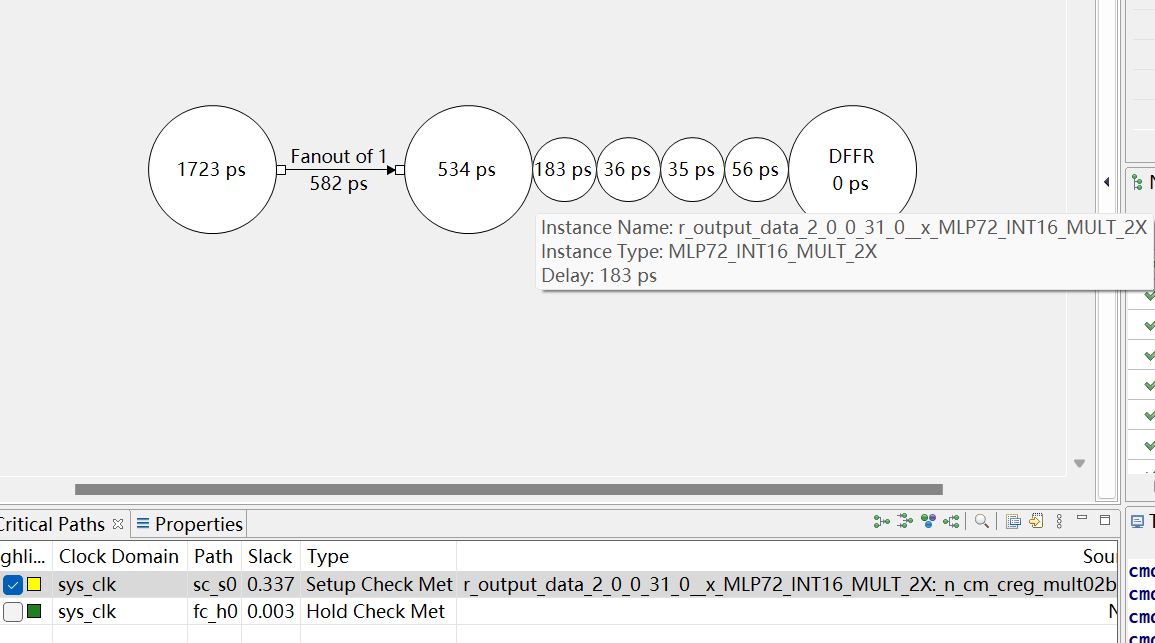

图7 示意图表示的时序路径

在floorplanner页面旁边有个Diagram视图,选中以后可以示意图的方式显示出这条路径的具体延时数据,鼠标停留在框图上还会显示更具体的信息。

综上所述,在时序分析方面,ACE开发工具套件提供了完备的时序分析工具,从时序报告,到Tcl命令,再到图形化的显示,用户可以很方便地利用工具进行时序分析,找到具体的问题所在,然后针对具体问题来优化设计的整体性能。

后面我们会继续深入了解ACE开发工具套件的各种特性,并且会用一些例子来说明如何更高效地利用这些特性为FPGA设计提供方便,敬请期待。

如需更多信息或者有任何疑问您可以通过Achronix公众号里的联系方式联系我们,也可访问Achronix公司官方网站

http://www.achronix.com。

参考文献:

1. Achronix website www.achronix.com

2. Achronix ACE User Guide UG070

我要赚赏金

我要赚赏金