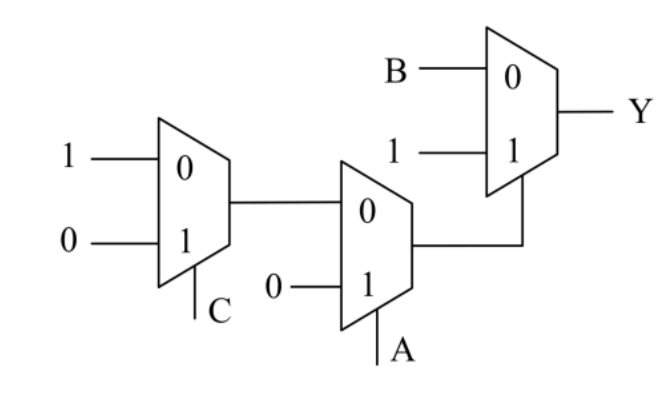

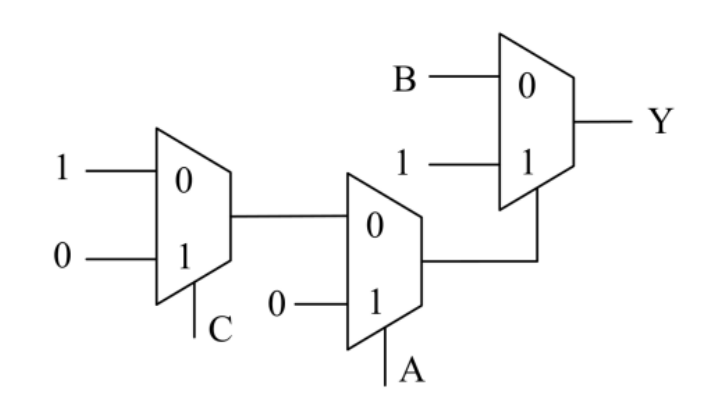

7、【简答题】请写出下述2to1 MUX所搭建电路的布尔表达式,并将布尔表达式化简。(3分)

解析:本题目主要考察了数字电路基础中的电路图与布尔表达式的转化与化简

2to1 MUX的布尔表达式可以写成:Y = CA+C’B

O1点的布尔表达式为:O1 = C*0+C’*1 = C’

O2点的布尔表达式为:O2 = A*0+A’*O1 = A’O1 = A’C’

Y点的布尔表达式为:Y = O2*1+O2’B = O2+O2’B ,利用公式:A+A’B = A+B,得Y = O2+B = A’C’+B

可以看到,在上一期的第6题逻辑表达式的化简中也用到了“A+A’B = A+B”这个公式,可见这个公式还是比较常见的,在化简逻辑表达式的时候十分有用,所以一定要牢记。

8、【简答题】简述你做过的项目,及自己负责的工作。(10分)

1)画出功能图

2)写出主要实现步骤,涉及到哪些方面理论没用到的仪器和工具。

解析:本题目主要考察了对所做项目的理解程度,是一道开放性的题目

这种类型的题目可以说是最简单的,但同时也是最难把握的,因为每个人做的项目都不一样,这里就主要谈谈题目的设置所想考察的点。

首先介绍一个项目,最直接的就是看项目的结构框图,结构图不需要画太详细,但需要把数据传输、处理的关键模块、路径,时钟域结构、缓存结构等表达清楚,让评审的人一看框图就知道项目的难度、关键的技术点是哪里。

主要实现步骤其实就是对框图结构的简单描述,不需要太详细,但需要表达出关键的内容。考察了对项目的简述的组织能力,是否能用简短的语言把关键的东西表达清楚。

涉及到的理论是一个较为全面的考察,有些时候只知道理论不知道如何实现,其实相当于不会,因为做工程一定要去实践和应用,否则就是纸上谈兵;而如果只会用,而不能将用到的技术和理论对应上,就无法举一反三,下次在哪里用到还是一知半解。

用到的仪器和工具主要是想考察是否真正的使用过这些工具来解决过工程问题。

套用上面的这种格式,其实我们完全可以把简历中的项目也用类似的结构整理、提炼出来。让面试官一看就知道项目的内容、难度,你的工作量,以及你对这个项目的把握理解程度,同样在面试的时候也要做好面试官问到这些问题的准备。

9、【简答题】请描述一下在学校所完成的主要项目的架构,并着重说明自己所完成部分的收获是什么?(10分)

解析:本题目主要考察了对所做项目的理解程度,是一道开放性的题目

和上一道题目是同样的类型,只是问法不一样。在项目具备一定难度的基础上,面试关希望看到的是你在这个项目中参与的角色、得到的收获以及遇到问题是如何解决的,如果能在这几个方面都回答的较好那就非常完美了。

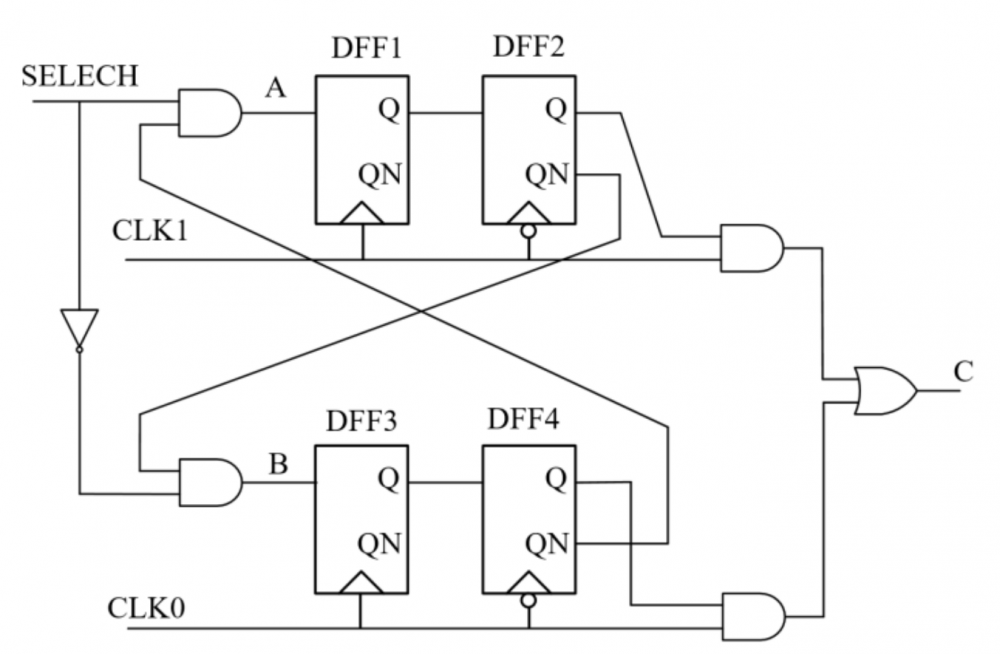

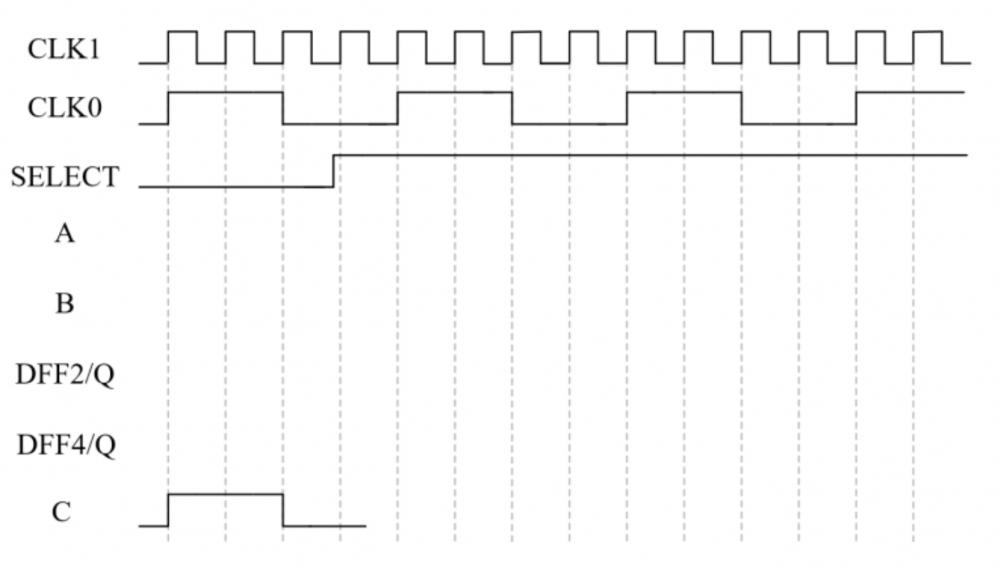

10、【简答题】

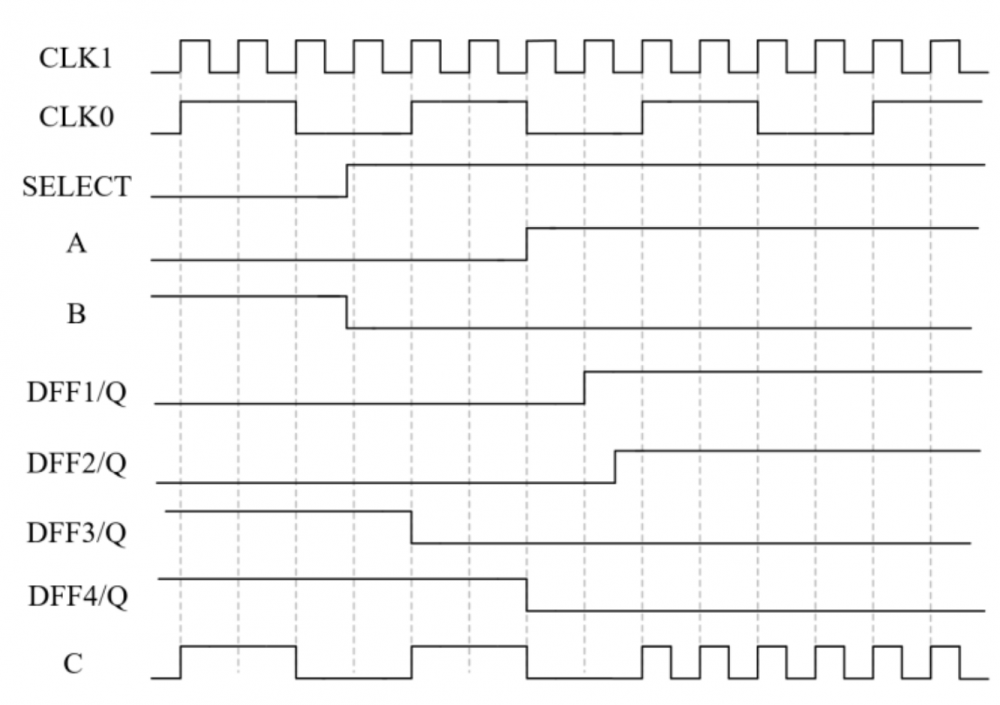

1)请根据电路图补全时序图(6分)

2)请说明该电路的功能(3分)

3)请说明电路图中DFF1和DFF3的作用。若去掉这两个DFF,电路中存在何种风险?(3分)

4)请说明DFF2和DFF4需要采用负沿采样的原因。若采用正沿采样,电路中存在何种风险(3分)

解析:本题目主要考察了时钟无毛刺切换

1)如果仅看电路,其实并不能很直观的看出其功能,但结合波形,我们大概可以看出,这个电路要实现的功能应该是做时钟的切换。SELECT作为时钟切换的选择信号,实现对CLK0和CLK1的切换,然后由C端口输出。既然是时钟切换,自然就会涉及到时钟切换时的毛刺问题(关于时钟切换会产生毛刺的原因和Verilog代码请参考“求职攻略| 异步电路中的时钟无毛刺切换(Glitch-Free)”)。结合功能和电路我们就可以反推出波形。

需要注意的就是在SELECT发生变化的时候,有些点的波形时立刻变化的,而有些点的波形时通过寄存器产生了延时,会延后变化。

2)电路的功能为;时钟无毛刺切换或Glitch Free

3)DFF1和DFF3的作用是通过寄存器打拍来去除时钟切换产生的毛刺,从而使系统较大概率的出现亚稳态现象,所以不可以去掉。

4)采用负沿采样也是为了保证DFF2和DFF4的输出在跳变时发生在时钟的低电平区域,这样再通过后级的与门时就可以减少毛刺的出现。如果采用正沿采样,则会有产生毛刺的风险。

我要赚赏金

我要赚赏金