USART波特率计算方法解析

USART 波特率发生器

USART 内置波特率发生器,其通过使用以PCLKx为基准的内部计数器进行计数,由用户设定其该计数器的溢出值(通常也称作分频系数),每计数达到一次溢出代表一位数据,故每位数据位宽就是分频系数个PCLKx周期。

用户通常可通过调整PCLKx以及分频系数来产生特定的USART波特率。以下基于AT32F435的USART1为例对其进行解析

关键词简介

USART时钟源:即USART波特时钟的来源。USART1的来源为PCLK2,PCLK2由HCLK分频而来,HCLK由系统时钟分频而来。当系统时钟为288MHz,HCLK不分频,PCLK2二分频时,此时PCLK2时钟为144MHz

目标波特率:即应用需求的USART波特率。可根据需求随意设定(但必须保障收发双发波特率一致),通常为9600、38400、115200等一些常见的典型波特率。

分频系数:即对PCLK2的分频值。为达到期望的波特率,必须要对PCLK2进行分频,该分频系数可配置为0~0xFFF内的任意满足需求的值

波特率公式

USART波特率 = USART时钟源/分频系数

驱动实现

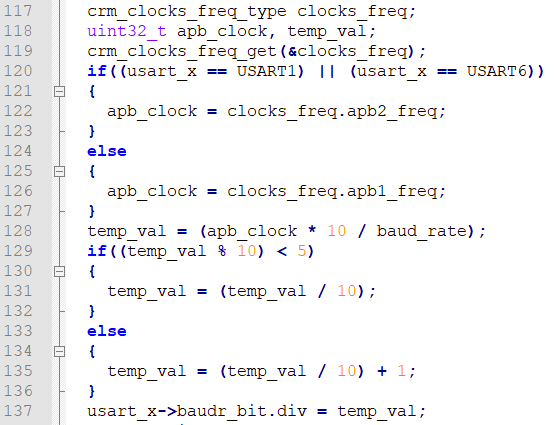

如下图

第119行到第127行为获取“apb_clock”,即获取USART时钟源。需要注意不同的串口所挂载的PCLK总线不同

第128行到第136行为计算“分频系数”,通过波特率公式而来。且为更接近目标波特率,采用“四舍五入”进行处理

第137行即为将计算得到的分频系数实际写入USART_BAUDR寄存器。

示例:

1)系统时钟为288MHz,PCLK2做二分频,目标波特率为115200时,“分频系数”=288000000/2/115200=1250,实际写入USART_BAUDR寄存器值应为1250(即十六进制的0x4E2)。

2)系统时钟为288MHz,PCLK2做二分频,USART_BAUDR寄存器值为0x3A98(即十进制15000)时,“波特率”=288000000/2/15000=9600。

注:

A.USART波特率的配置需要在USART使能前进行配置;

B.不同的USART挂载的PCLKx不同,应用需要自己计算波特率时要注意PCLKx的分频;

C.PCLKx过大时,某些极限波特率无法达到(比如PCLK为144MHz时,无法实现1200的USART波特率),此时可通过增加分频来降低PCLKx。

我要赚赏金

我要赚赏金