高速先生成员--孙小兵

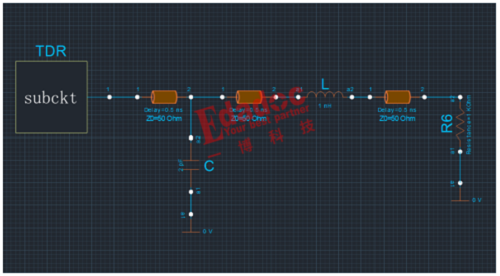

我们先来了解一下容性负载和感性负载对链路阻抗的影响。仿真链路模型如下图所示。链路中有三段50Ω的理想传输线,第一段和第二段之间增加一个电容模拟容性负载,第二段和第三段之间增加一个电感模拟感性负载,链路末端是一个1KΩ的电阻相当于开路。利用TDR仿真工具看整个链路的阻抗情况。

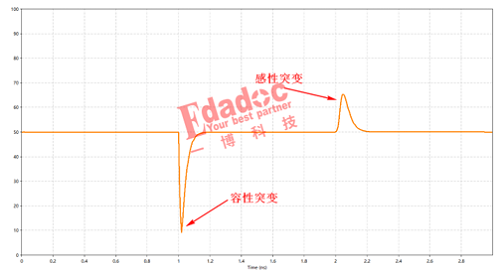

这里先简单介绍一下阻抗曲线结果如何看。坐标横轴表示时间,对应传输线从一端看过去不同传输时刻的位置点,坐标纵轴表示阻抗值。从下面阻抗曲线来看。链路在传输1ns时阻抗发生变化,而在链路中第一段传输线的传输时延是0.5ns。为什么时间刻度不对应呢?原因是看链路时域阻抗的方法是通过信号反射原理,比较输入电压和反射回来的电压幅值。脉冲信号需要有一个来回的过程。所以阻抗曲线中时间点实际是传输线时延的两倍。

从上面链路阻抗曲线结果来看,容性负载导致链路阻抗瞬间降低,然后又缓慢上升恢复到原来走线阻抗。感性负载导致链路阻抗先慢慢升高,然后缓慢恢复到链路阻抗上。对于链路中的出现的容性突变和感性突变,信号感受到的阻抗变化并不是只存在一瞬间的,而是随时间变化的。

了解了链路中容性负载和感性负载对链路阻抗的影响后,下面我们就来看看在DDR的Fly_By设计链路中容性负载对链路阻抗的影响。如下是常见的DDR一拖五的Fly_By拓扑的设计方案,链路中一个主控拖五个负载颗粒,端接电阻放在最后一个颗粒后面。

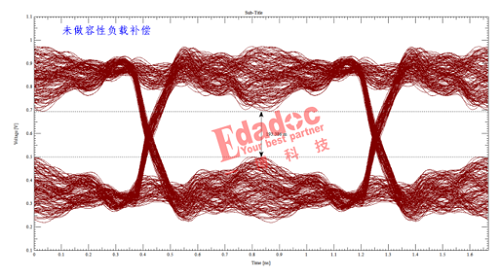

我们先对比下做容性负载补偿前后DDR链路前端颗粒信号质量情况,因为对于Fly_By链路,前端颗粒的信号质量是最差的。下图是有无做容性负载补偿链路中前端颗粒仿真得出的信号眼图。

从以上仿真结果来看,当没有做容性负载补偿时前端颗粒接收信号眼高为193mV,而做了容性负载补偿之后,信号眼高升高到303mV。因此在多负载链路中,容性负载补偿对负载信号质量有明显地改善。

那容性负载对链路究竟是产生怎样的影响呢?容性负载补偿具体需要怎么做,为什么做容性负载补偿可以改善链路上的信号质量?下面就通过对链路阻抗的观察分析进行阐述。

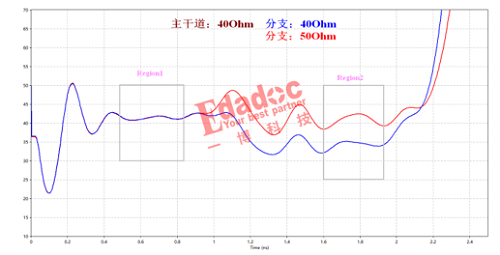

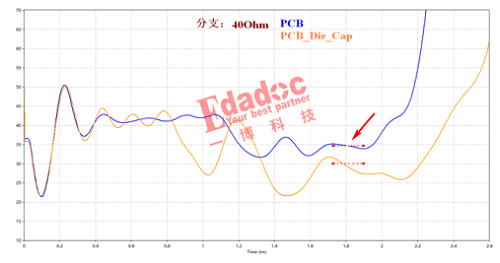

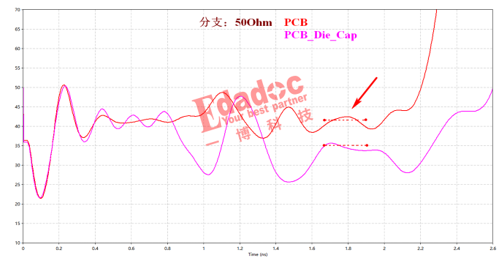

分别提取上面链路中支路走线做容性负载补偿前后的S参数,利用仿真软件看链路TDR详情如下,探测点选在主控一端。蓝色曲线是未做容性负载补偿的链路阻抗,区域1主干道阻抗是40Ω,分支部分阻抗最低约32Ω,区域2平均阻抗大致为34Ω。红色曲线是做容性负载补偿的链路阻抗结果,分支部分刚开始的阻抗趋向50Ω,但会马上下降,分支部分阻抗最低约37Ω, 区域2平均阻抗大致为41Ω。

由上面的纯链路阻抗结果分析可知,信号在分支部分感受到的阻抗会比实际走线阻抗偏低6-10Ω,而容性负载补偿就是将分支部分的阻抗故意抬高,使得链路整体阻抗更趋于匹配。

前面我们只考虑了分支Stub和过孔的影响。除了这些影响因素,芯片封装电容和Die电容也是影响链路阻抗的重要原因,这些因素将导致链路阻抗更低。下面我们接着分析链路增加芯片寄生电容的影响。由于一般芯片的寄生电容值大致在3pF左右,故我们在每一个负载位置挂一个3pF的电容来模拟芯片寄生电容的影响。下面是增加芯片寄生电容前后链路阻抗曲线结果。

由上面两张阻抗曲线结果图来看,芯片寄生电容的影响将导致链路阻抗再降低5Ω左右。没有做容性负载补偿时,信号在分支部分感受到的阻抗只有30Ω。而做了容性负载补偿的链路,信号在分支部分感受到的阻抗大致为35Ω,这可能比主干道的40Ω还是偏差较大,但也是更趋于接近了。

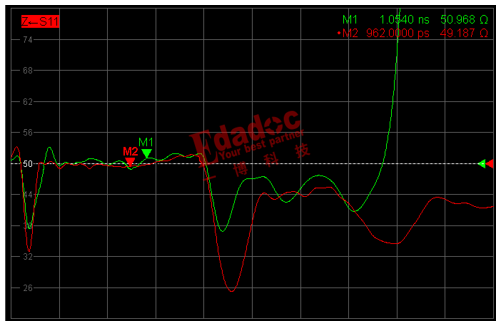

下图是一个DDR一拖三Fly_By链路的阻抗测试结果,主干道和支路走线阻抗都控制在50Ω,没有做容性负载补偿处理。绿色曲线是光板阻抗测试结果,红色曲线是贴了DDR颗粒的阻抗测试结果。可以看出光板情况下分支部分阻抗会比主干道偏低3Ω,而增加了颗粒封装寄生电容的影响,分支部分阻抗只有44Ω,比主干道阻抗偏低6Ω。

由以上测试和仿真结果分析可知,在多负载的Fly_By链路中,由于分支Stub,过孔寄生电容,芯片封装电容和Die电容等因素,导致负载呈容性,使得信号在支路部分感受到的阻抗将会比实际走线阻抗偏低。而容性负载补偿就是事先将支路部分走线阻抗做高,或者将主干线阻抗降低,用以平衡或者抵消容性负载导致阻抗偏低的影响,使得链路整体阻抗更趋近于匹配,从而改善信号质量。

我要赚赏金

我要赚赏金