今天给大侠带来基于FPGA的数字视频信号处理器设计,由于篇幅较长,分三篇。今天带来第一篇,上篇,视频信号概述和视频信号处理的框架。话不多说,上货。

为了方便参考学习,后篇这里也放上超链接:

基于FPGA的数字视频信号处理器设计(中)

基于FPGA的数字视频信号处理器设计(下)

之前也有图像处理相关方面的文章,这里超链接几篇,给各位大侠作为参考。

《冈萨雷斯数字图像处理MATLAB版》中文版(第二版) 电子版

荐读:FPGA设计经验之图像处理

FPGA设计中 Verilog HDL实现基本的图像滤波处理仿真

导读

图像是用各种观测系统以不同形式和手段观测客观世界而获得的,可以直接或间接作用于人眼进而产生视知觉的实体。

随着电子技术和计算机技术的飞速发展,数字图像技术近年来得到极大的重视和长足的发展,并在科学研究、工业生产、医疗卫生、通信等方面得到广泛的应用。

视频信号由一系列连续的图像组成。对视频信号的处理已经成为数字图像处理领域中重要的一部分。例如机器人模式识别的过程就是一个视频信号处理的过程,电视制导导弹识别目标就是充分利用视频信号处理技术不断判断目标是否和预先设定目标图像一致。本篇将讲解如何用 FPGA 技术实现基本的视频信号处理。本篇的例子可以作为各位大侠进行视频信号处理时的一个参考,也可以在这个基础上根据需要进行扩展。

第一篇内容摘要:本篇会介绍视频信号概述,包括视频信号处理的基本过程、数字图像处理技术概念、数字视频信号的格式;视频信号处理的框架,包括视频信号转换模块、视频数据计算模块以及通信模块等相关内容。

在讲解数字视频信号处理器以前,需要了解视频信号的组成。摄像头输出的视频信号满足电视信号的制式,一般摄像头、摄像机都提供 PAL 制的视频信号。

目前,世界上实际应用的电视信号制式主要有 NTSC 制、PAL 制和 SECAM 制 3 种。世界上大多数国家采用 PAL 制,我国也采用 PAL 制。美国、日本等国家采用 NTSC 制。俄罗斯、法国、埃及等少数国家采用 SECAM 制。

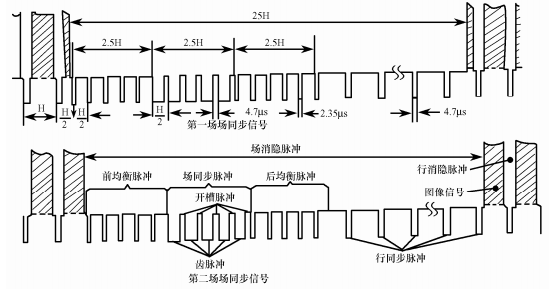

PAL 电视制式规定,场扫描频率为 50Hz,每帧图像的扫描行数为 625 行。PAL 制电视信号如图 1 所示。

电视信号由“图像信号”和确保扫描同步的“复合同步信号”以及消除扫描逆程回扫线的“复合消隐信号”等辅助信号构成。有关电视信号的原理请自行查阅相关资料,这里不详细解释。

1.1 视频信号处理的基本过程

视频信号的处理过程就是拍摄视频信号的逆过程。摄像头输出的是标准 PAL 制电视信号。摄像头通过光电转换实现图像到视频信号的转换,也就是扫描的过程。摄像头每扫描完一行图像,加入一个行同步脉冲,每扫描完一场图像加入一个场同步信号。同时为了保证扫描逆程光栅不显示,应加入和同步信号同周期的消隐信号。

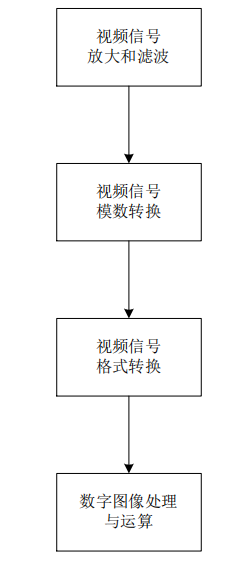

对视频信号进行处理,需要先进行 A/D 转换、行/场同步信号的分离等步骤,然后采用专用的视频信号处理器对视频信号进行转换,最后用FPGA 处理数字图像信号并得到需要的结果。视频信号处理流程如图 2 所示。

图 2 视频信号处理基本流程

如图 2 所示的流程中,视频信号的放大、模数转换和格式转换由专用的视频处理芯片完成,FPGA 需要完成对视频信号转化后的数字图像进行处理和运算。在进行具体的开发前先介绍一下相关的概念。

1)像素

一幅平面图像可以看成是由许许多多的小单元组成,在图像处理系统中,这些组成画面的细小单元称为像素。像素越小,单位面积上的像素数目就越多,由其构成的图像就越清晰。一幅黑白或者灰度平面图像,表征它的特征参量是亮度。这就是说,组成画面的每个像素,不但有各自确定的几何位置,而且它们各自还呈现着不同的亮度。又由于电视系统传送的是活动图像,因而每个在确定位置上的像素其亮度又随时间不断地变化着,也就是说像素的亮度又是时间的函数。像素亮度既是空间(二维)的函数,同时又是时间的函数。

2)一帧图像

电视系统中把构成一幅图像的各像素传送一遍称为进行了一个帧处理,或称为传送了一帧,每帧图像由许多像素组成。因此组成一幅完整图像也叫做一帧图像。

3)一场图像

PAL 制电视图像是隔行扫描的,即一帧图像分两次扫描,第一次扫描奇数行的图像,第二次扫描偶数行的图像。每次扫描获得的图像称为一场图像,分为奇数场和偶数场。

4)图像的串行传输

根据人的视觉惰性,可把组成一帧图像的各个像素的亮度按一定顺序一个一个地转换成相应的电信号并依次传送出去,接收端再按同样顺序将各个电信号在对应位置上转变成具有相应亮度的像素,这就是图像的串行传输。这种串行传输具有两个特点:

• 要求传送速度快。只有传送迅速,传送时间小于视觉暂留时间,重现图像才会给人以连续无跳动的感觉。

• 传送要准确。每个像素一定要在轮到它传送时才被转换、传送,并被接收方接收。而且收、发双方每个像素被转换、还原的几何位置要一一对应。即收发双方应同步工作,同步在电视系统中是十分重要的。

5)扫描

将组成一帧图像的像素,按顺序转换成电信号的过程(或逆过程)称为扫描。扫描的过程和我们读书时视线从左到右、自上而下依次进行的过程类似。从左至右的扫描称为行扫描,自上而下的扫描称为帧或者场扫描。电视系统中,扫描多是由电子枪进行的,通常称其为电子扫描。通过电子扫描与光电转换,就可以把反映一幅图像亮度的空间与时间的函数转换为只随时间变化的单值函数(电信号),从而实现平面图像的顺序传送。

1.3 数字视频信号的格式

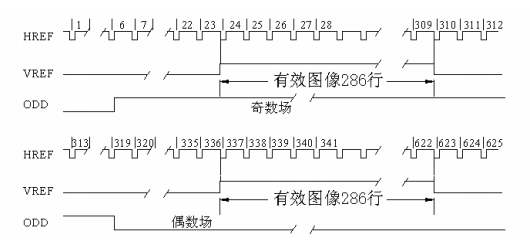

PAL 制电视信号转化为数字视频信号后的具体格式如图 3 所示,一般数据格式符合 ITU656 YUV 4:2:2 标准(在后面的将结合数字视频处理器对数字视频格式详细介绍)。

图 3 一帧图像采集的时序关系一帧图像含有 625 行数据,其中有效图像数据 572 行,其他为场消隐信号;每行图像数据包含 720 个像素。因此,PAL 制电视信号的分辨率为 720×572。PAL 制电视信号每秒扫描 25帧图像,每帧包括奇、偶两场图像。

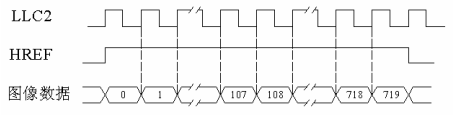

一帧图像分为奇数场和偶数场,每场各有 286 行有效图像。垂直参考电压信号 VREF 的高电平表示有效图像信号,偶数场和奇数场各 286 行。ODD 信号高电平表示为奇数场,低电平表示偶数场。行参考电压信号 HREF 信号表示一行有效的图像数据。一行图像数据又包括 720 个像素的数据,每行图像数据如图 4 所示。

图 4 一行图像数据

二、视频信号处理的框架

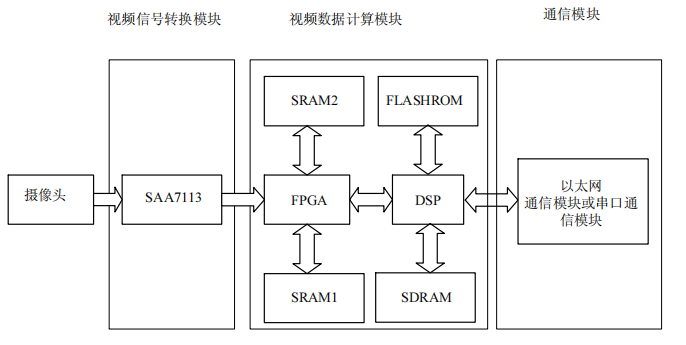

如图 5 所示的是一般工程项目中视频信号处理的框架,由 3 个模块组成:

• 视频信号转换模块

由视频信号处理器完成视频信号从模拟信号到数字信号的转换、图像信号与其他的分离、视频信号的格式转换等,最终提供后端可以处理的数字视频数据。

• 视频数据计算模块

首先接收来自前一个模块的数字视频数据,然后完成对数字视频数据的计算。一般数据接收由 FPGA 完成,根据需要可以选择专用芯片,如 DSP(Digital SignalProcessor,数字信号处理器)完成计算,也可以选择 FPGA。

• 通信模块

实现与外界的数据交换。

图 5 视频信号处理框架

虽然视频信号处理的需求多种多样,但数据处理的流程都遵循数据采集、格式转换、数据接收、数据计算、数据通信的步骤。

2.1 视频信号转换模块

视频信号转换模块由视频信号处理器及其辅助电路组成。这个模块的设计要点是选择视频信号处理器。电视信号构成极为复杂,其中除了包含图像信号之外,还包含行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等。因而,对电视信号进行 A/D 转换的电路也非常复杂,Philips 公司将这些非常复杂的电视 A/D 转换电路集成到了一块芯片内,生产出功能强大的视频输入处理芯片 SAA7113(后面简称 SAA7113)。

SAA7113 采用 CMOS 工艺,通过简洁的 I2C 总线与采样控制器连接可方便地构成图像采集系统。SAA7113 芯片中的场同步信号、行同步信号、像素时钟信号 LLC2 以及其他状态信号都可直接由管脚引出,省去了时钟同步电路的设计,而且可靠性更高。系统内部采用锁相环技术,不但有高的可靠性,并简化了设计复杂度。在 SAA7113 中有控制字可以直接控制行同步有效时间,省略了行延迟电路。因此,采用 SAA7113 可为电视信号的数字化应用提供极大的方便。

2.2 视频数据计算模块

在视频信号处理过程中为保证实时性,首先要求实时图像处理系统具有处理大数据量的能力;其次对系统的体积大小、功能、稳定性等也有严格的要求。实时图像处理算法中经常要用到对图像的求和、求差运算、二维梯度运算、图像分割、边缘探测等不同层次、不同种类的运算。有的运算结构比较简单,但是数据量大,计算速度要求高;有些运算对速度要求并不高,但计算方式和结构比较复杂,难以用纯硬件方式实现。因此,实时图像处理系统是要求运算速度高、运算种类多的综合性信息处理系统。

随着大规模可编程器件的发展,采用 DSP+ASIC(Application Specific IntegratedCircuit,特定用途集成电路)结构的信号处理系统显示出了其优越性,逐步得到重视。与通用集成电路相比,ASIC 芯片具有体积小、重量轻、功耗低、可靠性高等优点,而且在大批量应用时更可降低成本。现场可编程门阵列(FPGA)是在专用 ASIC 的基础上发展起来的,它克服了专用 ASIC 不够灵活的缺点。与其他中小规模集成电路相比,其优点主要在于它的灵活性很强,即其内部具体的逻辑功能可以根据需要配置,对电路的修改和维护很方便。

目前,FPGA的容量已经超过了百万门级,FPGA 已成为系统设计的重要选择方案之一。图像处理系统中,底层的图像预处理的数据量很大,要求处理速度快,但运算结构相对比较简单,适用于 FPGA 通过硬件实现,这样能同时兼顾速度及灵活性。高层运算的特点是所处理的数据量较底层少,但算法结构复杂,适宜采用运算速度高、寻址方式灵活、通信能力强的DSP 芯片来实现。

DSP+FPGA 结构最大的特点是结构灵活,有较强的通用性,适于模块化设计,从而能够提高运算、处理的效率;同时开发周期短,易于维护和扩展,适于实时图像处理;对不同算法有较强的适应能力。

上面的讨论为各位大侠提供视频数据计算的方案。由于本篇主要介绍 FPGA 技术,这里将结合FPGA 介绍如何进行视频数据计算。

2.3 通信模块

通信模块用于提供当前系统与外部进行数据交换的通道,可以有以太网、RS-232、RS-422、RS-485、现场总线、USB 等多种方式。

我要赚赏金

我要赚赏金