STM32的时钟系统

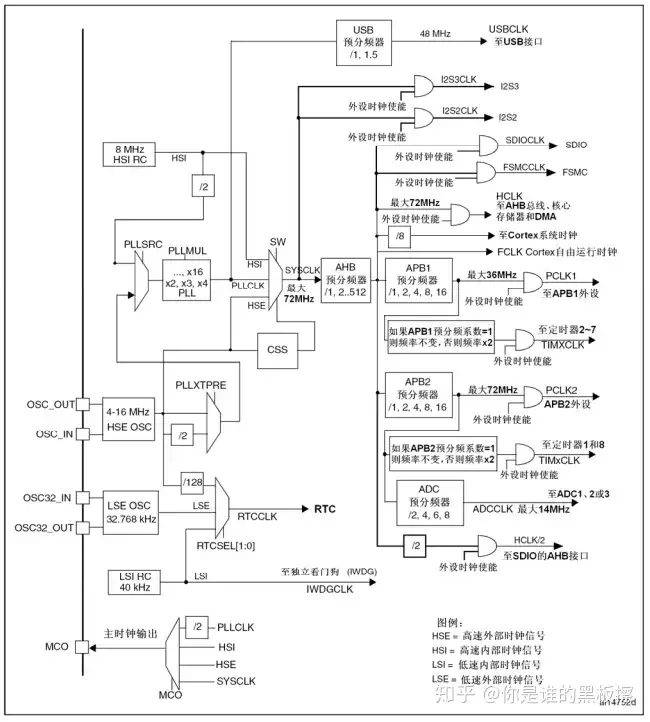

相较于51单片机,stm32的时钟系统可以说是非常复杂了,我们现在看下面的一张图:

上图说明了时钟的走向,是从左至右的从时钟源一步步的分配给外设时钟。需要注意的是,上图左侧一共有四个时钟源,从上到下依次是:

高速内部时钟(HSI):以内部RC振荡器产生,频率为8Mhz,但相较于外部时钟不稳定。

高速内部时钟(HSE):以外部晶振作为时钟源,晶振频率可取范围为4~16Mhz,一般采用8Mhz的晶振。

低速外部时钟(LSE): 以外部晶振作为时钟源,主要是提供给实时时钟模块,所以一般选用32.768khz,该频率下定时器方便取整。

低速内部时钟(LSI): 从内部RC振荡器产生,频率为40khz,也是主要提供给实时时钟模块。

根据上图,以我们最常用的高速外部时钟为例,沿着路线一步步的分析:

从最左端的OSC_OUT和OSC_IN开始,这两个引脚分别连接到外部晶振的两端。

我们假设连接的晶振为8Mhz,它遇到了第一个分频器PLLXTPRE。在这个分频器中,可以选择设置二分频,或者不分频。这里我们选择不分频。

然后箭头指向了开关PLLSRC,这个开关可以选择HSE或者HSI作为其时钟输出。这里我们选择HSE,紧接着又遇到锁相环PLL,也叫倍频器。我们可以设定2到16的倍频因子(PLLMUL),经过PLL的时钟称为PLLCLK。在这里设置倍频因子为9,也就是说乘以9,PLLCLK为72Mhz。

然后又遇到一个开关SW,经过这个开关之后就是STM32的系统时钟(SYSCLK)了。通过这个开关,可以切换SYSCLK的时钟源,有HSI,PLLCLK,HSE三个选择。我们选择PLLCLK时钟,所以SYSCLK就为72Mhz了。

PLLCLK在输入到SW前,还流向了USB预分频器,所以这个PLLCLK也作为USB的时钟。

再继续看SYSCLK,SYSCLK经过AHB预分频器,分频后再输入到其他外设。本例中AHB不分频,直接输入到HCLK,FCLK或者SDIOCLK等时钟。

接下来看最后一层,GPIO外设是挂载在APB2总线上的,APB2总线的时钟来源于APB2预分频器,在APB2预分频器中可以选择/2,/4,/8,/16这几个分频倍数。在这里我选择不分频率,也就是说,GPIO的时钟也为72Mhz

上面这一套流程走下来,经历了一系列的分频和倍频,得到了几个与我们开发密切相关的时钟。

1.SYSCLK:系统时钟,是STM32大部分器件的时钟来源,主要由AHB预分频器分配到各个部件。

2.HCLK:由AHB预分频器直接输出得到,它是高速总线AHB的时钟信号,提供给存储器,DMA及Cortex内核,是Cortex内核运行的时钟,CPU主频就是这个信号。

3.FCLK:也是由AHB输出得到,是内核的“自由运行时钟”。“自由”表现在它不来自时钟HCLK。因此在HCLK停止时FCLK也可以继续运行。也就是说,即使CPU休眠了,也能够采样到外部中断和跟踪休眠事件。低功耗模式下使用。

4.PCLK1:外设时钟,由APB1分频得到,最大可为72Mhz,提供给APB1总线上的外设使用。

5.PCLK2:外设时钟,由APB2预分频输出得到,最大为72Mhz,提供给APB2总线上的外设。

来源: 整理文章为传播相关技术,网络版权归原作者所有,如有侵权,请联系删除。

我要赚赏金

我要赚赏金