01 使用LDO稳压器

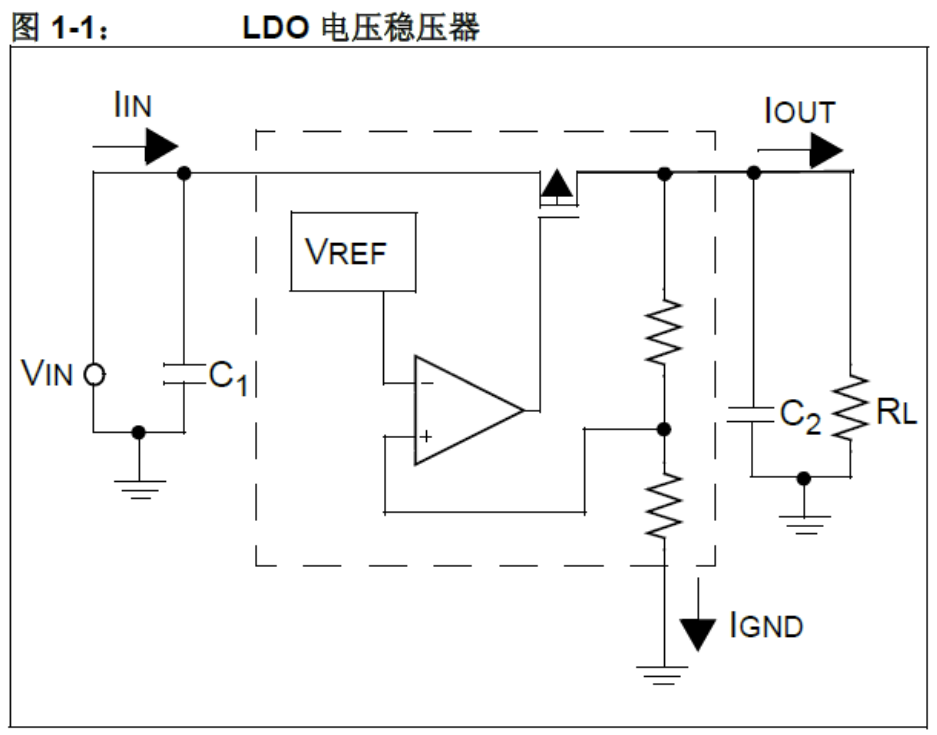

标准三端线性稳压器的压差通常是 2.0-3.0V。要把 5V 可靠地转换为 3.3V,就不能使用它们。压差为几百个毫伏的低压降 (Low Dropout, LDO)稳压器,是此类应用的理想选择。图 1-1 是基本LDO 系统的框图,标注了相应的电流。

从图中可以看出, LDO 由四个主要部分组成:

导通晶体管

带隙参考源

运算放大器

反馈电阻分压器

在选择 LDO 时,重要的是要知道如何区分各种LDO。器件的静态电流、封装大小和型号是重要的器件参数。根据具体应用来确定各种参数,将会得到最优的设计。

LDO的静态电流IQ是器件空载工作时器件的接地电流 IGND。IGND 是 LDO 用来进行稳压的电流。当IOUT>>IQ 时, LDO 的效率可用输出电压除以输入电压来近似地得到。然而,轻载时,必须将 IQ 计入效率计算中。具有较低 IQ 的 LDO 其轻载效率较高。轻载效率的提高对于 LDO 性能有负面影响。静态电流较高的 LDO 对于线路和负载的突然变化有更快的响应。

02 采用齐纳二极管的低成本方案 这里详细说明了一个采用齐纳二极管的低成本稳压器方案。

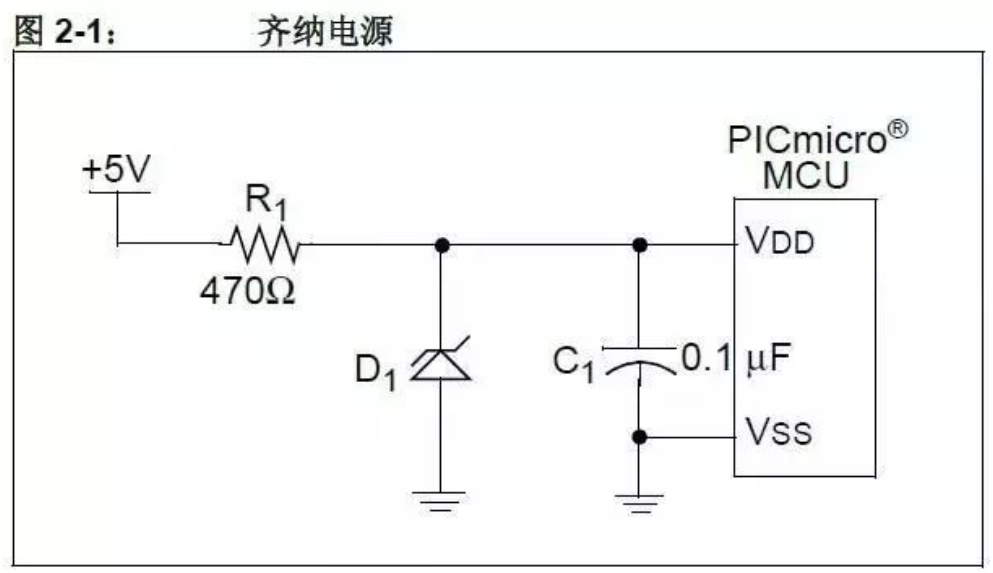

可以用齐纳二极管和电阻做成简单的低成本 3.3V稳压器,如图 2-1 所示。在很多应用中,该电路可以替代 LDO 稳压器并具成本效益。但是,这种稳压器对负载敏感的程度要高于 LDO 稳压器。另外,它的能效较低,因为 R1 和 D1 始终有功耗。R1 限制流入D1 和 PICmicro MCU的电流,从而使VDD 保持在允许范围内。由于流经齐纳二极管的电流变化时,二极管的反向电压也将发生改变,所以需要仔细考虑 R1 的值。

R1 的选择依据是:在最大负载时——通常是在PICmicro MCU 运行且驱动其输出为高电平时——R1上的电压降要足够低从而使PICmicro MCU有足以维持工作所需的电压。同时,在最小负载时——通常是 PICmicro MCU 复位时——VDD 不超过齐纳二极管的额定功率,也不超过 PICmicro MCU的最大 VDD。

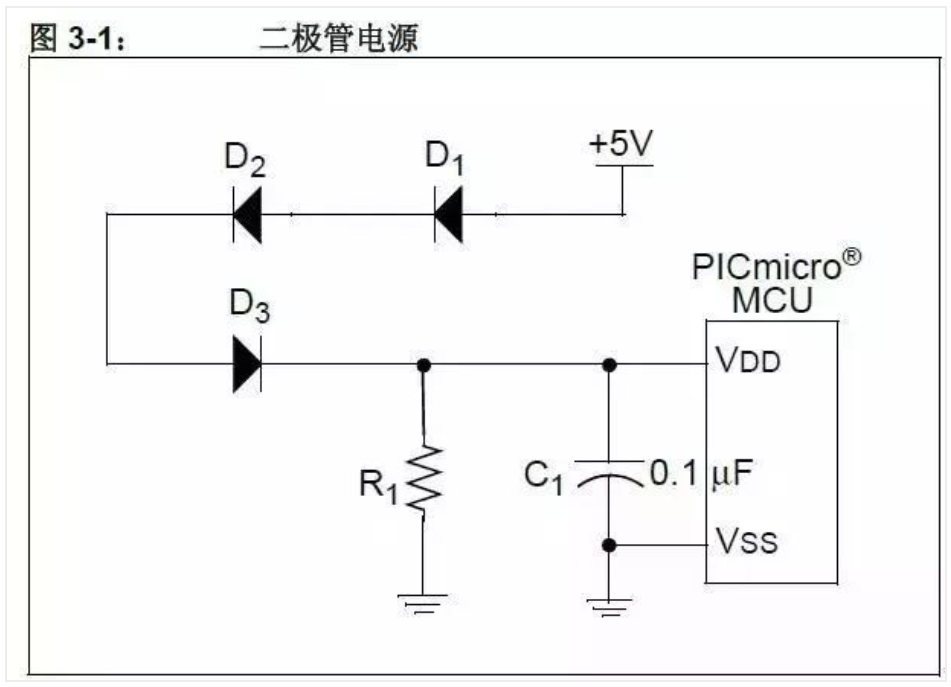

03 采用3个整流二极管的更低成本方案 图 3-1 详细说明了一个采用 3 个整流二极管的更低成本稳压器方案。

我们也可以把几个常规开关二极管串联起来,用其正向压降来降低进入的 PICmicro MCU 的电压。这甚至比齐纳二极管稳压器的成本还要低。这种设计的电流消耗通常要比使用齐纳二极管的电路低。

所需二极管的数量根据所选用二极管的正向电压而变化。二极管 D1-D3 的电压降是流经这些二极管的电流的函数。连接 R1 是为了避免在负载最小时——通常是 PICmicro MCU 处于复位或休眠状态时——PICmicro MCU VDD 引脚上的电压超过PICmicro MCU 的最大 VDD 值。根据其他连接至VDD 的电路,可以提高R1 的阻值,甚至也可能完全不需要 R1。二极管 D1-D3 的选择依据是:在最大负载时——通常是 PICmicro MCU 运行且驱动其输出为高电平时——D1-D3 上的电压降要足够低从而能够满足 PICmicro MCU 的最低 VDD 要求。

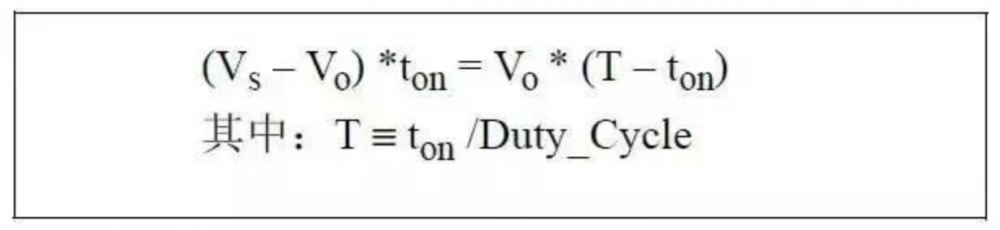

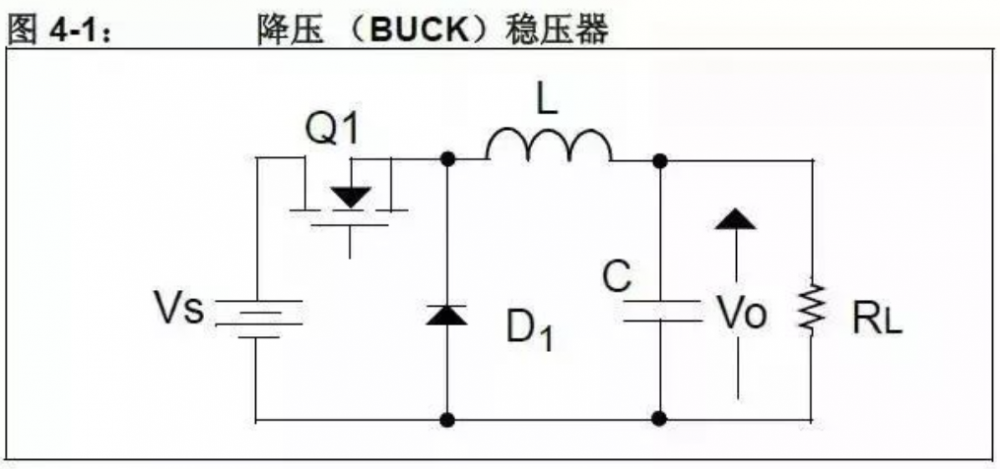

04 使用开关稳压器 如图 4-1 所示,降压开关稳压器是一种基于电感的转换器,用来把输入电压源降低至幅值较低的输出电压。输出稳压是通过控制 MOSFET Q1 的导通(ON)时间来实现的。由于 MOSFET 要么处于低阻状态,要么处于高阻状态(分别为 ON 和OFF),因此高输入源电压能够高效率地转换成较低的输出电压。

当 Q1 在这两种状态期间时,通过平衡电感的电压- 时间,可以建立输入和输出电压之间的关系。

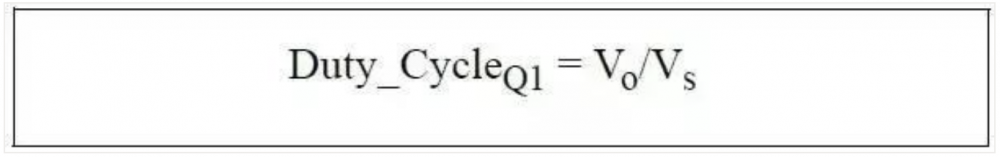

对于 MOSFET Q1,有下式:

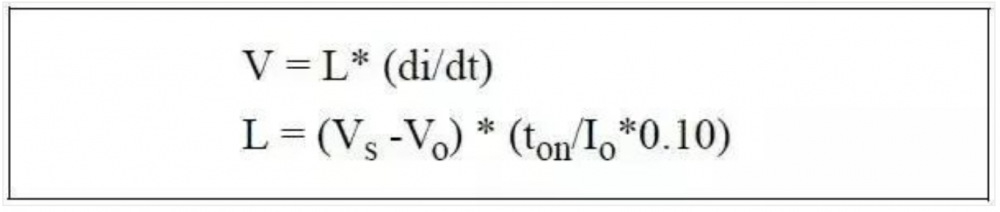

在选择电感的值时,使电感的最大峰 - 峰纹波电流等于最大负载电流的百分之十的电感值,是个很好的初始选择。

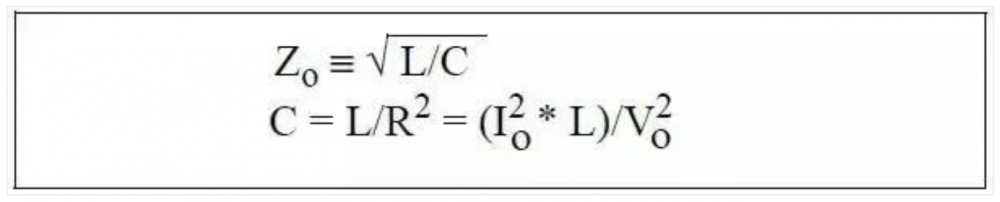

在选择输出电容值时,好的初值是:使 LC 滤波器特性阻抗等于负载电阻。这样在满载工作期间如果突然卸掉负载,电压过冲能处于可接受范围之内。

在选择二极管 D1 时,应选择额定电流足够大的元件,使之能够承受脉冲周期 (IL)放电期间的电感电流。

在连接两个工作电压不同的器件时,必须要知道其各自的输出、输入阈值。知道阈值之后,可根据应用的其他需求选择器件的连接方法。表 4-1 是本文档所使用的输出、输入阈值。在设计连接时,请务必参考制造商的数据手册以获得实际的阈值电平。

05 3.3V→5V直接连接 将 3.3V 输出连接到 5V 输入最简单的方法是直接连接,但直接连接需要满足以下 2 点要求:

3.3V输出的 VOH 大于 5V 输入的 VIH

3.3V输出的 VOL 小于 5V 输入的 VIL

能够使用这种方法的例子之一是将 3.3V LVCMOS输出连接到 5V TTL 输入。从表 4-1 中所给出的值可以清楚地看到上述要求均满足。

3.3V LVCMOS 的 VOH (3.0V)大于5V TTL 的VIH (2.0V)

3.3V LVCMOS 的 VOL (0.5V)小于 5V TTL 的VIL (0.8V)

如果这两个要求得不到满足,连接两个部分时就需要额外的电路。可能的解决方案请参阅技巧 6、7、 8 和 13。

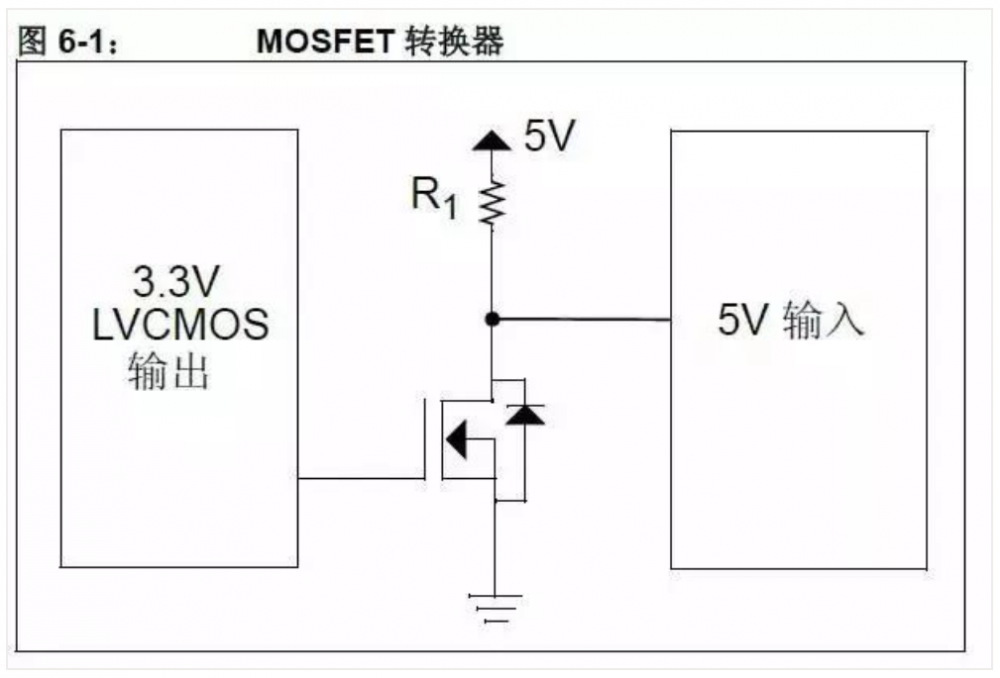

06 使用MOSFET转换器 如果 5V 输入的 VIH 比 3.3V CMOS 器件的 VOH 要高,则驱动任何这样的 5V 输入就需要额外的电路。图 6-1 所示为低成本的双元件解决方案。

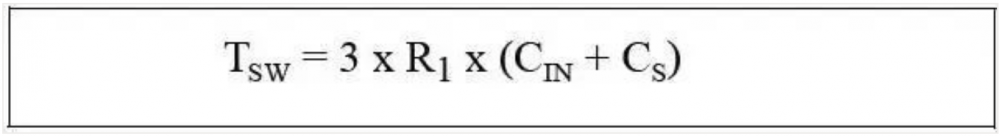

在选择 R1 的阻值时,需要考虑两个参数,即:输入的开关速度和 R1 上的电流消耗。当把输入从 0切换到 1 时,需要计入因 R1 形成的 RC 时间常数而导致的输入上升时间、 5V 输入的输入容抗以及电路板上任何的杂散电容。输入开关速度可通过下式计算:

由于输入容抗和电路板上的杂散电容是固定的,提高输入开关速度的惟一途径是降低 R1 的阻值。而降低 R1 阻值以获取更短的开关时间,却是以增大5V 输入为低电平时的电流消耗为代价的。通常,切换到 0 要比切换到 1 的速度快得多,因为 N 沟道 MOSFET 的导通电阻要远小于 R1。另外,在选择 N 沟道 FET 时,所选 FET 的VGS 应低于3.3V 输出的 VOH。

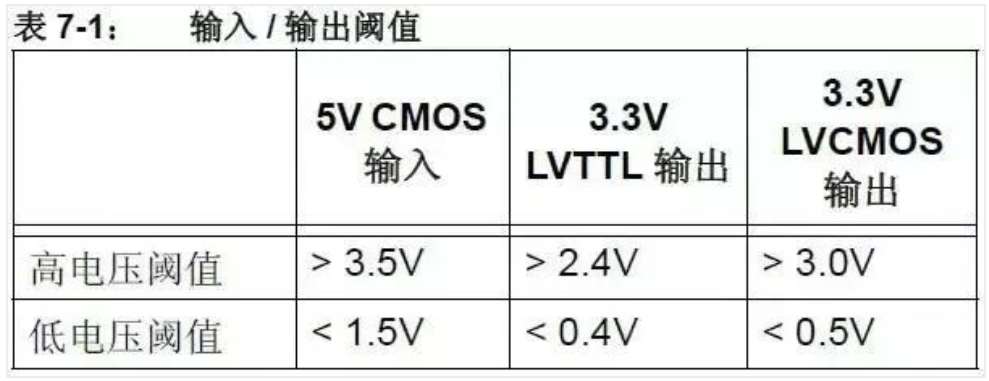

07 使用二极管补偿 表 7-1 列出了 5V CMOS 的输入电压阈值、 3.3VLVTTL 和 LVCMOS 的输出驱动电压。

从上表看出, 5V CMOS 输入的高、低输入电压阈值均比 3.3V 输出的阈值高约一伏。因此,即使来自 3.3V 系统的输出能够被补偿,留给噪声或元件容差的余地也很小或者没有。我们需要的是能够补偿输出并加大高低输出电压差的电路。

输出电压规范确定后,就已经假定:高输出驱动的是输出和地之间的负载,而低输出驱动的是 3.3V和输出之间的负载。如果高电压阈值的负载实际上是在输出和 3.3V 之间的话,那么输出电压实际上要高得多,因为拉高输出的机制是负载电阻,而不是输出三极管。

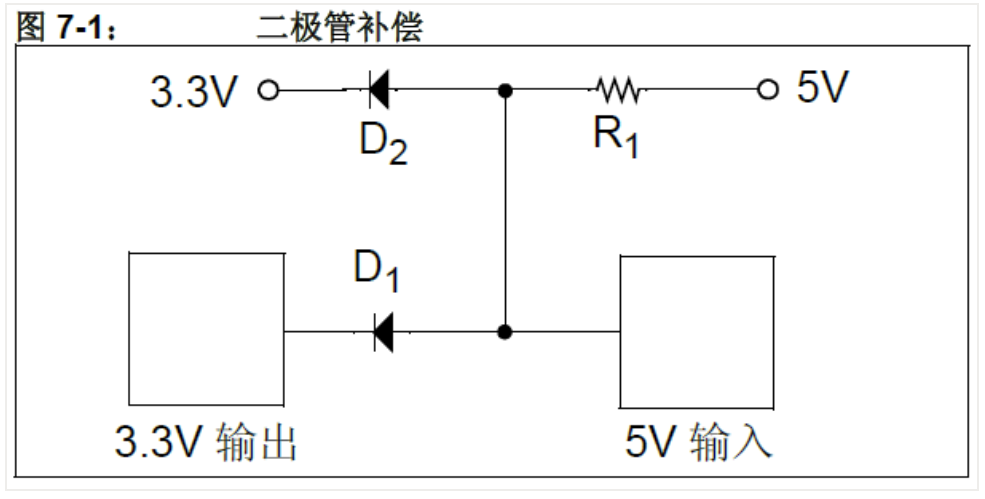

如果我们设计一个二极管补偿电路 (见图 7-1),二极管 D1 的正向电压 (典型值 0.7V)将会使输出低电压上升,在 5V CMOS 输入得到 1.1V 至1.2V 的低电压。它安全地处于 5V CMOS 输入的低输入电压阈值之下。输出高电压由上拉电阻和连至3.3V 电源的二极管 D2 确定。这使得输出高电压大约比 3.3V 电源高 0.7V,也就是 4.0 到 4.1V,很安全地在 5V CMOS 输入阈值 (3.5V)之上。

注:为了使电路工作正常,上拉电阻必须显著小于 5V CMOS 输入的输入电阻,从而避免由于输入端电阻分压器效应而导致的输出电压下降。上拉电阻还必须足够大,从而确保加载在 3.3V 输出上的电流在器件规范之内。

08 使用电压比较器 比较器的基本工作如下:

反相 (-)输入电压大于同相 (+)输入电压时,比较器输出切换到 Vss。

同相 (+)输入端电压大于反相 (-)输入电压时,比较器输出为高电平。

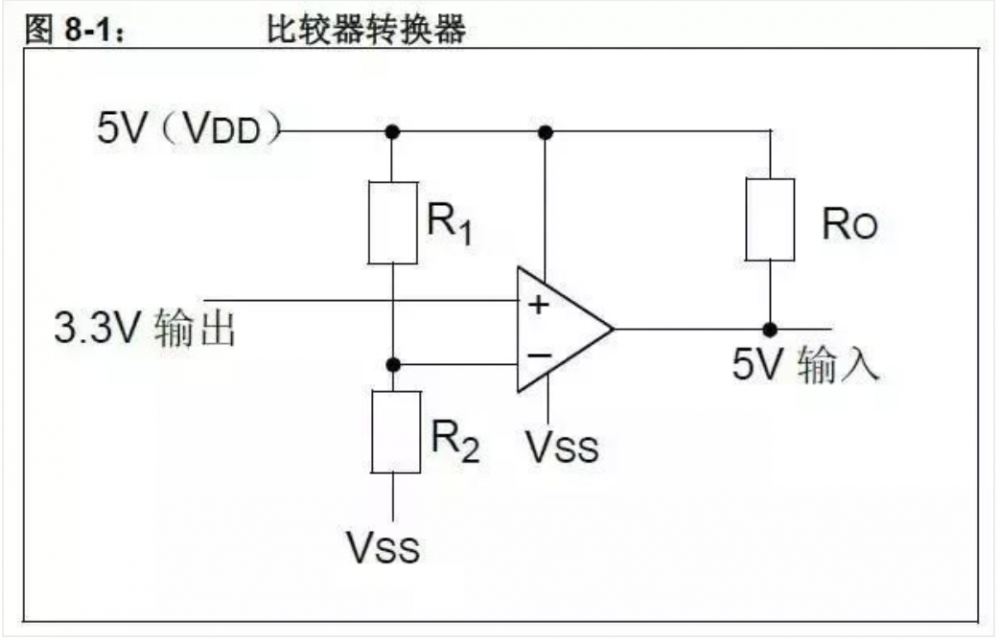

为了保持 3.3V 输出的极性, 3.3V 输出必须连接到比较器的同相输入端。比较器的反相输入连接到由 R1 和 R2 确定的参考电压处,如图 8-1 所示。

R1 和 R2 之比取决于输入信号的逻辑电平。对于3.3V 输出,反相电压应该置于VOL 与VOH之间的中点电压。对于 LVCMOS 输出,中点电压为:

如果 R1 和 R2 的逻辑电平关系如下:

若 R2 取值为 1K,则 R1 为 1.8K。

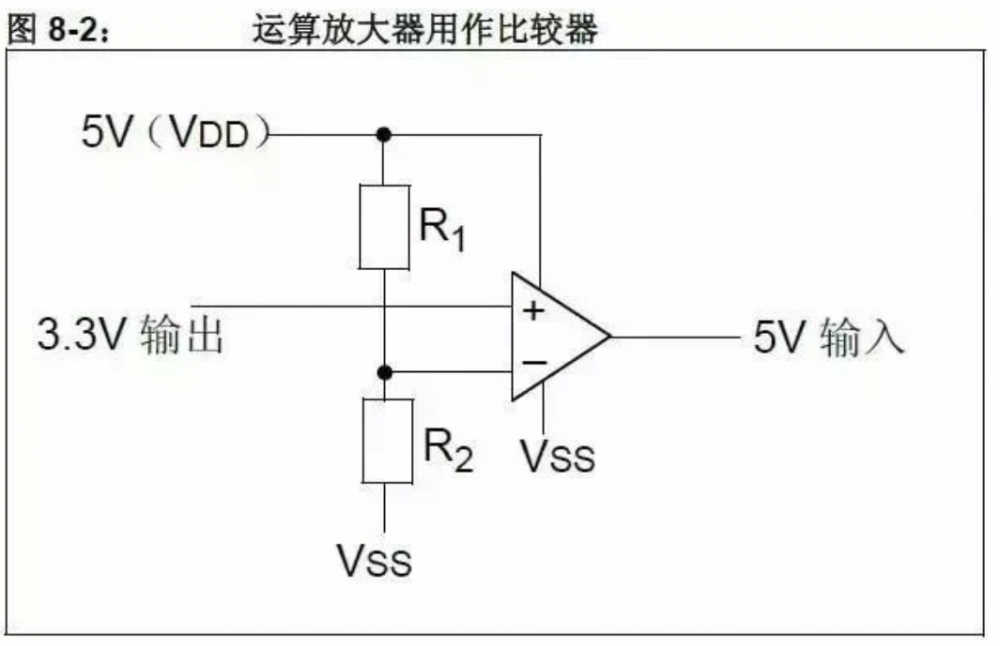

经过适当连接后的运算放大器可以用作比较器,以将 3.3V 输入信号转换为 5V 输出信号。这是利用了比较器的特性,即:根据 “反相”输入与 “同相”输入之间的压差幅值,比较器迫使输出为高(VDD)或低 (Vss)电平。

注:要使运算放大器在 5V 供电下正常工作,输出必须具有轨到轨驱动能力。

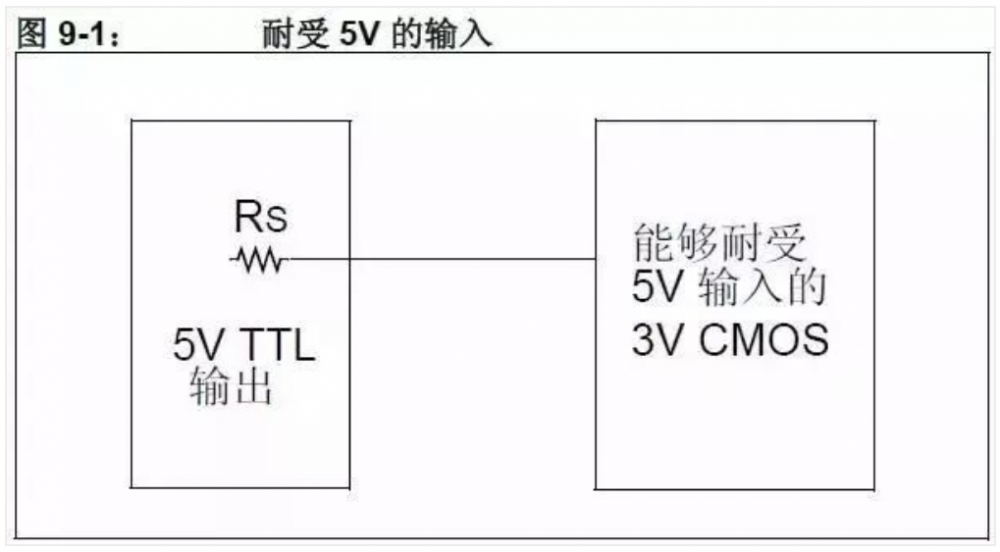

09 直接连接 通常 5V 输出的 VOH 为 4.7 伏, VOL 为 0.4 伏;而通常 3.3V LVCMOS 输入的 VIH 为 0.7 x VDD, VIL为 0.2 x VDD。

当 5V 输出驱动为低时,不会有问题,因为 0.4 伏的输出小于 0.8 伏的输入阈值。当 5V 输出为高时, 4.7 伏的 VOH 大于 2.1 伏 VIH,所以,我们可以直接把两个引脚相连,不会有冲突,前提是3.3V CMOS 输出能够耐受 5 伏电压。

如果 3.3V CMOS 输入不能耐受 5 伏电压,则将出现问题,因为超出了输入的最大电压规范。

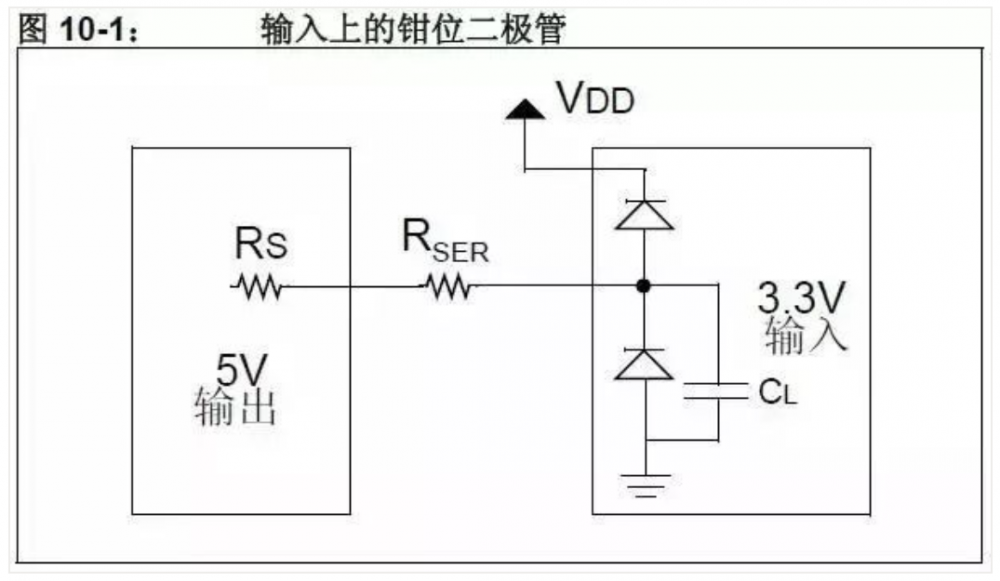

10 使用二极管钳位 很多厂商都使用钳位二极管来保护器件的 I/O 引脚,防止引脚上的电压超过最大允许电压规范。钳位二极管使引脚上的电压不会低于 Vss 超过一个二极管压降,也不会高于 VDD 超过一个二极管压降。要使用钳位二极管来保护输入,仍然要关注流经钳位二极管的电流。流经钳位二极管的电流应该始终比较小 (在微安数量级上)。

如果流经钳位二极管的电流过大,就存在部件闭锁的危险。由于5V 输出的源电阻通常在 10Ω 左右,因此仍需串联一个电阻,限制流经钳位二极管的电流,如图 10-1所示。使用串联电阻的后果是降低了输入开关的速度,因为引脚 (CL)上构成了 RC 时间常数。

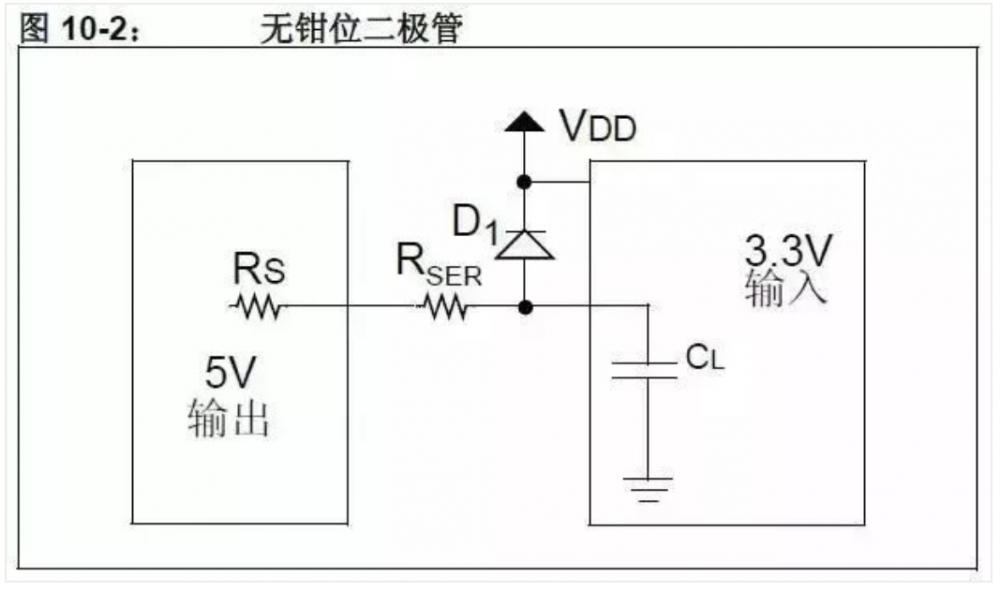

如果没有钳位二极管,可以在电流中添加一个外部二极管,如图 10-2 所示。

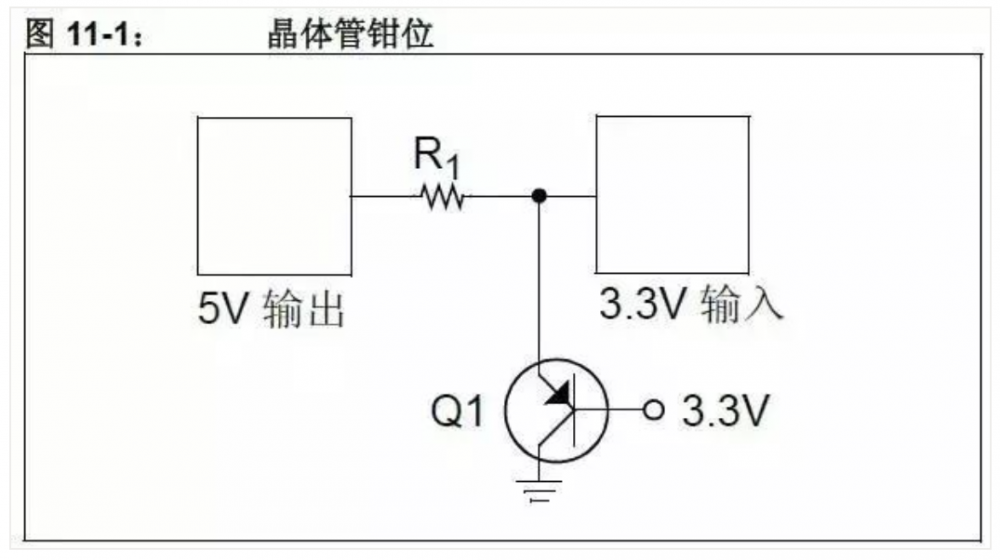

11 5V→3.3V有源钳位 使用二极管钳位有一个问题,即它将向 3.3V 电源注入电流。在具有高电流 5V 输出且轻载 3.3V 电源轨的设计中,这种电流注入可能会使 3.3V 电源电压超过 3.3V。

为了避免这个问题,可以用一个三极管来替代,三极管使过量的输出驱动电流流向地,而不是 3.3V 电源。设计的电路如图 11-1 所示。

Q1的基极-****极结所起的作用与二极管钳位电路中的二极管相同。区别在于,****极电流只有百分之几流出基极进入 3.3V 轨,绝大部分电流都流向集电极,再从集电极无害地流入地。基极电流与集电极电流之比,由晶体管的电流增益决定,通常为10-400,取决于所使用的晶体管。

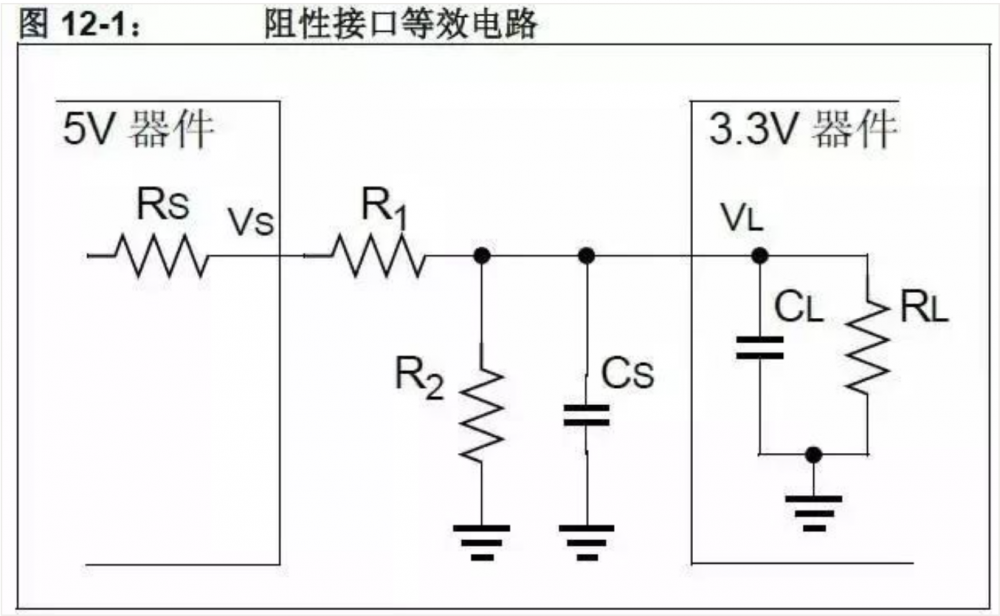

12 电阻分压器 可以使用简单的电阻分压器将 5V 器件的输出降低到适用于 3.3V 器件输入的电平。这种接口的等效电路如图 12-1 所示。

通常,源电阻 RS 非常小 (小于 10Ω),如果选择的 R1 远大于RS 的话,那么可以忽略 RS 对 R1 的影响。在接收端,负载电阻 RL 非常大 (大于500 kΩ),如果选择的R2远小于RL的话,那么可以忽略 RL 对 R2 的影响。

在功耗和瞬态时间之间存在取舍权衡。为了使接口电流的功耗需求最小,串联电阻 R1 和 R2 应尽可能大。但是,负载电容 (由杂散电容 CS 和 3.3V 器件的输入电容 CL 合成)可能会对输入信号的上升和下降时间产生不利影响。如果 R1 和 R2 过大,上升和下降时间可能会过长而无法接受。

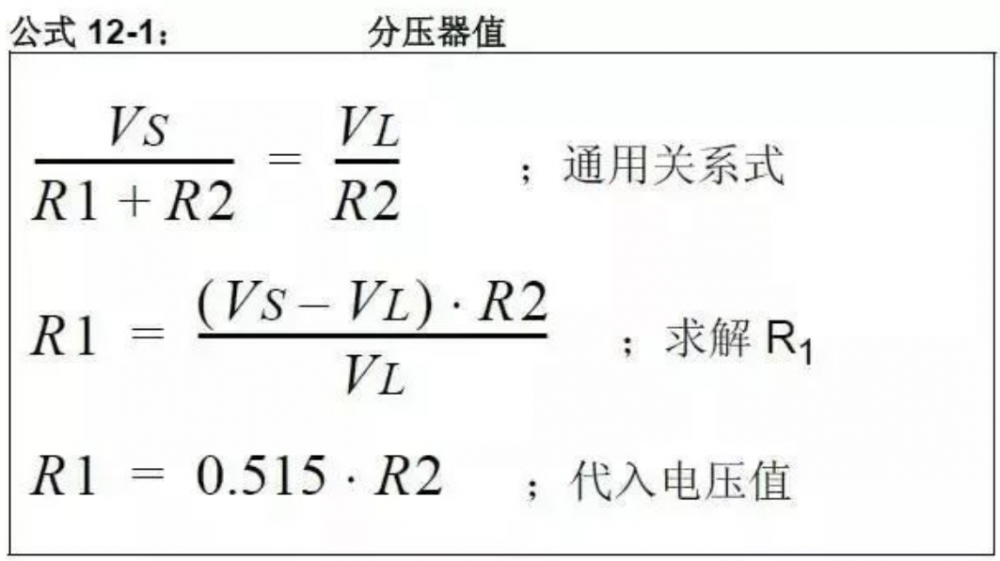

如果忽略 RS 和 RL 的影响,则确定 R1 和 R2 的式子由下面的公式 12-1 给出。

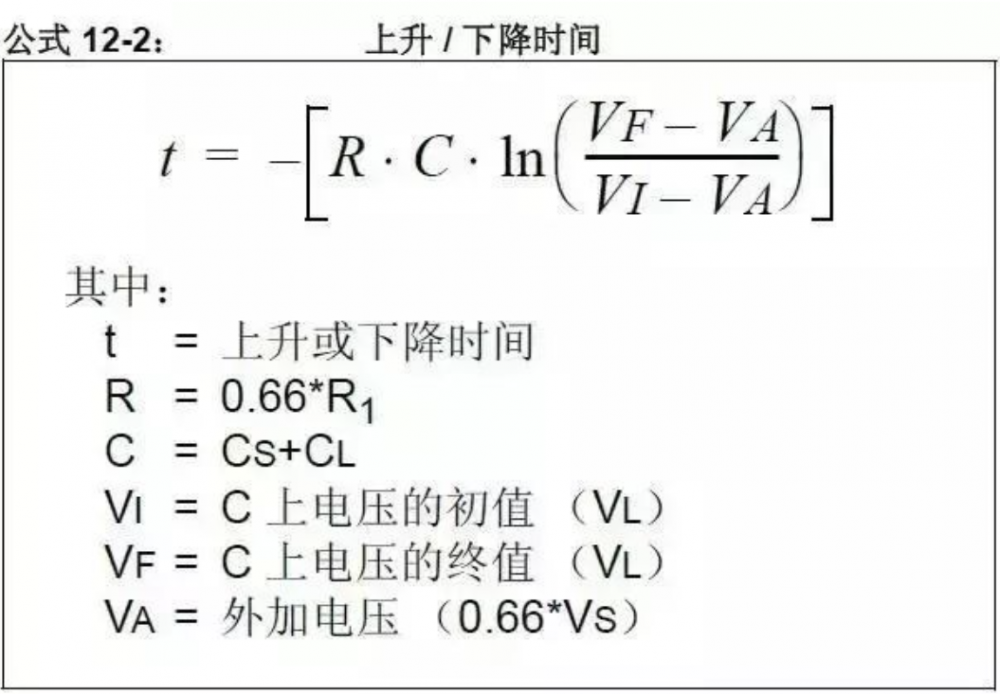

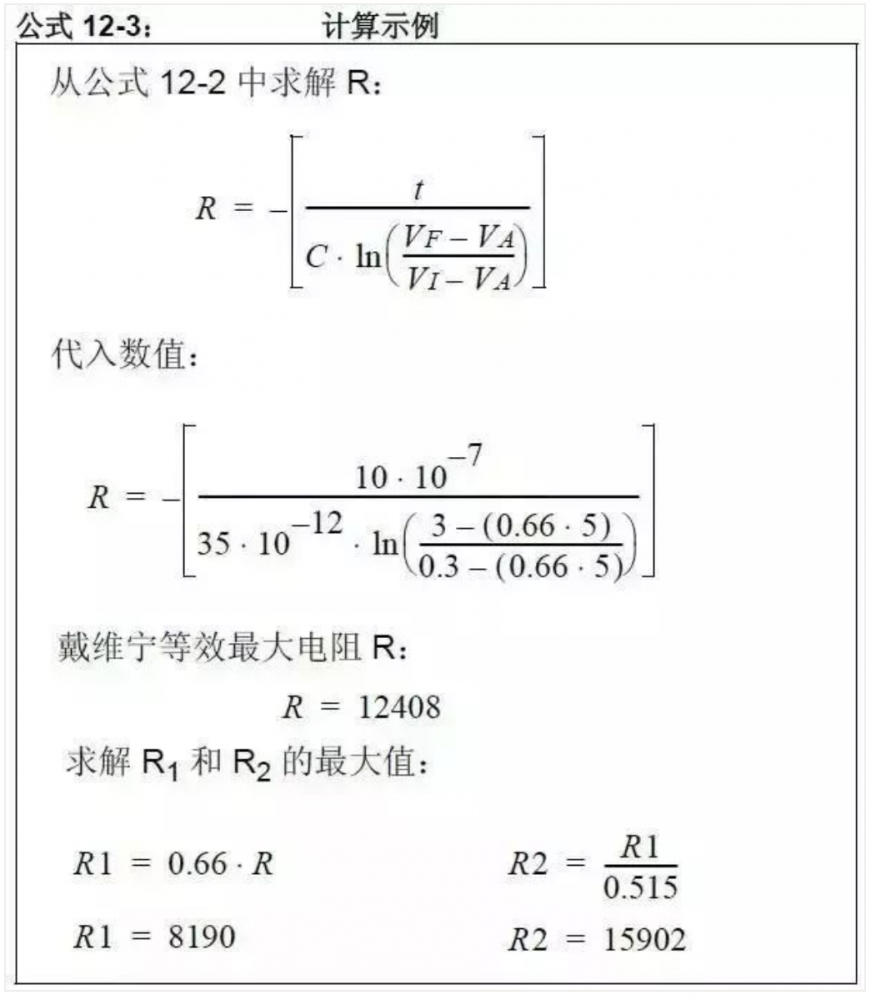

公式 12-2 给出了确定上升和下降时间的公式。为便于电路分析,使用戴维宁等效计算来确定外加电压 VA 和串联电阻R。戴维宁等效计算定义为开路电压除以短路电流。根据公式 12-2 所施加的限制,对于图 12-1 所示电路,确定的戴维宁等效电阻 R 应为 0.66*R1,戴维宁等效电压 VA 应为0.66*VS。

例如,假设有下列条件存在:

杂散电容 = 30 pF

负载电容 = 5 pF

从 0.3V 至 3V 的最大上升时间 ≤ 1 μs

外加源电压 Vs = 5V

确定最大电阻的计算如公式 12-3 所示。

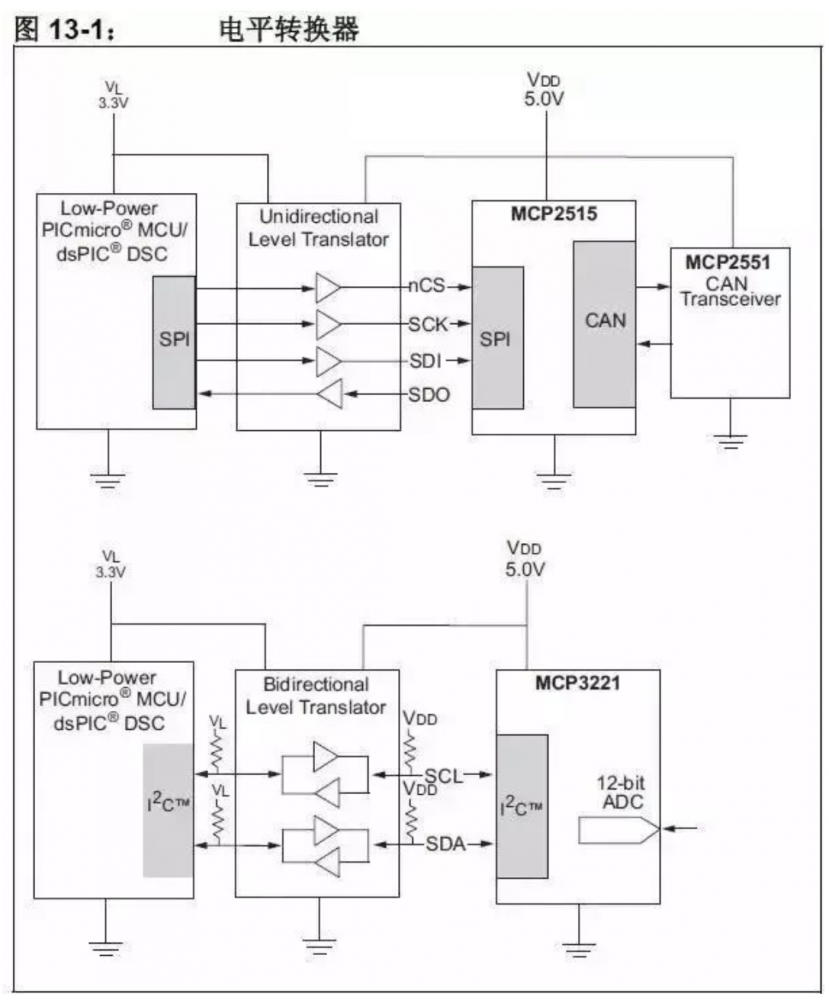

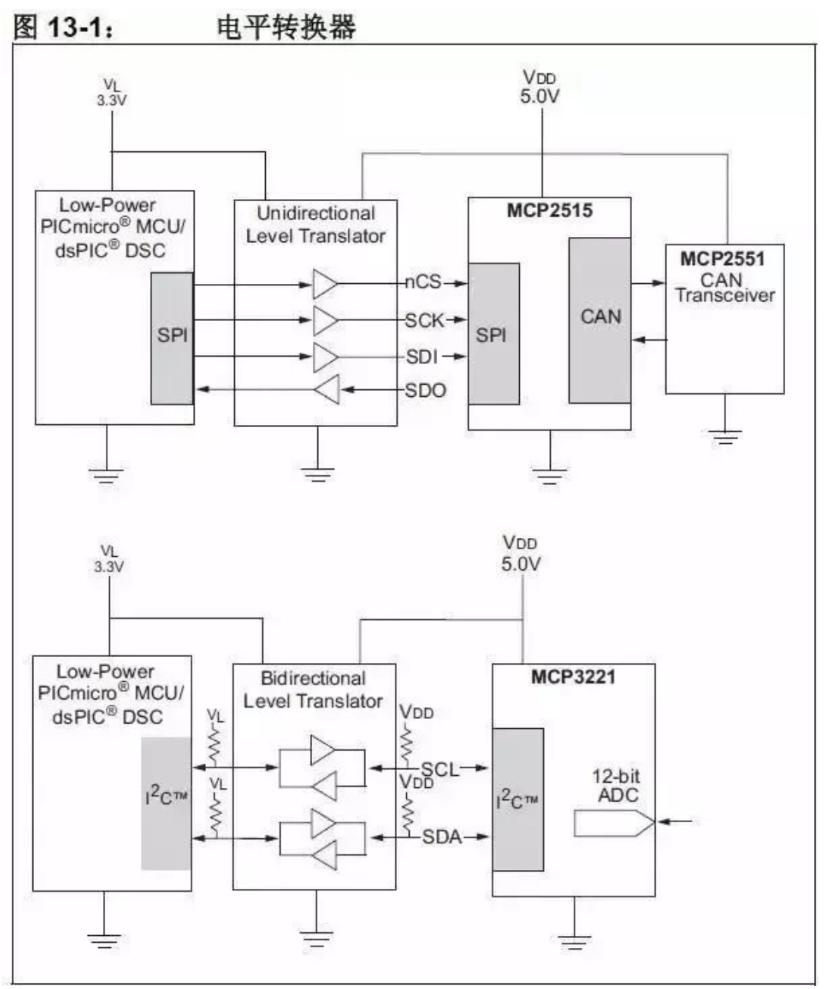

13 电平转换器 尽管电平转换可以分立地进行,但通常使用集成解决方案较受欢迎。电平转换器的使用范围比较广泛:有单向和双向配置、不同的电压转换和不同的速度,供用户选择最佳的解决方案。

器件之间的板级通讯 (例如, MCU 至外设)通过 SPI 或 I2C™ 来进行,这是最常见的。对于SPI,使用单向电平转换器比较合适;对于 I2C,就需要使用双向解决方案。下面的图 13-1 显示了这两种解决方案。

3.3V 至 5V 接口的最后一项挑战是如何转换模拟信号,使之跨越电源障碍。低电平信号可能不需要外部电路,但在 3.3V 与 5V 之间传送信号的系统则会受到电源变化的影响。例如,在 3.3V 系统中,ADC转换1V峰值的模拟信号,其分辨率要比5V系统中 ADC 转换的高,这是因为在 3.3V ADC 中,ADC 量程中更多的部分用于转换。但另一方面,3.3V 系统中相对较高的信号幅值,与系统较低的共模电压限制可能会发生冲突。

因此,为了补偿上述差异,可能需要某种接口电路。本节将讨论接口电路,以帮助缓和信号在不同电源之间转换的问题。

14 模拟增益模块 从 3.3V 电源连接至 5V 时,需要提升模拟电压。33 kΩ 和 17kΩ 电阻设定了运放的增益,从而在两端均使用满量程。11 kΩ 电阻限制了流回 3.3V 电路的电流。

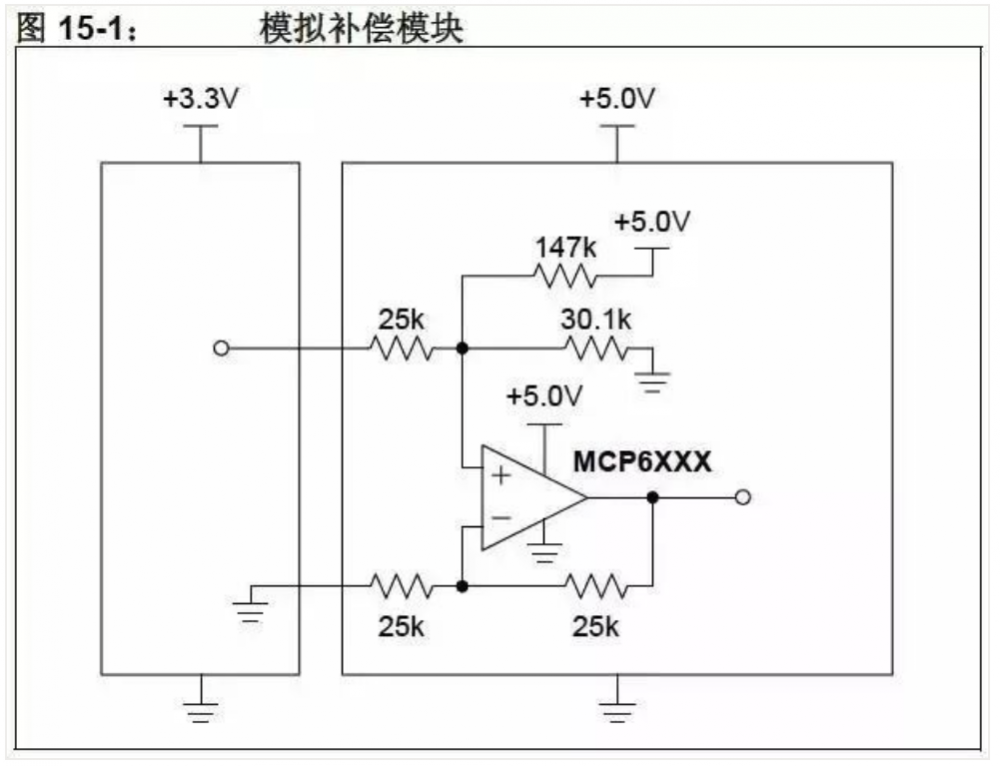

15 模拟补偿模块 该模块用于补偿 3.3V 转换到 5V 的模拟电压。下面是将 3.3V 电源供电的模拟电压转换为由 5V电源供电。右上方的 147 kΩ、 30.1 kΩ 电阻以及+5V 电源,等效于串联了 25 kΩ 电阻的 0.85V 电压源。

这个等效的 25 kΩ 电阻、三个 25 kΩ 电阻以及运放构成了增益为 1 V/V 的差动放大器。0.85V等效电压源将出现在输入端的任何信号向上平移相同的幅度;以 3.3V/2 = 1.65V 为中心的信号将同时以 5.0V/2 = 2.50V 为中心。左上方的电阻限制了来自 5V 电路的电流。

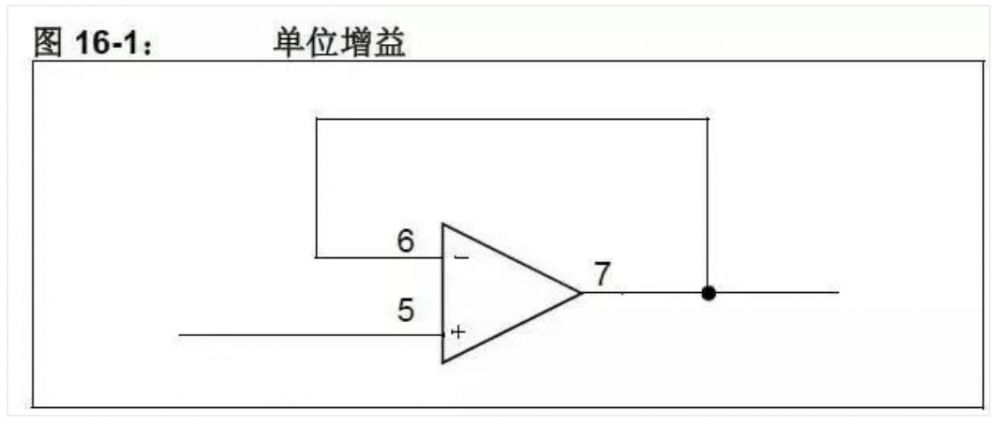

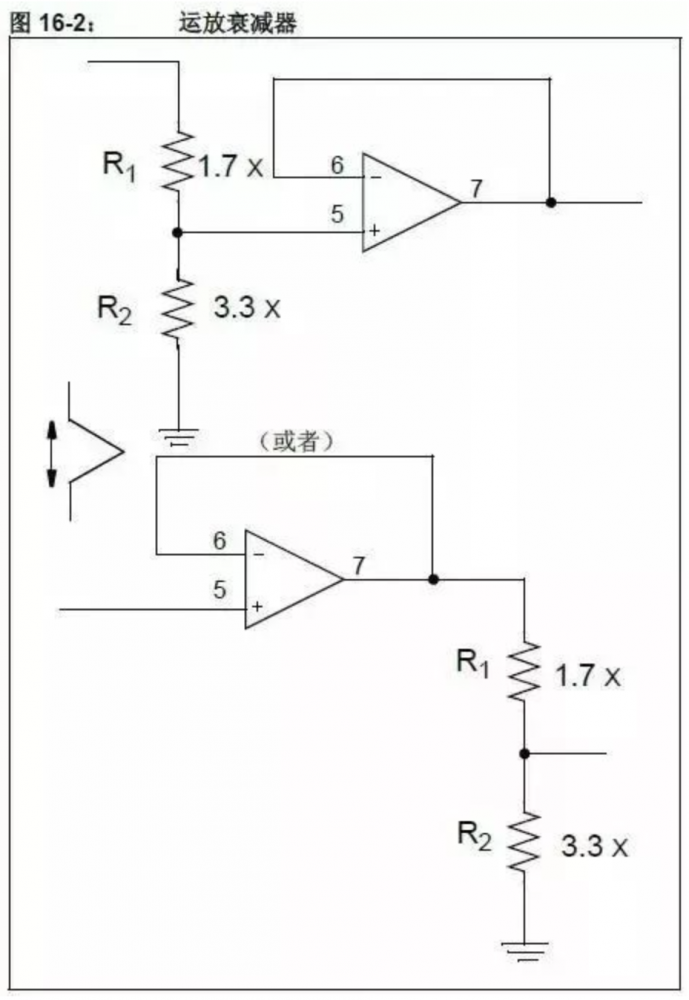

16 有源模拟衰减器 此技巧使用运算放大器衰减从 5V 至 3.3V 系统的信号幅值。

要将 5V 模拟信号转换为 3.3V 模拟信号,最简单的方法是使用 R1:R2 比值为 1.7:3.3 的电阻分压器。

然而,这种方法存在一些问题:

1)衰减器可能会接至容性负载,构成不期望得到的低通滤波器。

2)衰减器电路可能需要从高阻抗源驱动低阻抗负载。

无论是哪种情形,都需要运算放大器用以缓冲信号。所需的运放电路是单位增益跟随器 (见图 16-1)。

电路输出电压与加在输入的电压相同。

为了把 5V 信号转换为较低的 3V 信号,我们只要加上电阻衰减器即可。

如果电阻分压器位于单位增益跟随器之前,那么将为 3.3V 电路提供最低的阻抗。此外,运放可以从3.3V 供电,这将节省一些功耗。如果选择的 X 非常大的话, 5V 侧的功耗可以最大限度地减小。

如果衰减器位于单位增益跟随器之后,那么对 5V源而言就有最高的阻抗。运放必须从 5V 供电,3V 侧的阻抗将取决于 R1||R2 的值。

17 模拟限幅器 在将 5V 信号传送给 3.3V 系统时,有时可以将衰减用作增益。如果期望的信号小于 5V,那么把信号直接送入 3.3V ADC 将产生较大的转换值。当信号接近 5V 时就会出现危险。所以,需要控制电压越限的方法,同时不影响正常范围中的电压。

这里将讨论三种实现方法:

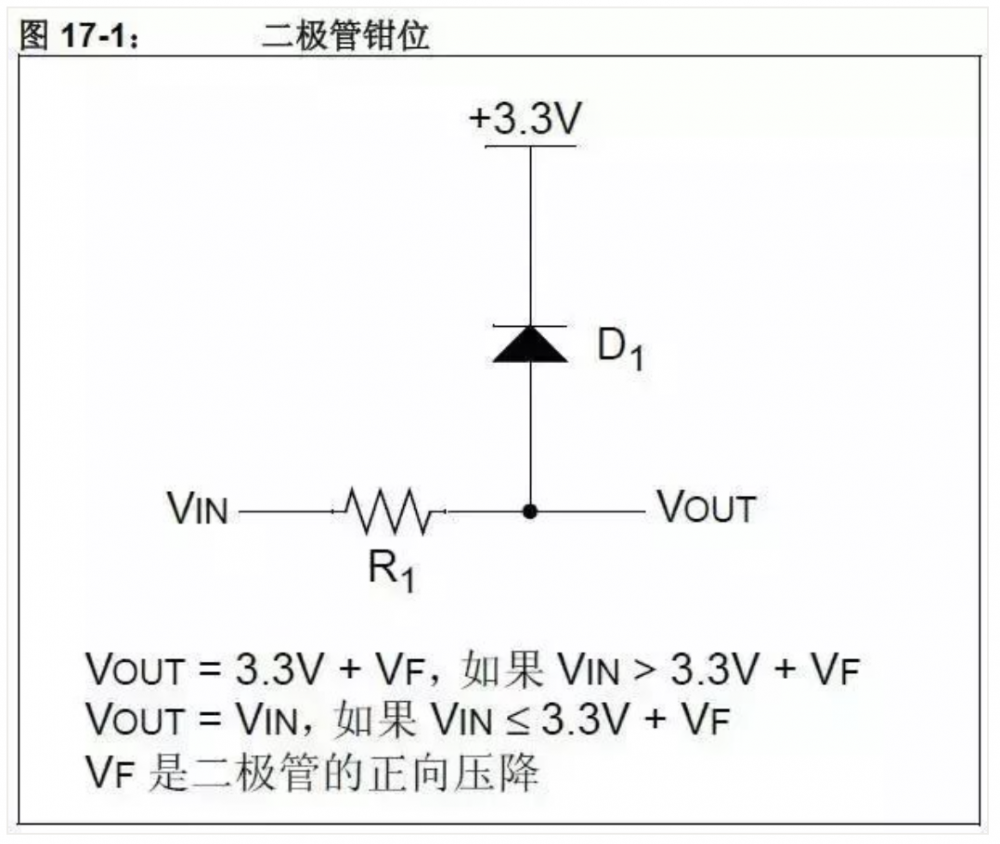

使用二极管,钳位过电压至 3.3V 供电系统。

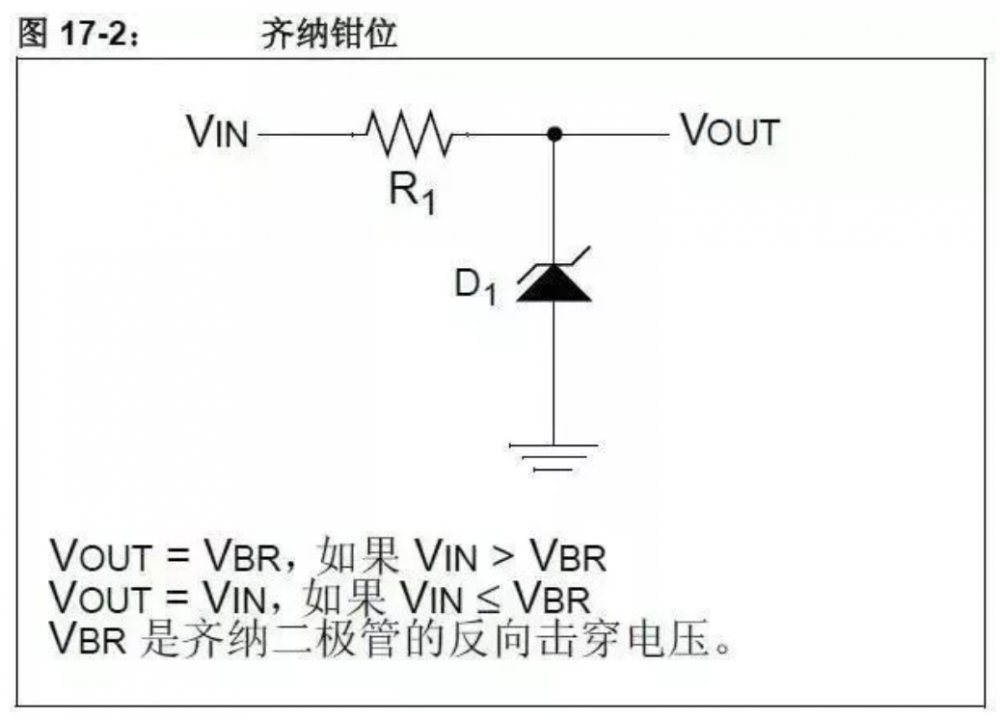

使用齐纳二极管,把电压钳位至任何期望的电压限。

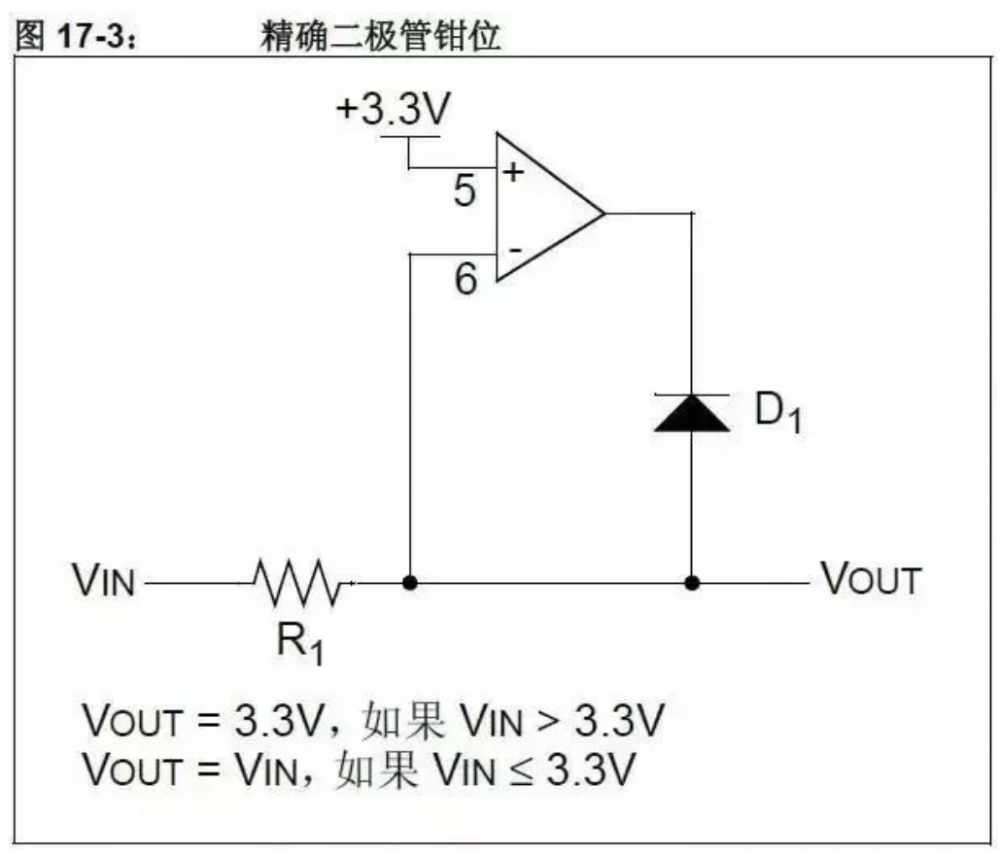

使用带二极管的运算放大器,进行精确钳位。

进行过电压钳位的最简单的方法,与将 5V 数字信号连接至 3.3V 数字信号的简单方法完全相同。使用电阻和二极管,使过量电流流入 3.3V 电源。选用的电阻值必须能够保护二极管和 3.3V 电源,同时还不会对模拟性能造成负面影响。如果 3.3V 电源的阻抗太低,那么这种类型的钳位可能致使3.3V 电源电压上升。即使 3.3V 电源有很好的低阻抗,当二极管导通时,以及在频率足够高的情况下,当二极管没有导通时 (由于有跨越二极管的寄生电容),此类钳位都将使输入信号向 3.3V 电源施加噪声。

为了防止输入信号对电源造成影响,或者为了使输入应对较大的瞬态电流时更为从容,对前述方法稍加变化,改用齐纳二极管。齐纳二极管的速度通常要比第一个电路中所使用的快速信号二极管慢。不过,齐纳钳位一般来说更为结实,钳位时不依赖于电源的特性参数。钳位的大小取决于流经二极管的电流。这由 R1 的值决定。如果 VIN 源的输出阻抗足够大的话,也可不需要 R1。

如果需要不依赖于电源的更为精确的过电压钳位,可以使用运放来得到精密二极管。电路如图 17-3所示。运放补偿了二极管的正向压降,使得电压正好被钳位在运放的同相输入端电源电压上。如果运放是轨到轨的话,可以用 3.3V 供电。

由于钳位是通过运放来进行的,不会影响到电源。

运放不能改善低电压电路中出现的阻抗,阻抗仍为R1 加上源电路阻抗。

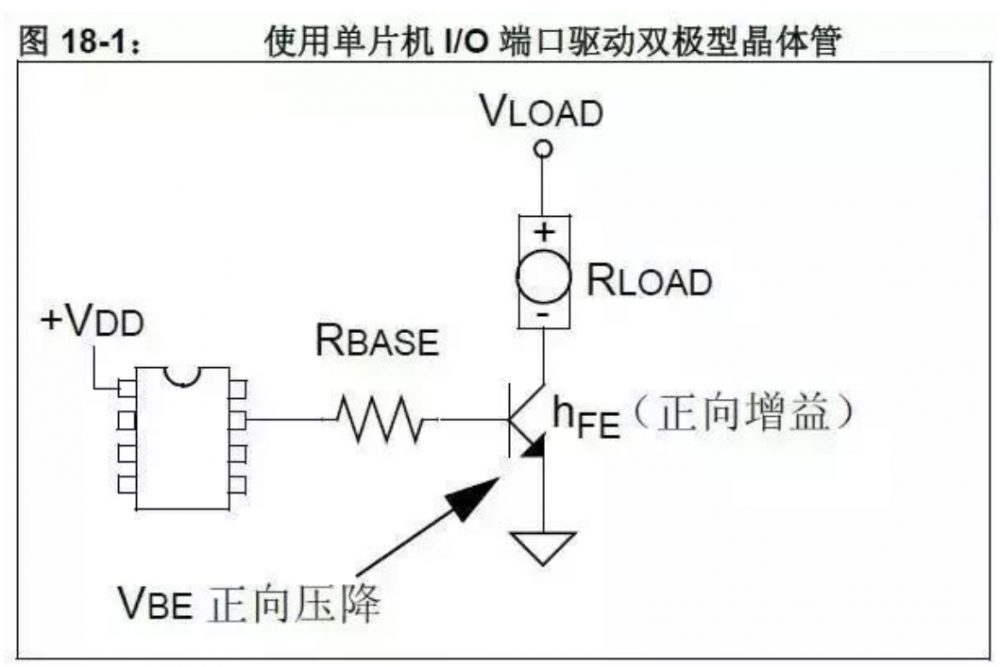

18 驱动双极型晶体管 在驱动双极型晶体管时,基极 “驱动”电流和正向电流增益 (Β/hFE)将决定晶体管将吸纳多少电流。如果晶体管被单片机 I/O 端口驱动,使用端口电压和端口电流上限 (典型值 20 mA)来计算基极驱动电流。如果使用的是 3.3V 技术,应改用阻值较小的基极电流限流电阻,以确保有足够的基极驱动电流使晶体管饱和。

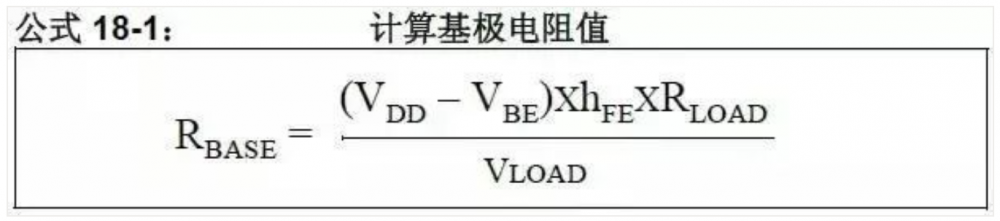

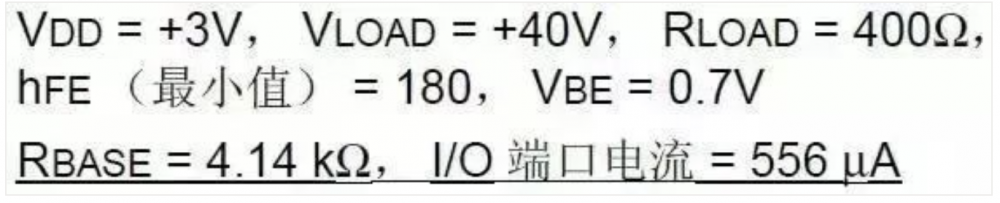

RBASE的值取决于单片机电源电压。公式18-1 说明了如何计算 RBASE。

如果将双极型晶体管用作开关,开启或关闭由单片机 I/O 端口引脚控制的负载,应使用最小的 hFE规范和裕度,以确保器件完全饱和。

▶ 3V 技术示例:

▶ 5V技术示例:

对于这两个示例,提高基极电流留出裕度是不错的做法。将 1mA 的基极电流驱动至 2 mA 能确保饱和,但代价是提高了输入功耗。

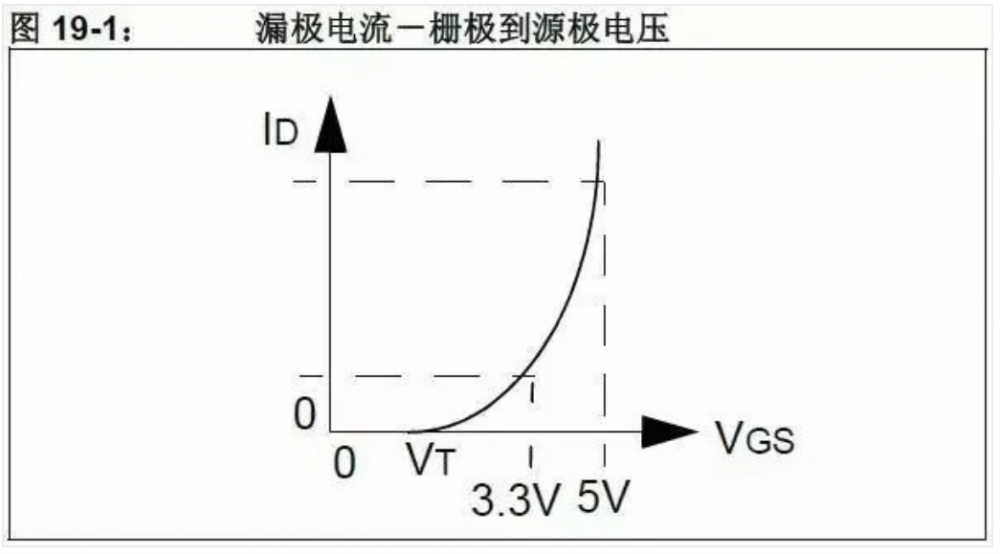

19 驱动N沟道MOSFET晶体管 在选择与 3.3V 单片机配合使用的外部 N 沟道MOSFET 时,一定要小心。MOSFET 栅极阈值电压表明了器件完全饱和的能力。

对于 3.3V 应用,所选 MOSFET 的额定导通电阻应针对 3V 或更小的栅极驱动电压。例如,对于具有 3.3V 驱动的100 mA负载,额定漏极电流为250 μA的FET在栅极 - 源极施加 1V 电压时,不一定能提供满意的结果。在从 5V 转换到 3V 技术时,应仔细检查栅极- 源极阈值和导通电阻特性参数,如图 19-1所示。稍微减少栅极驱动电压,可以显著减小漏电流。

对于 MOSFET,低阈值器件较为常见,其漏-源电压额定值低于 30V。漏-源额定电压大于 30V的 MOSFET,通常具有更高的阈值电压 (VT)。

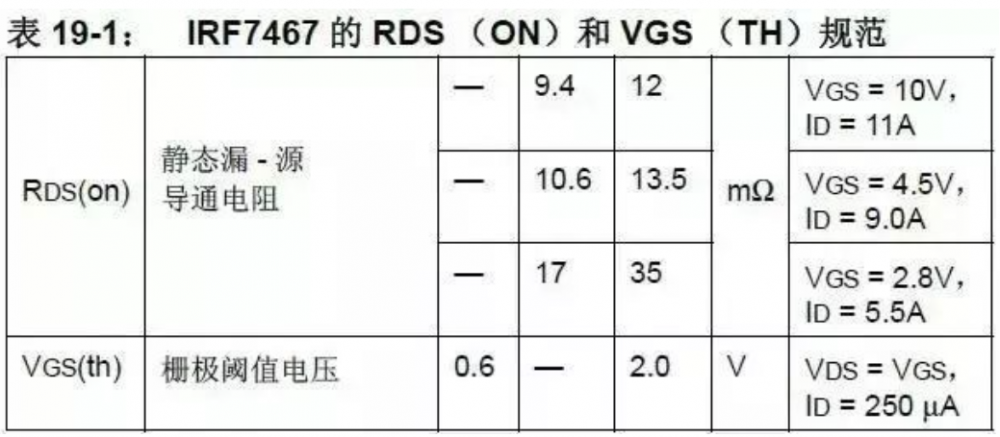

如表 19-1 所示,此 30V N 沟道 MOSFET 开关的阈值电压是 0.6V。栅极施加 2.8V 的电压时,此MOSFET 的额定电阻是 35 mΩ,因此,它非常适用于 3.3V 应用。

对于 IRF7201 数据手册中的规范,栅极阈值电压最小值规定为 1.0V。这并不意味着器件可以用来在1.0V 栅 - 源电压时开关电流,因为对于低于 4.5V 的VGS (th),没有说明规范。对于需要低开关电阻的 3.3V 驱动的应用,不建议使用 IRF7201,但它可以用于 5V 驱动应用。

我要赚赏金

我要赚赏金