在 cyc8kit-5LP 上使用 Del-Sigma A/D 为 8 位,但是当增加到 10 位或更多位时,误差会增加。

我正在使用 UART 向终端显示测量结果

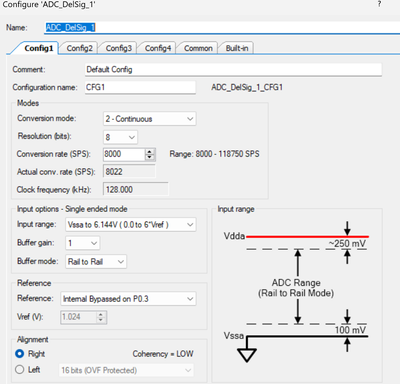

该组件配置为:

如果我的输入电压为 4.002V (精度 +-1mV),

然后用 A/D 吐出 4023 mV。误差在 1LSB 以内。

将 A/D 改为 10 位然后 A/D 给出 4053mV

将 A/D 改为 12 位然后我得到:4061mV

14 位会产生 4063mV。

知道我做错了什么吗?

共2条

1/1 1 跳转至页

PSOC5LPdelta-sigmaA/D误差随位数的增加而增加是为什么?

2楼

当将delta-sigma A/D的位数增加时,误差会增加的原因是由于增加位数会引入更多的量化位,从而对测量结果进行更多的近似。这种近似会导致更大的测量误差。

你说的问题,我认为当将A/D的位数增加时,测量结果会更接近给定的精度范围(+- 1mV),因此误差可能会增加。这是因为增加了位数后,量化的步进大小变得更小,因此近似误差也会增加。

要减小误差,可以考虑以下几点:

1. 使用更高精度的参考电压:如果参考电压的精度较低,那么测量结果的精度也会受到限制。

2. 优化信号链:检查信号传输中是否有任何噪声或干扰的来源,并尽量减小它们的影响。

3. 使用校准技术:通过对A/D进行校准,可以从测量结果中去除系统误差,从而提高精度。

需要注意的是,delta-sigma A/D的位数增加并不总是会导致误差增加。在某些情况下,增加位数可能会提高精度,特别是当信号的动态范围较大时。但在一些情况下,由于近似误差的引入,增加位数可能会导致误差增加。

共2条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |