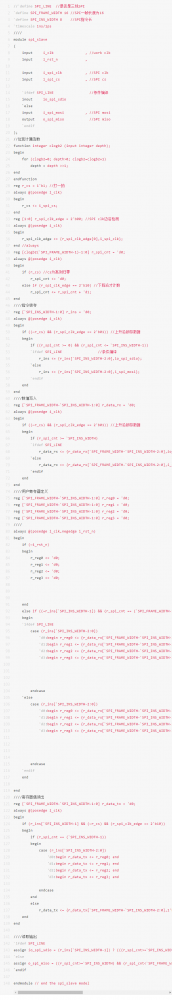

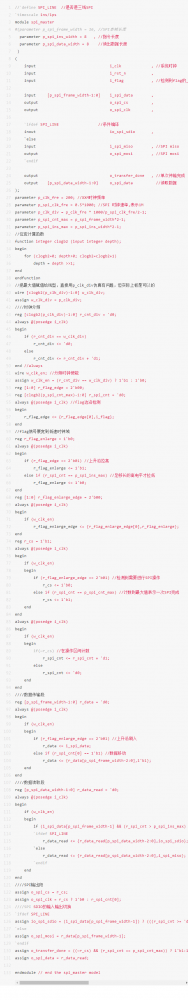

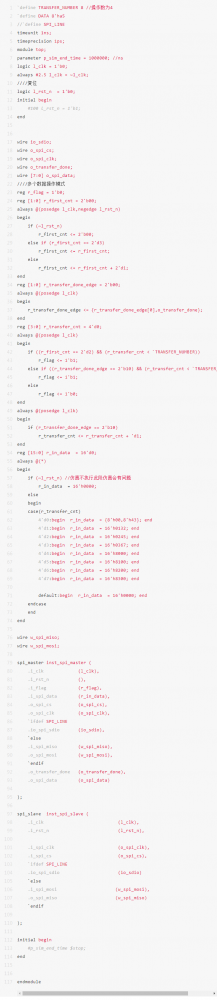

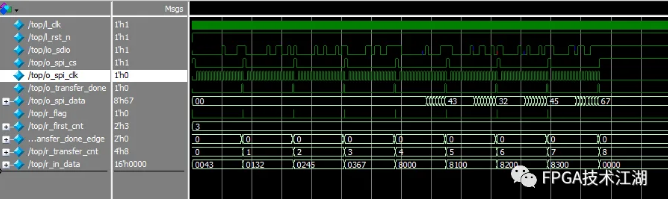

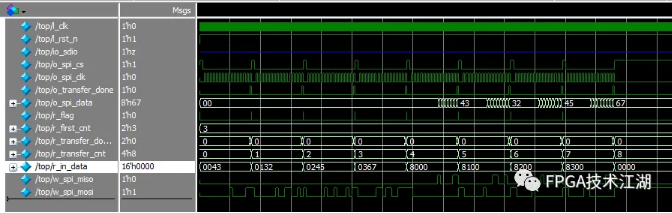

今天给大侠带来FPGA设计中,对SPI进行参数化结构设计,话不多说,上货。 SPI salve SPI salve支持功能: 支持三线SPI或者四线SPI。通过define切换。 支持指令长度、帧长自定义。 工作时钟可自定义,大于SPI clk的2倍。 用户只需修改:(1)几线SPI。(2)单帧长度。(3)指令长度。(4)寄存器开辟。 注意:指令最高bit表示读写,低写高读,其余bit表示地址。指令接着为数据端,两者位宽之和即为SPI单帧长。 SPI master spi master内部仅仅封装SPI驱动,写入值读出控制由上层控制,这部分逻辑很simple,不赘述。用户只需给入SPI帧及控制使能即可。 用户只需修改parameter参数:(1)单帧长;(2)指令长;(3)数据长;(4)工作时钟;(5)SPI clk。 实现不使用状态机,采用线性序列计数法。 仿真如下所示:写入四个寄存器值,再读出。 仿真代码如下: 三线SPI: 四线SPI:

为了避免每次SPI驱动重写,直接参数化,尽量一劳永逸。SPI master有啥用呢,你发现各种外围芯片的配置一般都是通过SPI配置的,只不过有三线和四线。SPI slave有什么用呢,当外部主机(cpu)要读取FPGA内部寄存器值,那就很有用了,FPGA寄存器就相当于RAM,cpu通过SPI寻址读写数据。代码仅供参考,勿做商业用途。

可以看到读写是一致的,验证通过。

我要赚赏金

我要赚赏金