今天给大侠带来基于FPGA的数字电压表设计,附源码,获取源码,请在“FPGA技术江湖”公众号内回复“数字电压表设计源码”,可获取源码文件。话不多说,上货。

模数转换器,又称A/D转换器,简称ADC,通常是指一个将模拟信号转换为抗干扰性更强的数字信号的电子器件。一般的ADC是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小,故任何一个ADC都需要一个参考模拟量作为转换标准。比较常见的参考标准为最大的可转换信号大小,而输出的数字量则表示输入信号相对于参考信号的大小。本设计则通过对模数转换芯片(TLC549)的采样控制,实现一个简易的数字电压表。

设计原理

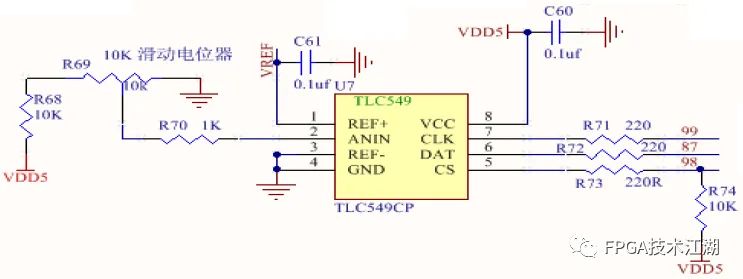

TLC549典型的配置电路如下图所示:

TLC549的端口描述如下:

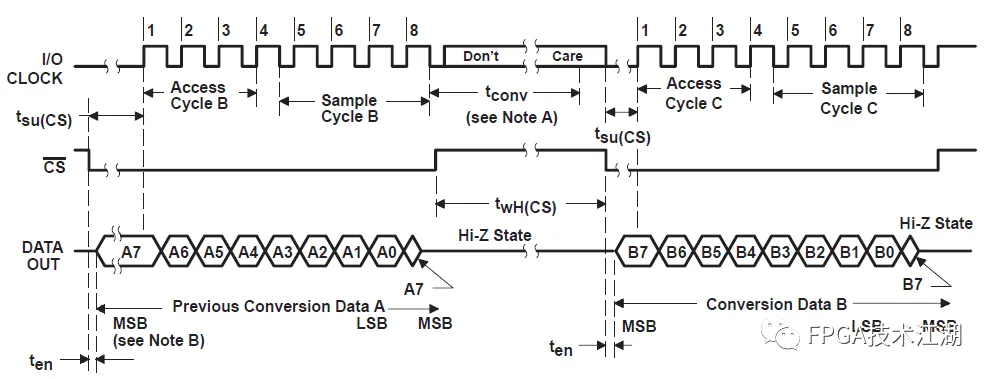

TLC549是一个8位的串行模数转换器,A/D转换时间最大为17us,最大转换速率为4MHz。下图为TLC549的访问时序,从图中可以看出,TLC549的使用只需对外接输入输出时钟(I/O CLK)和芯片选择(/CS)、输入的模拟信号(ANALOG IN)的控制。

分析时序图可知:当片选信号(/CS)拉低时,ADC前一次的转换数据(A)的最高位A7立即出现在数据线DATA OUT上,之后的数据在时钟I/O CLOCK的下降沿改变,可在I/O CLOCK的上升沿读取数据。转换时,/CS要置为高电平。在设计操作时,要注意Tsu(CS)、Tconv、Twh(CS)和I/O CLOCK的频率这几个参数。Tsu(CS)为CS拉低到I/O CLOCK第一个时钟到来的时间,至少要1.4us;Twh(CS)为ADC的转换时钟,不超过17us,Tconv的值也不超过17us;I/O CLOCK为 1.1MHz。其他参数可参考数据手册。

由于ADC是8位的,所以采样的电压值为:

V =(D*Vref)/256

其中V为采样的电压值;D为ADC转换后读取的8位二进制数;Vref为参考电压值,此处为2.5V。

设计架构

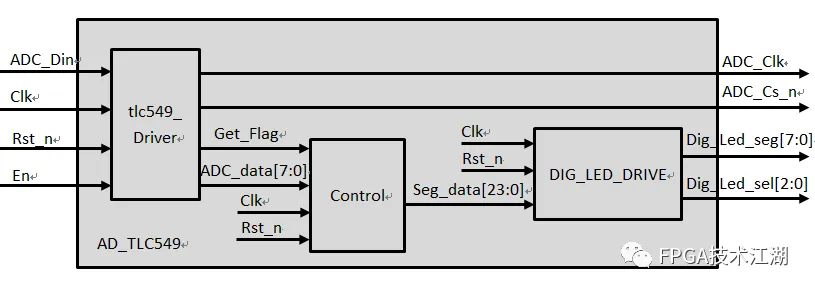

本设计通过调节电位器RW1改变ADC的模拟输入值,数据采样读取后由数码管显示,最后用万用表测量输入电压,并与读取在数码管上的数据(单位为mV)作比较。设计的架构图如下:

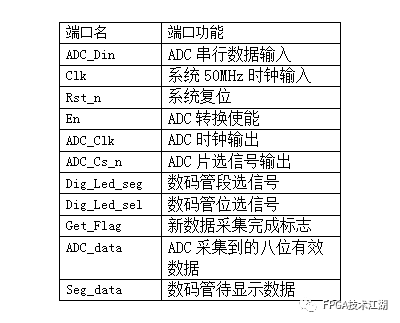

设计架构图对应端口的功能描述表:

tlc549_Driver模块采用序列机实现接口访问时序,并且产生1MHz的ADC_Clk和采集到ADC_data;Control模块,将采集到的ADC数据(ADC_data)换算成对应的电压值,并经过二进制到BCD转换以后传送到数码管;DIG_LED_DRIVE模块负责数码管的驱动,将传递过来的数据显示出来。

设计代码

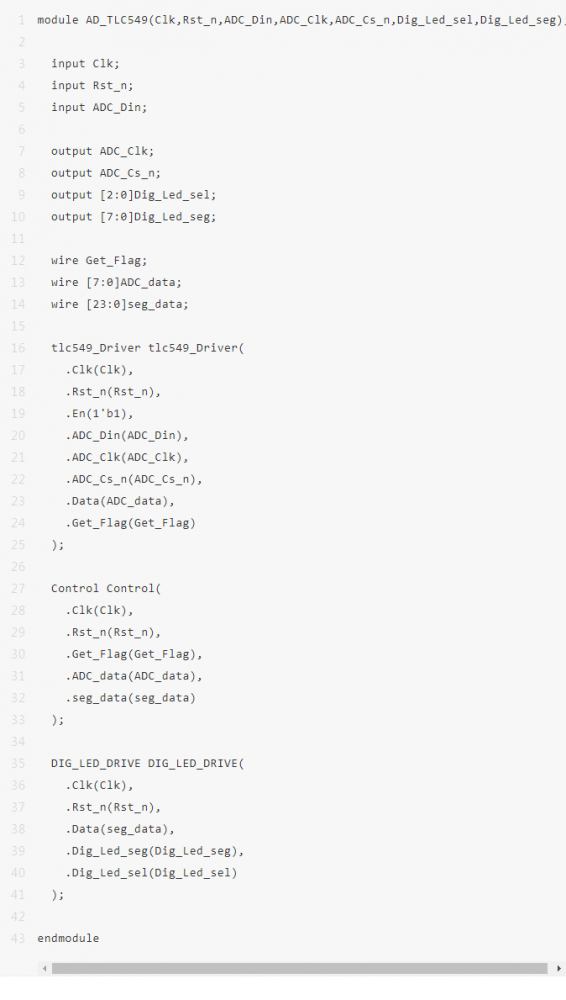

AD_TLC549顶层模块代码:

=

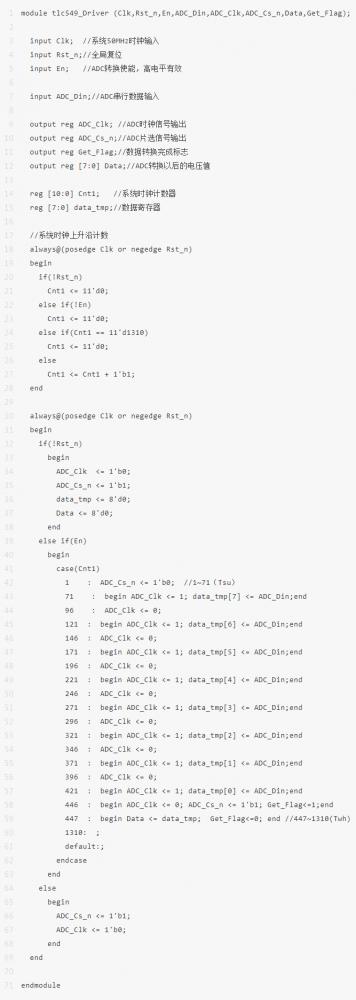

tlc549_Driver模块代码:

=

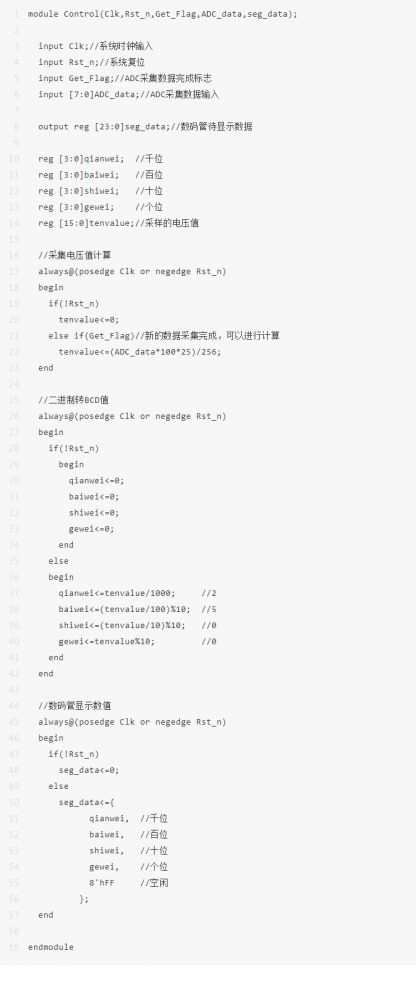

Control模块代码:

=

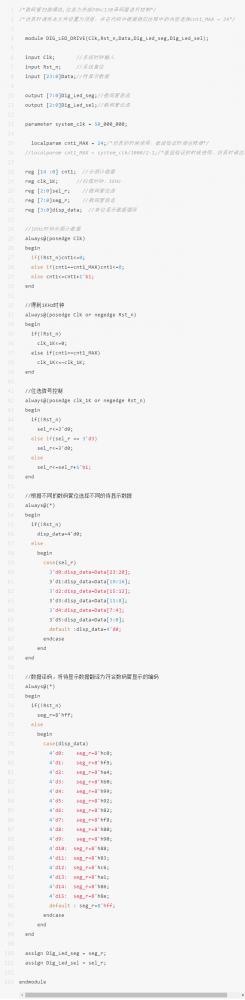

DIG_LED_DRIVE模块代码:

=

仿真测试

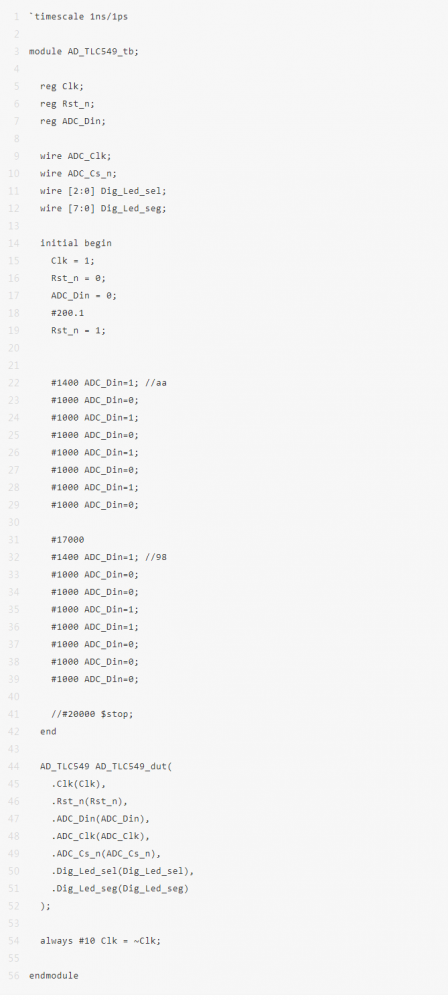

AD_TLC549_tb顶层测试代码如下:

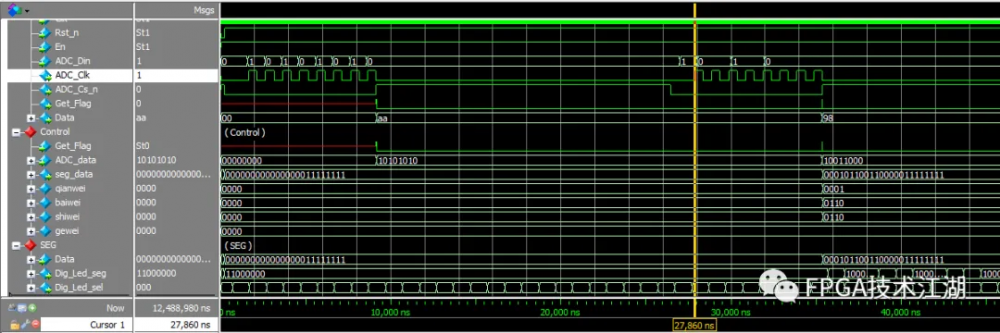

仿真图如下所示:

观察仿真图,实现了数据的采集,并正确显示,下板验证结果也达到了设计的预期效果。

我要赚赏金

我要赚赏金