地线干扰以及PCB走线的影响在电路设计中是一个重要且复杂的问题。以下是对这两个问题的详细分析和归纳:

感觉音响的要求更高一点,这里分享一下,后面再说音响的:

一、地线干扰

地线干扰是指通过公用地线的方式产生的信号干扰,通常发生在不同的单元电路、部件或系统之间。地线干扰的形式主要可以归结为三类:

地环路干扰:由于地线阻抗的存在,当电流流过地线时,会在地线上产生电压。当电流较大时,这个电压可以很大。例如,附近有大功率用电器启动时,会在地线中流过很强的电流,从而在“地线环路”中产生差模电压,对电路造成影响。

公共阻抗干扰:当两个电路共用一段地线时,由于地线的阻抗,一个电路的地电位会受另一个电路工作电流的调制。这种耦合称为公共阻抗耦合,可能导致信号从一个电路耦合到另一个电路。

地环路电磁耦合干扰:在实际电路的PCB上,“地线环路”将包围一定的面积。根据电磁感应定律,这个环路会产生电磁场,与附近的导线发生电磁耦合,从而产生干扰。

二、PCB走线的影响

PCB走线对电路性能的影响主要体现在以下几个方面:

导线阻抗:PCB上的导线(包括地线)同样存在阻抗。对于交流信号,导线的感抗成分不可忽略,尤其是当频率较高时。这种阻抗可能导致信号衰减、相位偏移等问题。

信号串扰:当PCB上的走线布局不合理时,不同信号线之间可能发生串扰。这可能是由于信号线之间的电容耦合、电感耦合或电磁辐射引起的。

电磁干扰(EMI):PCB上的走线布局、线宽、线距等因素都可能影响电磁干扰的大小。不合理的走线布局可能导致电磁辐射增加,从而对其他电路或系统产生干扰。

为了减小地线干扰和PCB走线的影响,可以采取以下措施:

优化地线设计:尽量减小地线阻抗,避免地线环路,使用多层板设计来分离不同电压的地线等。

合理布局PCB走线:避免信号线之间的交叉和重叠,保持足够的线距和线宽,使用屏蔽线或地线来隔离敏感信号等。

使用滤波器、隔离器等器件来减小干扰:这些器件可以有效地滤除或隔离干扰信号,提高电路的抗干扰能力。

由于接地电路中有杂散电流,可能会有不必要的电位累积在其他敏感地点,这样地线并不是真正的零电位,即电位得到了提升。为了防止这个情况发生,可以利用多种技术,包括以下措施:

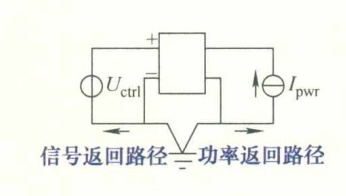

不要将信号返回走线和功率返回走线直接捆绑在一起;2.将电源地和信号地分开,如图所示;

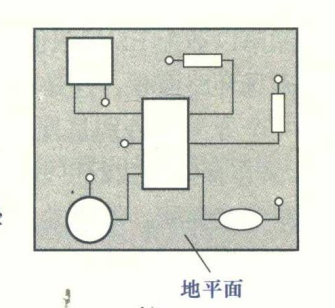

使用地平面,如图所示;

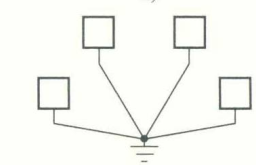

应用星形接地/单点接地配置,如图所示:

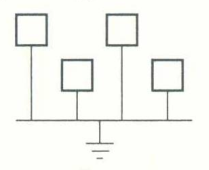

使用接地总线,如图所示:

对于接大地的电源系统引入的差模干扰信号,特别是在超标频段9kHz~5MHz和30~70MHz,以下是一些建议的处理方法:

使用Y2电容:

在L线和N线,即火线和零线上,各自串联一个Y2电容到大地。Y2电容是安规电容的一种,主要用于跨接L线、N线与地之间,其功能是压制共模干扰。但在这里,它也可以对差模干扰产生一定的抑制作用,尤其是在特定的频段上。

引入差模电感:

地线在接入电源系统之前,先通过一个差模电感。差模电感主要用来抑制电源线上的差模干扰,它允许电源电流通过,但对差模干扰电流产生较大的阻抗,从而起到抑制差模干扰的作用。

使用镍锌材质磁环:

地线套上镍锌材质的磁环,并绕2~4圈。镍锌磁环具有较高的磁导率和磁饱和感,能够吸收高频噪声和干扰信号。通过绕制一定的圈数,可以增强其对特定频段干扰的抑制作用。

同样地,输出线也可以套上镍锌材质的磁环,并绕2~4圈,以减少输出线上的干扰信号。

在功率地方面,驱动中常见的三个主功率环路包括:

PFC功率环路:

用于提高电源的功率因数,减小对电网的谐波污染。

DC-DC功率环路(降压、反激、正激、半桥、全桥等):

这些是直流到直流的转换电路,用于将一种直流电压转换为另一种直流电压,以满足不同电路或设备的需求。

输出功率环路:

这是指电源向负载提供功率的环路,它直接决定了电源的输出性能和稳定性。

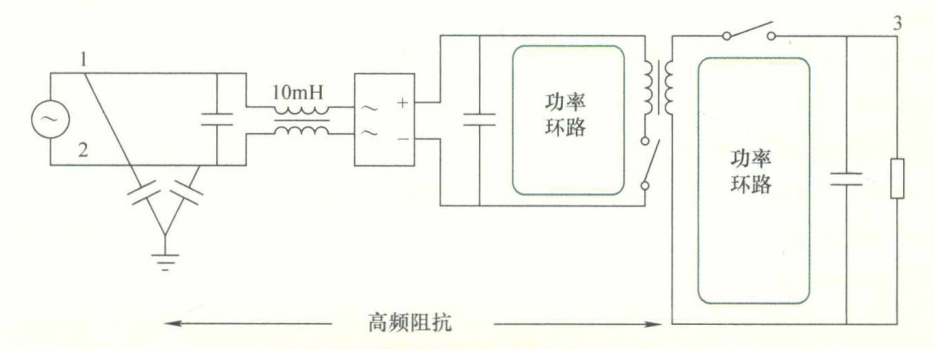

反激变换器中的功率环路如图所示:

在功率环路设计中,接地走线的处理对于防止干扰和保证电路性能至关重要。以下是根据您提供的信息和参考文章中的相关内容,对功率环路中接地走线处理的详细分析和建议:

功率环路接地走线的重要性

防止信号走线被干扰:功率走线中可能存在较大的电流变化(di/dt),这些变化会产生电磁场,对附近的信号走线造成干扰。因此,功率环路的接地走线必须与信号地走线分开,以减少这种干扰。

减小环路走线面积:过大的环路走线面积会增加电磁辐射的可能性,特别是在30~50MHz和70~100MHz频段。因此,合理设计功率地的环路走线,减小其面积,是降低电磁辐射的有效方法。

整改方法

在PFC的MOSFET的DS之间增加MLCC小电容:

在MOSFET的漏极(D)和源极(S)之间增加一个MLCC(多层陶瓷电容器)小电容,容值在22~100pF之间。过小的电容效果不明显,过大的电容则可能导致效率降低和MOSFET温升过高。

如果空间允许,建议使用插件瓷片电容代替高压MLCC,因为它们通常具有更好的性能。

在PFC的拓扑二极管上并RC电路:

对于中小功率变换器,可以在拓扑二极管上并联一个RC电路,其中R在100Ω左右,C在100pF以下。这种方法可以显著减少电磁辐射,但可能会对效率产生影响,并需要重新调试相关参数。

需要注意的是,RC电路的加入可能会对某些APFC芯片的过零检测功能产生影响,如ST的L6562X系列芯片。因此,在实际应用中需要谨慎使用,并进行必要的调试。

对于PFC后级连接Flyback的拓扑结构:

如果PFC后级连接的是Flyback拓扑结构,仍然可以使用上述方法在MOSFET和拓扑二极管上增加MLCC小电容和RC电路来减少电磁辐射。

我要赚赏金

我要赚赏金