接触NXP的单片机比较少,前面使用RTT,只需要修改少量的代码即可以完成。

今天读了一下他的驱动,发现跟STM32的驱动有很多的不同点。

他的驱动使用结构来定义读取的对一个GPIO的定义如下:

#if defined(FSL_FEATURE_PORT_PCR_MUX_WIDTH) && FSL_FEATURE_PORT_PCR_MUX_WIDTH

/*! @brief PORT pin configuration structure */

typedef struct _port_pin_config

{

#if defined(FSL_FEATURE_PORT_HAS_PULL_ENABLE) && FSL_FEATURE_PORT_HAS_PULL_ENABLE

uint16_t pullSelect : 2; /*!< No-pull/pull-down/pull-up select */

#else

uint16_t : 2;

#endif /* FSL_FEATURE_PORT_HAS_PULL_ENABLE */

#if defined(FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE) && FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE

uint16_t pullValueSelect : 1; /*!< Pull value select */

#endif /* FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE */

#if defined(FSL_FEATURE_PORT_HAS_SLEW_RATE) && FSL_FEATURE_PORT_HAS_SLEW_RATE

uint16_t slewRate : 1; /*!< Fast/slow slew rate Configure */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_SLEW_RATE */

#if !(defined(FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE) && FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE)

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE */

#if defined(FSL_FEATURE_PORT_HAS_PASSIVE_FILTER) && FSL_FEATURE_PORT_HAS_PASSIVE_FILTER

uint16_t passiveFilterEnable : 1; /*!< Passive filter enable/disable */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_PASSIVE_FILTER */

#if defined(FSL_FEATURE_PORT_HAS_OPEN_DRAIN) && FSL_FEATURE_PORT_HAS_OPEN_DRAIN

uint16_t openDrainEnable : 1; /*!< Open drain enable/disable */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_OPEN_DRAIN */

#if defined(FSL_FEATURE_PORT_HAS_DRIVE_STRENGTH) && FSL_FEATURE_PORT_HAS_DRIVE_STRENGTH

uint16_t driveStrength : 1; /*!< Fast/slow drive strength configure */

#else

uint16_t : 1;

#endif

#if defined(FSL_FEATURE_PORT_HAS_DRIVE_STRENGTH1) && FSL_FEATURE_PORT_HAS_DRIVE_STRENGTH1

uint16_t driveStrength1 : 1; /*!< Normal/Double drive strength enable/disable */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_DRIVE_STRENGTH1 */

#if defined(FSL_FEATURE_PORT_PCR_MUX_WIDTH) && (FSL_FEATURE_PORT_PCR_MUX_WIDTH == 3)

uint16_t mux : 3; /*!< Pin mux Configure */

uint16_t : 1;

#elif defined(FSL_FEATURE_PORT_PCR_MUX_WIDTH) && (FSL_FEATURE_PORT_PCR_MUX_WIDTH == 4)

uint16_t mux : 4; /*!< Pin mux Configure */

#else

uint16_t : 4;

#endif

#if defined(FSL_FEATURE_PORT_HAS_INPUT_BUFFER) && FSL_FEATURE_PORT_HAS_INPUT_BUFFER

uint16_t inputBuffer : 1; /*!< Input Buffer Configure */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_INPUT_BUFFER */

#if defined(FSL_FEATURE_PORT_HAS_INVERT_INPUT) && FSL_FEATURE_PORT_HAS_INVERT_INPUT

uint16_t invertInput : 1; /*!< Invert Input Configure */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_INVERT_INPUT */

uint16_t : 1;

#if defined(FSL_FEATURE_PORT_HAS_PIN_CONTROL_LOCK) && FSL_FEATURE_PORT_HAS_PIN_CONTROL_LOCK

uint16_t lockRegister : 1; /*!< Lock/unlock the PCR field[15:0] */

#else

uint16_t : 1;

#endif /* FSL_FEATURE_PORT_HAS_PIN_CONTROL_LOCK */

} port_pin_config_t;

#endif /* FSL_FEATURE_PORT_PCR_MUX_WIDTH */去除掉条件编译,简化如下:

/*! @brief PORT pin configuration structure */

typedef struct _port_pin_config

{

uint16_t pullSelect : 2; /*!< No-pull/pull-down/pull-up select 先择上下拉方式 */

/* FSL_FEATURE_PORT_HAS_PULL_ENABLE */

uint16_t pullValueSelect : 1; /*!< Pull value select 上下位的值 */

/* FSL_FEATURE_PORT_PCR_HAS_PULL_VALUE */

uint16_t slewRate : 1; /*!< Fast/slow slew rate Configure 速率*/

/* FSL_FEATURE_PORT_HAS_SLEW_RATE */

uint16_t passiveFilterEnable : 1; /*!< Passive filter enable/disable */

/* FSL_FEATURE_PORT_HAS_PASSIVE_FILTER */

uint16_t openDrainEnable : 1; /*!< Open drain enable/disable 开漏是否启用 */

/* FSL_FEATURE_PORT_HAS_OPEN_DRAIN */

uint16_t driveStrength : 1; /*!< Fast/slow drive strength configure 快/慢驱动 */

uint16_t driveStrength1 : 1; /*!< Normal/Double drive strength enable/disable 正常或双部驱动 */

/* FSL_FEATURE_PORT_HAS_DRIVE_STRENGTH1 */

uint16_t mux : 4; /*!< Pin mux Configure 复用选择*/

uint16_t inputBuffer : 1; /*!< Input Buffer Configure 输入缓冲*/

/* FSL_FEATURE_PORT_HAS_INPUT_BUFFER */

uint16_t invertInput : 1; /*!< Invert Input Configure 中断是否开启*/

/* FSL_FEATURE_PORT_HAS_INVERT_INPUT */

uint16_t : 1;

uint16_t lockRegister : 1; /*!< Lock/unlock the PCR field[15:0] */

/* FSL_FEATURE_PORT_HAS_PIN_CONTROL_LOCK */

} port_pin_config_t;

/* FSL_FEATURE_PORT_PCR_MUX_WIDTH */

根据编译条件,结构体优化下来是只是占用了uint16_t的空间,

在管脚的初始化时,示例工程中配置如下:const port_pin_config_t LED_RED = {/* Internal pull-up/down resistor is disabled */

kPORT_PullDisable,

/* Low internal pull resistor value is selected. */

kPORT_LowPullResistor,

/* Fast slew rate is configured */

kPORT_FastSlewRate,

/* Passive input filter is disabled */

kPORT_PassiveFilterDisable,

/* Open drain output is disabled */

kPORT_OpenDrainDisable,

/* Low drive strength is configured */

kPORT_LowDriveStrength,

/* Normal drive strength is configured */

kPORT_NormalDriveStrength,

/* Pin is configured as P3_12 */

kPORT_MuxAlt0,

/* Digital input enabled */

kPORT_InputBufferEnable,

/* Digital input is not inverted */

kPORT_InputNormal,

/* Pin Control Register fields [15:0] are not locked */

kPORT_UnlockRegister};官方的库中,对每个寄存器的配置都给出了枚举,使得阅读方便。

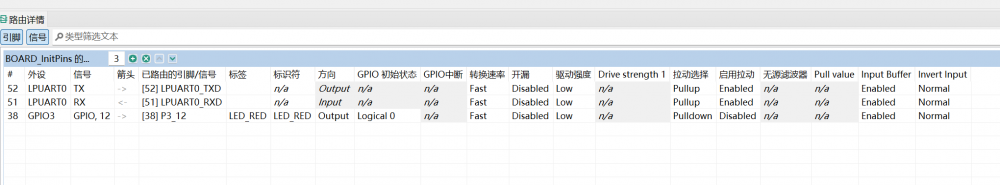

其实大家也不需要太多的去记,因为官方给出的图形化配置工具,给出了详细的中文界,点点就可以配置好:

在这里可以添加一行,对所需的GPIO进行配置,然后自动生成代码。

我要赚赏金

我要赚赏金