待机功耗的降低是一个在电子设备设计和电源管理中非常重要的问题。在无负载状态下,设备的功耗虽然相对较小,但长时间的待机状态依然会累积成相当数量的能源消耗。

以下是一些关于待机功耗降低的方法,以及进行的详细解释和方法:

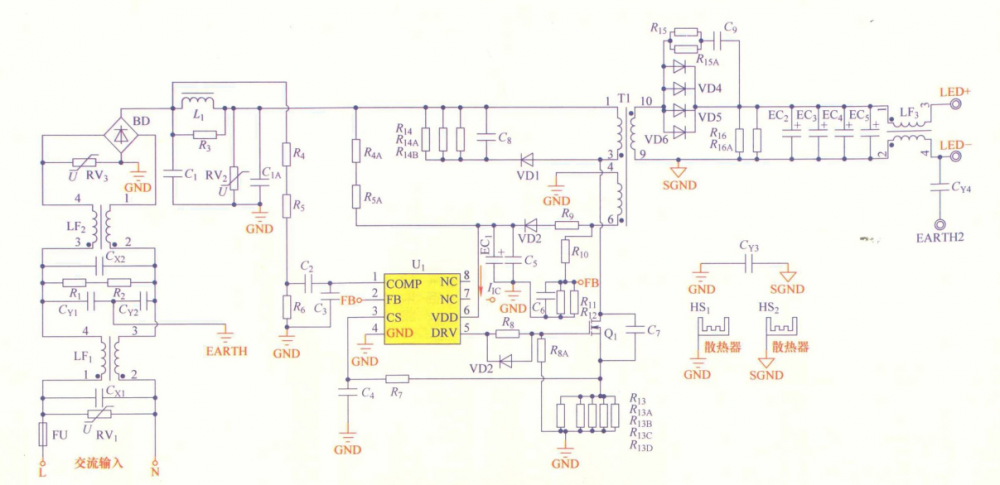

优化电路设计:输入部分损耗:通过适当设计共模电感,包括线径和匝数,可以降低脉冲电流造成的共模电感内阻损耗。此外,还可以在符合安规的前提下加大放电电阻的组织,减小热敏电阻的阻值,从而减少相应的损耗。启动损耗:使用恒流启动方式启动,启动完成后关闭启动电路,从而降低启动电阻的损耗。与开关电源工作相关的损耗:这包括X电容的放电电阻损耗和启动电阻的损耗。在满足放电时间和启动时间的要求下,适当增大这些电阻的阻值可以降低损耗。例如,假设R1+R2=1MΩ,并且R4A+R5A=480kΩ,则阻值越大,损耗越小。使用高效能元件:选择具有低待机功耗的电子元器件,如高效能的电源管理芯片、低漏电流的MOSFET等。优化软件控制:通过软件控制,使设备在待机状态下进入深度休眠模式,进一步降低CPU、内存等核心部件的功耗。待机监测策略:通过智能插座或其他监测设备,实时监测设备的待机功耗,并根据用户的使用需求进行判断和控制,以最大限度地降低待机能耗。提高能源利用效率:通过改进电源转换效率、减少不必要的能源浪费等方式,提高整体系统的能源利用效率。下面根据电路看一下具体的方法:

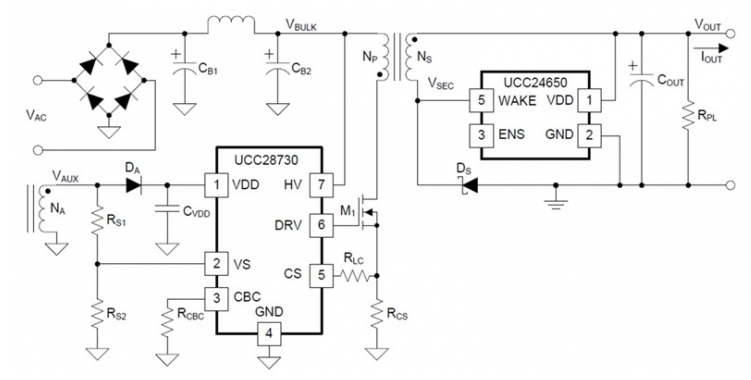

一次侧单级 PFC 电路原理图:

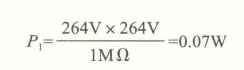

1.X电容的放电电阻损耗,R和R,在输人电压最高的时候功耗最大,假设R,+R,=1MΩ,则:

在满足放电时间的要求下,这两个电阻阻值越大,则损耗越小。

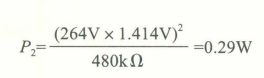

2.启动电阻的损耗,R4A和R5A,在输人电压最高的时候功耗最大,假设R4A+R5A=480k0,则:

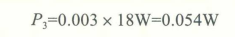

在满足启动时间的要求下,这两个电阻阻值越大,则损耗越小。3.芯片损耗,假设芯片正常工作电流有效值为3mA,工作电压为18V,则:

在保证芯片在全范围下不会进人欠电压状态时,应按比较低的工作电压选取,这样损耗最小。

4.假负载的损耗,R16和R6A,在输出电压最高的时候(假设空载电压40V)功耗最大,假设R16和R16A都取 30kΩ,则:

对上面的图,总的待机损耗P=P,+P,+P:+P=(0.07+0.29+0.054+0.11)W=0.524W,从上面的分析可以看出,除开芯片这个因素,功率损耗最大在启动电阻和假负载,若想降低待机的损耗,就需要重点考虑这两点。启动电阻的大小与启动时间的快慢相关联,假负载的大小与输出电容放电快慢相关联,根据实际情况,可以选择不同大小的启动电阻和假负载。

一个简化的示意图,说明了如何在极低开关频率下实现稳定的电源输出和负载阶跃响应。

唤醒监视器在电源设计中扮演着关键角色,特别是在需要实现极低待机功耗的应用中。

这些监视器通常位于变压器的次级侧,持续监视输出电压或电流,并在检测到负载变化时向初级侧的控制器发送唤醒信号。

以下是对您提到的UCC28730和UCC24650两款产品的概述和特性解释:UCC28730 PSR反激控制器功能:使用主侧绕组传感提供精确的电压和恒流调节,无需光耦合器反馈电路。它工作在谷开关的不连续传导模式下,以最小化开关损耗。调制方案:结合了频率调制和一次峰值电流调制,提供高转换效率。电源管理:在低功耗工作水平时,设备可以降低开关频率,进一步减少功耗。电磁干扰:具有降低基本开关频率及其谐波处电磁干扰峰值能量的特性。优点:通过一次侧控制实现准确的电压和电流调节、快速的动态响应和故障保护。UCC24650二次侧电压监视器监视功能:定期检测VDD电压,并在检测到3%的浮动时发送唤醒信号给一次侧稳压(PSR)控制器。唤醒信号:在检测到控制器驱动的开关活动之前,以33kHz的频率重复发送唤醒信号。相对浮动检测:允许电压调节至5V至28V之间的任一电压。超低待机频率:唤醒警报功能实现超低待机频率,以最大限度降低开关损耗并减小响应重载阶跃所需的输出电容。使能和禁用信号:可用于控制二次侧电路(如同步整流控制器或继电器驱动器),以进一步降低待机功耗。特性性能:具有出色的负载瞬态性能和零待机功耗。输出电容:实现最小输出电容,以降低ΔV-OUT。功耗:器件电流补偿小于50μA(典型值)。封装:采用5引脚小外形尺寸晶体管(SOT)-23封装。

我要赚赏金

我要赚赏金