在传统的通信技术中,中频解调单元均采用模拟方法进行处理,即采用模拟滤波器、混频器、乘法器和压控振荡器等模拟器件进行电路实现,从而导致所设计通信电路结构复杂、体积大。另外模拟器件功耗和内部噪声都比较大,且抗干扰能力差,易受外界环境影响,不能保证长时间稳定可靠地工作。因此,这种传统的中频解调电路不能实现对数字信号的最佳接收。

相对于模拟电路,数字电路具有传输速度快、传输距离远、抗干扰能力强、传输误码率低等优势。通信技术正向着模拟到数字化的方向快速发展,基于数字信号处理与高速数字电路开发技术的数字化通信技术正成为现代通信的中坚力量。

随着超大规模集成电路的发展以及半导体工艺的进步,通信技术中解调算法的数字化实现已经成为现代测控通信技术的发展趋势。QPSK解调方式由于具有包络恒定、解调处理过程误码率低、解调效率高等特点而被广泛应用于现代通信系统中。

本文在对QPSK数字解调原理进行深入研究后,利用FPGA开发软件对解调过程中载波同步及位同步等关键技术模块进行了电路搭建,并对解调器功能进行了仿真分析和在线验证。仿真分析及在线测试结果表明该中频数字解调系统功能稳定,性能良好,能够满足实际工程需求。

1QPSK中频数字解调原理

本文所设计的QPSK中频数字解调器,首先接收前端的中频调制信号,然后对其进行数字下变频处理,最后将所得到的信号通过低通滤波器处理,从而恢复基带码元信号。由于调制载波与本地载波具有一定的频差及相位偏差,本文通过数字Costas载波同步环对本地数控振荡器产生载波频率进行动态调整,从而更好地恢复基带码元信号。由于信道传输延迟,解调端采样时钟与调制端采样时钟不能完全同步,为了对载波恢复数据进行更准确的抽样判决,本文采用基于Gardner算法的位同步环路对原始基带码元序列进行了更好的恢复。

1.1数字Costas载波同步环

为了实现数字解调功能,通常采用的载波同步环路有逆调制环、M次方环和Costas环。逆调制载波同步环和M次方环通常用在低速解调场合,不能满足现代测控通信高速解调的要求。

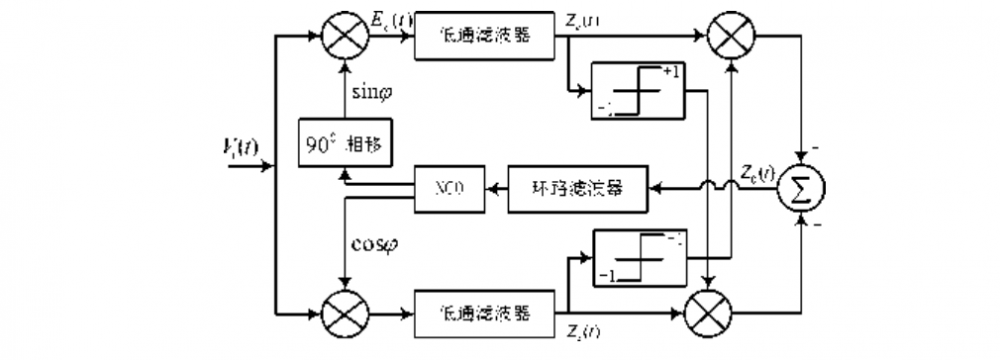

相比于其它几种载波同步环路,数字Costas载波同步环具有更快的输出响应,环路工作更加稳定,环路模型内部参数灵活可变。因此,在本文设计的数字解调器中采用数字Costas环完成载波同步过程,其原理框图1所示。

图1数字Costas载波同步环

由图1可知,本文设计的数字Costas载波同步环路由正交双通道组成,输入调制信号分别与同相和正交载波频率相乘,将混频输出分别经过低通滤波器得到基带信号,两路基带信号通过数字鉴相器得出环路误差信号,并将此误差信号作为数控振荡器反馈输入信号,从而产生所需载波频率,保证载波同步环路更快地进入锁定状态。

为了通过数字Costas载波同步环更好地实现环路误差估计,通常在两路基带信号进入数字鉴相器之前,先通过硬限幅器将信号幅度限制在一定范围内,从而保证后端电路进行更准确的采样判决。

假定数控振荡器输出的两路正交载波分别为cos(ω0t+Δφ)和sin(ω0t+Δφ),根据实际信道传输过程,可知本地载波与调制载波具有一定的相位差,假定相位误差表示如下式:

式中(ω0 - ωc)t 为本地载波与调制载波的频差,φ0(t)为载波 相位偏差,由此可得鉴相器输出误差信号表达式如下:

为了使载波同步环路控制更准确,通常需要将误差信号经过环路滤波器滤除高频噪声干扰。则本文中所设计载波同步环路经过环路滤波后,可得误差信号表达式如下:

1.2基于Gardner算法的位同步环

在现代通信系统中,通常采用三种位同步方式完成环路锁定:模拟方式、混合方式及数字方式。

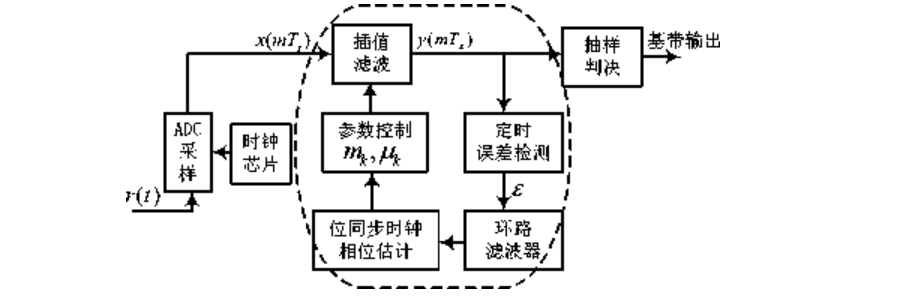

相比于模拟位同步方式,数字位同步方式具有抗干扰能力强、信道传输误码率低等优点。经过对各种位同步方式进行比较之后,本文采用基于Gardner算法的数字插值滤波结构实现位同步。该方法通过比较本地时钟与接收数据码元时钟,采用插值抽样的方法直接获得位同步时钟的估计值,进而使本地时钟与接收基带码元时钟同步。数字内插位同步环路的原理框图如图2所示。

图2数字内插位同步环路原理图

图2中,虚线部分表示位同步反馈环路,y(mL:)表示插值滤波输出,m和例分别表示内插控制参数,e表示定时误差检测输出。ADC采样模块在外部时钟的控制下,对接收到的模拟输入信号进行采样,从而得到数字化离散信号x(mL),将其输入到位同步反馈环路,进而使位同步环路进入锁定。位同步环路由插值滤波器、定时误差检测模块、环路滤波器和内插控制器四部分组成:

在进行数字插值滤波器设计时,通常采用多相结构、横向结构以及Fallow结构。在低速解调应用场合,通常采用横向结构进行插值滤波器电路实现。多相结构大多应用于时变线性滤波器,这种滤波器设计具有比较复杂的硬件电路,很难在实际工程中得到应用。相比于以上两种滤波器,基于Farrow结构的数字插值滤波器易于电路设计实现,且具有较好的滤波性能,本文在进行解调器电路设计时,即选用了此种插值滤波器。

定时误差检测器是位同步环路的重要环节,只有环路能够准确地检测出定时误差,才能保证位同步环路尽快地锁定。定时误差检测通常有非数据辅助算法和数据辅助判决算法。非数据辅助算法能够减少位定时信息的使用,通常用在信噪比较低的场合,以Gardner算法应用较多;数据辅助判决算法能够增大位定时信息的利用率,通常用在信噪比较高的场合,以最大似然估计算法应用较多。经过对位同步环路各项具体指标进行综合考虑,本文最终决定采用基于Gardner算法的位同步误差检测方法,Gardner算法具有运算效率高,环路误差检测能力强,能够用在数据传输速率较高的场合。

环路滤波器接收误差检测器输出误差信号,滤除其中高频噪声干扰,得到较准确的误差信号输出,从而保证位同步环路能够更快地进入锁定状态。

内插控制器接收环路滤波器输出误差信号e,通过控制内插控制器内部NCO数控振荡器,从而产生内插基点控制系数m和小数间隔控制参数加并反馈输入到插值滤波器,进而控制整个位同步环路正常锁定。

2QPSK数字解调关键模块的FPGA设计及功能仿真

传统的数字电路设计主要通过ASIC专用集成电路实现,但ASIC开发周期长,且不具有可灵活编程的特点,不能满足现代通信系统的高传输速率、高度灵活性的要求。

随着数字信号处理技术的进步及超大规模集成电路的发展,FPGA因其所具有的各种优势在数字电路设计领域得到迅速发展。FPGA具有丰富的逻辑资源和布线资源,能够通过软件编程的方法对电路功能进行动态更改,硬件实现简单、开发周期短。现代测控通信技术中,通常利用FPGA完成数字电路设计。

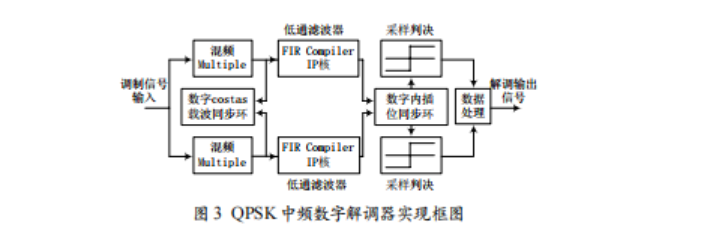

本文通过对各种指标进行综合考虑,决定利用FPGA编程工具完成中频数字解调器电路设计,其硬件实现原理框图如图3所示。

由图3可以看出,中频数字解调器主要由载波同步环路和位同步环路组成。输入调制信号先经过载波同步模块消除调制载波和本地载波的频偏及相位偏差,然后将载波恢复基带数据信号通过位同步环路,从而消除解调端和调制端的采样时钟偏差。

2.1载波同步模块FPGA设计及功能仿真

本文中载波同步模块主要包括数字下变频、低通滤波器、环路滤波器及数字鉴相器等模块。为了降低数字电路设计难度,提高数字电路设计效率,本文中通过调用DDSIP核产生

所需载波频率;利用FPGA开发软件内部集成的乘法器核完成混频操作;通过调用CICCompilerIP核完成低通滤波器的设计;利用Verilog编程语言允许的加法和移位运算,实现环路滤波器和数字鉴相器的设计。

本文所设计载波同步模块系统采样时钟为200MHz,输出载波频率为40.7MHz,在系统采样时钟的驱动下,每间隔5个载波周期抽取一个采样点。完成载波同步模块电路设计后,利用Modelsim仿真软件对载波同步环路关键信号进行仿真,得到的仿真波形如图4所示。

图4数字Costas环关键信号仿真波形

图4中,信号muti_sin_out和muti_cos_out为数控振荡器的两路正交载波输出。信号muti_out_i和muti_out_q为数字下变频的混频输出,从图4可以看出,混频输出波形基本能够反映输入基带信号波形,但是混频电路输出信号中混有高频谐波分量,因而出现如图所示图形包络。cic_dout」和cic_dout_q为低通滤波器的输出信号,从图中可以看出,经过低通滤波之后,基带频谱中混入的高频成分被滤除掉,得到的信号波形和输入基带数字序列波形大致相同。信号Jianxiang_out为数字鉴相器的输出,从图中可以看出,数字鉴相器的输出具有很小的数量级,为了对数控振荡器进行更好地反馈控制,通常需要增加放大电路,将鉴相误差信号进行放大。信号huanlu_out为载波环路滤波器的输出,从图中可以看出,鉴相器输出波形经过平滑滤波,得到环路滤波输出作为数控振荡器的反馈输入控制信号。

2.2位同步模块FPGA设计及功能仿真

文中位同步电路主要包括插值滤波器、定时误差检测模块、环路滤波器和内插控制器等模块。具体编程实现时,由于硬件电路不能支持浮点运算,通常需要对位同步环路内部信号进行量化处理,在保证位同步环路能够正确恢复原始基带信号基础上,为了便于电路实现,通常采取减少内插采样点数方法,通过插值滤波器对输入信号进行下采样操作。并且尽量用移位操作代替乘法器的使用,这样既能够节省硬件资源,又能够提高计算精度。

本文的位同步环路采用流水线设计思想,下采样时钟为20MHz,完成位同步模块电路设计后,利用Modelsim仿真软件对位同步环路中关键信号进行仿真,得到的仿真波形如图5所示。

图5位同步模块关键信号仿真波形

图5中,在内插控制参数作用下,输入调制信号经过插值滤波器后,滤除信号频谱中的高频成分,得到较平滑的插值滤波输出,cz_filter_out_i和cz_filter_out_q分别为插值滤波器I、Q两路输出信号。error_detect_out_i和error_detect_out_q分别为定时误差检测模块的I、Q两路输出信号,由图6可以看出,定时误差检测电路输出信号基本能够反映相邻采样点的幅度变化大小。huanlu_filter_out_i和huanlu_filter_out_q分别为环路滤波器I、Q两路输出信号,误差信号经过环路滤波器之后,高频成分被滤除掉,环路滤波输出波形更加平滑,从而能够更加准确地反映误差检测模块输出误差信号大小。mk1、uk1及mk2、uk2分别为插值滤波器内插基点控制参数和小数间隔控制参数,在内插控制参数作用下,整个位同步环路能够更快地完成锁定。

3测试实验及结果

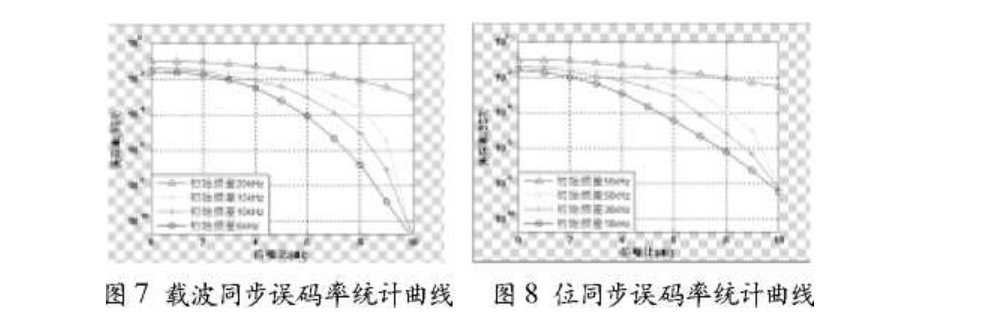

载波同步环路捕获带宽和载波恢复数据误码率为数字Costas载波同步环的两个主要指标,位同步环路同步带宽和位定时数据误码率为位同步环路的两个主要指标。

3.1载波同步模块关键指标测试

通过FPGA进行编程测试时,可以通过改变NCO数控振荡器的初始频率控制字来产生本地载波与调制载波的初始频差,当初始频差增大到一定值时,载波同步环路不能进入锁定状态,此值即为载波同步环路的最大捕获带宽叫

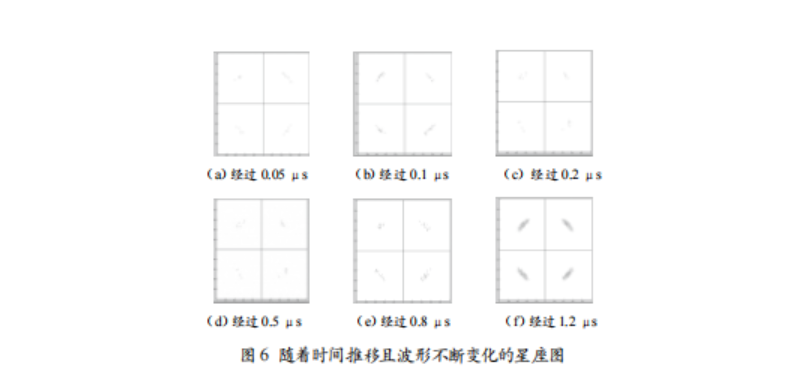

为了便于对解调器载波同步环路捕获带宽进行测试,本文采用Pin码产生随机数作为基带输入数据,当初始频差设定为5kHz条件下,利用在线逻辑分析仪的数据捕获及存储功能,

将载波恢复I、Q两路数据分别映射到x轴和y轴,可以得到如图6所示的、随着时间推移且波形不断变化的星座图。

当初始频差分别设定为5kHz,10kHz及15kHz时载波同步环路在经历一段时间的不稳态之后,最终能够进入锁定状态,但是当初始频差增大到20kHz条件下,载波同步环路经历很长时间之后仍然不能进入锁定状态。

经过大量测试,本文中所设计载波同步环路由未锁定状态进入到锁定状态,所需时间不超过0.1us,载波同步环路捕获带宽优于15kHz。

当初始频差分别设定为5kHz、10kHz、15kHz、20kHz条件下,经过大量的测试,对输入基带数据和载波恢复数据进行大数据量统计,并进行数据比对,可得到如图7所示的本载波同步环的误码率统计曲线。

由图7可知,当初始频差为5kHz条件下,随着环路逐渐进入锁定状态,载波恢复数据误码率逐渐降低,直至接近于0;当初始频差为20kHz条件下,环路不能进入锁定状态,载波恢复数据误码率一直保持较大值。

3.2位同步模块关键指标测试

为了便于位同步环路同步带宽的测试,本文在测试过程中利用FPGA内部集成的DCM数字时钟管理模块对内插采样频率进行动态微调,当初始频差设定为10kHz条件下,利用在线逻辑分析的数据捕获及存储功能,将位同步抽样判决两路输出数据分别映射到x轴和y轴,可以得到随着时间推

逐渐增大下采样初始频差,当初始频差增大到55kHz时,

位同步环路经过很长时间也不能完成锁定,表明55kHz的初始频差已超出了本文所设计的位同步环路同步带宽。

本文针对位同步环路进行大量测试,根据测试结果可知位同步环路同步带宽优于50kHz,位同步环路锁定建立时间约为1us。

在不同初始频差条件下,经过大量的测试,对基带输入数据和位同步插值滤波恢复数据进行大量统计,可得到图8所示的本位同步环路误码率统计曲线。

由图8可以看出,当下采样初始频差为10kHz条件下,随着环路逐渐进入锁定状态,位同步环路恢复数据误码率逐渐降低;当下采样初始频差为55kHz条件下,环路不能进入锁定状态,位同步环路恢复数据误码率一直保持较大值。

4结语

本文设计的基于FPGA的QPSK全数字中频解调器功能稳定,性能良好,数据传输误码率可低于10-9量级,载波同步环路捕获带宽优于15kHz,位同步环路同步带宽优于50kHz,可以推广到实际工程应用中。

来源: 整理文章为传播相关技术,网络版权归原作者所有,如有侵权,请联系删除。

我要赚赏金

我要赚赏金