在数字电路设计中,多输入门(multi-input gates)用于执行各种逻辑运算。每种门电路根据其功能对输入信号进行处理,并产生一个输出信号。

与门(AND Gate):

当且仅当所有输入都为1时,输出为1。

示例句法:

multiple_input AND gate_instance_name (OutputA, Input1, Input2, ..., InputN);

multiple_input AND AND_gate1 (OutA, In1, In2, In3);

与非门(NAND Gate):

与门的输出取反。即,当且仅当所有输入都为1时,输出为0;否则输出为1。

示例句法:

multiple_input NAND gate_instance_name (OutputA, Input1, Input2, ..., InputN);

multiple_input NAND NAND_gate1 (OutA, In1, In2, In3);

或门(OR Gate):

当至少一个输入为1时,输出为1。

示例句法:

multiple_input OR gate_instance_name (OutputA, Input1, Input2, ..., InputN);

multiple_input OR OR_gate1 (OutA, In1, In2, In3);

异或门(XOR Gate):

当输入数目为奇数时输出为1,输入数目为偶数时输出为0。

示例句法:

multiple_input XOR gate_instance_name (OutputA, Input1, Input2, ..., InputN);

multiple_input XOR XOR_gate1 (OutA, In1, In2, In3);

标准的XOR门通常只有两个输入。对于多输入XOR,实现可能更复杂,需要额外的逻辑。

同或门(XNOR Gate):

异或门的输出取反。即,当输入数目为偶数时输出为1,输入数目为奇数时输出为0。

示例句法:

multiple_input XNOR gate_instance_name (OutputA, Input1, Input2, ..., InputN);

multiple_input XNOR XNOR_gate1 (OutA, In1, In2, In3);

标准的XNOR门通常只有两个输入。对于多输入XNOR,实现可能更复杂,需要额外的逻辑。

在实际的数字电路设计中,对于超过两个输入的逻辑门(尤其是XOR和XNOR),可能需要通过组合逻辑(如使用多个两输入门)来实现。上述句法提供了一种理论上的表示方法,但在实际硬件描述语言(如Verilog或VHDL)中,可能需要更具体的实现方法。

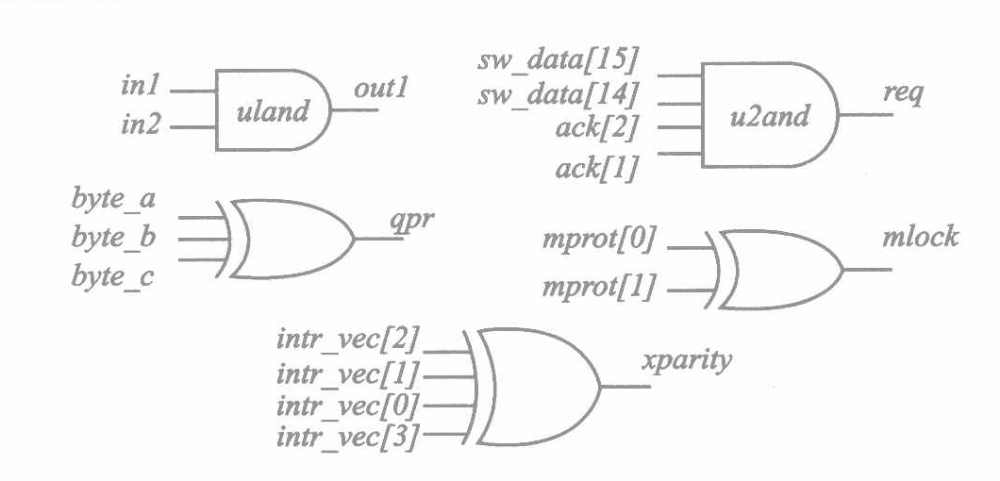

and uland(outl,in1,in2); and u2and( req,sw_data[15],sw_data[14],ack[2],ack[1]); xor (qpr,byte_a,byte b,byte_c), (mlock,mprot[0],mprot[1]), (xparity,intr_vec[2],intr_vec[1], intr_vec[0],intr_vec[3]);

第一条实例引用语句定义了一个名为u1and 的双输入与门,其输出为out1,两个输人分别为 in1 和 in2。

第二条实例语句定义了一个名为u2and 的四输入与门,其输出为reg,4个输入分别为 sw

data[15]、sw_data[14]、ack[2]和 ack[1]。第三条实例引用语句定义了一个没有具体名称的异或门,其输出是qpr,3个输人分别为byte_a、byte_b和byte_c;该条语句同时还定义了另外两个没有具体名称的异或门。

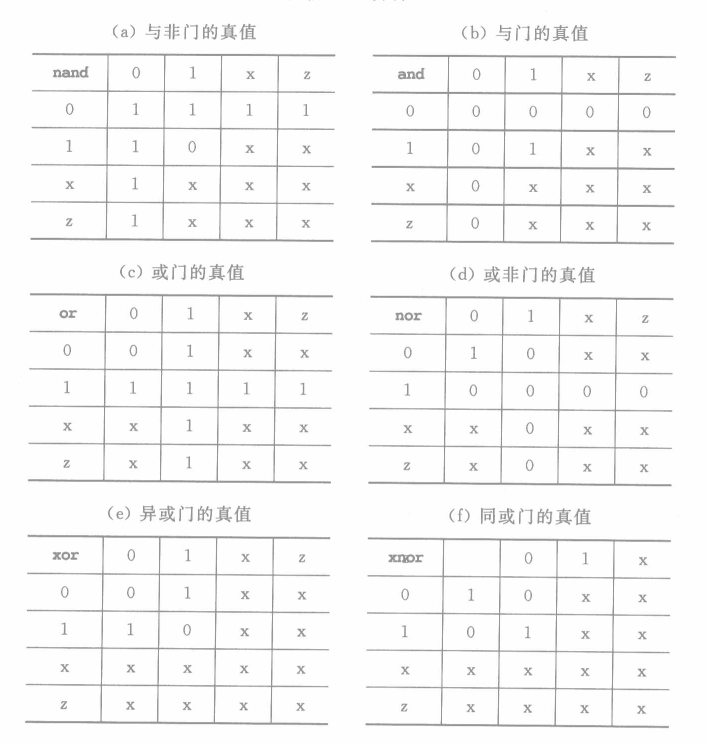

请注意出现在输入端的z值其处理方式与x值相同;此外多输入门的输出决不可能是z。

总结:

在数字电路设计中,多输入门执行各种逻辑运算,每种门电路根据功能处理输入信号并产生输出。常见的多输入门包括与门、与非门、或门、异或门和同或门。对于超过两个输入的逻辑门,尤其是XOR和XNOR,可能需要通过组合逻辑实现。

实例引用语句定义了具体逻辑门的名称、输出和输入。and u1and(outl,in1,in2); 定义了一个双输入与门,而 and u2and(req,sw_data[15],sw_data[14],ack[2],ack[1]); 定义了一个四输入与门。异或门的实例可能更复杂, xor(qpr,byte_a,byte_b,byte_c), 同时定义了其他异或门。

在硬件描述语言中,这些实例需要更具体的实现。输入端的z值(高阻态)通常与x值(未知态)相同处理,而多输入门的输出不可能是z。了解这些基本概念有助于设计复杂的数字电路,并通过组合逻辑门实现所需的功能。

我要赚赏金

我要赚赏金