【前言】

在macOS下面如果要对MM32F5375进行开发的话,需要创建基于GCC下的开发环境。官网只提供了keil、IAR的开发环境的支持。因此首要任务就是编写启动的汇编文件、链接文件。下面就分享这两个文件的编写。

首先这款MCU是基于基于Armv8-M架构的,与他同样的F5270、F5260等都是同一内核的产品,所以可以根据F5260的启动汇编进行代码改写就行了。

【启动汇编代码编写】

通过keil的startup_mm32f5370_keil.c 的文件的分析,阅读MM32F5370的用户手册,他们启动流程是一样的,区别就是中断函数有出入,所以共有部分,可以复制F5260的,然后中断向量,通过keil的启动文件进行编写。最后编写代码如下:

@ ------------------------------------------------------------------------- @ @file: startup_MM32F5370.S @ @purpose: CMSIS Star-MC1 Core Device Startup File @ @ @version: 1.0 @ @date: 2025-01-25 @ @build: lulugl @ ------------------------------------------------------------------------- .syntax unified .arch armv8-m.main #define __INITIAL_SP __StackTop #define __STACK_LIMIT __StackLimit #if defined (__ARM_FEATURE_CMSE) && (__ARM_FEATURE_CMSE == 3U) #define __STACK_SEAL __StackSeal #endif .section .vectors .align 2 .globl __Vectors .globl __Vectors_End .globl __Vectors_Size __Vectors: .long __INITIAL_SP /* Initial Stack Pointer */ .long Reset_Handler /* Reset Handler */ .long NMI_Handler /* -14 NMI Handler */ .long HardFault_Handler /* -13 Hard Fault Handler */ .long MemManage_Handler /* -12 MPU Fault Handler */ .long BusFault_Handler /* -11 Bus Fault Handler */ .long UsageFault_Handler /* -10 Usage Fault Handler */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long SVCall_Handler /* -5 SVCall Handler */ .long DebugMon_Handler /* -4 Debug Monitor Handler */ .long 0 /* Reserved */ .long PendSV_Handler /* -2 PendSV Handler */ .long SysTick_Handler /* -1 SysTick Handler */ .long /* Interrupts */ .long WWDG_IWDG_IRQHandler /* WWDG IWDG */ .long PVD_IRQHandler /* PVD */ .long BKP_TAMPER_IRQHandler /* BKP TAMPER */ .long RTC_IRQHandler /* RTC */ .long FLASH_IRQHandler /* FLASH */ .long RCC_CRS_IRQHandler /* RCC CRS */ .long EXTI0_IRQHandler /* EXTI0 */ .long EXTI1_IRQHandler /* EXTI1 */ .long EXTI2_IRQHandler /* EXTI2 */ .long EXTI3_IRQHandler /* EXTI3 */ .long EXTI4_IRQHandler /* EXTI4 */ .long DMA1_CH1_IRQHandler /* DMA1 Channel1 */ .long DMA1_CH2_IRQHandler /* DMA1 Channel2 */ .long DMA1_CH3_IRQHandler /* DMA1 Channel3 */ .long DMA1_CH4_IRQHandler /* DMA1 Channel4 */ .long DMA1_CH5_IRQHandler /* DMA1 Channel5 */ .long DMA1_CH6_IRQHandler /* DMA1 Channel6 */ .long DMA1_CH7_IRQHandler /* DMA1 Channel7 */ .long ADC1_2_IRQHandler /* ADC1 ADC2 */ .long 0 /* Reserved */ .long DMA1_CH8_IRQHandler /* DMA1 Channel8 */ .long FLEXCAN1_IRQHandler /* FlexCAN1 */ .long 0 /* Reserved */ .long EXTI9_5_IRQHandler /* EXTI9~5 */ .long TIM1_BRK_IRQHandler /* TIM1 BRK */ .long TIM1_UP_IRQHandler /* TIM1 UP */ .long TIM1_TRG_COM_IRQHandler /* TIM1 TRG COM */ .long TIM1_CC_IRQHandler /* TIM1 CC */ .long TIM2_IRQHandler /* TIM2 */ .long TIM3_IRQHandler /* TIM3 */ .long TIM4_IRQHandler /* TIM4 */ .long I2C1_IRQHandler /* I2C1 */ .long 0 /* Reserved */ .long I2C2_IRQHandler /* I2C2 */ .long 0 /* Reserved */ .long SPI1_IRQHandler /* SPI1 */ .long SPI2_IRQHandler /* SPI2 */ .long USART1_IRQHandler /* USART1 */ .long USART2_IRQHandler /* USART2 */ .long USART3_IRQHandler /* USART3 */ .long EXTI15_10_IRQHandler /* EXTI15~10 */ .long RTC_ALR_IRQHandler /* RTCAlarm */ .long USB_WKUP_IRQHandler /* USB WKUP */ .long TIM8_BRK_IRQHandler /* TIM8 BRK */ .long TIM8_UP_IRQHandler /* TIM8 UP */ .long TIM8_TRG_COM_IRQHandler /* TIM8 TRG COM */ .long TIM8_CC_IRQHandler /* TIM8 CC */ .long ADC3_IRQHandler /* ADC3 */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long TIM5_IRQHandler /* TIM5 */ .long SPI3_IRQHandler /* SPI3 */ .long USART4_IRQHandler /* USART4 */ .long USART5_IRQHandler /* USART5 */ .long TIM6_IRQHandler /* TIM6 */ .long TIM7_IRQHandler /* TIM7 */ .long DMA2_CH1_IRQHandler /* DMA2 Channel1 */ .long DMA2_CH2_IRQHandler /* DMA2 Channel2 */ .long DMA2_CH3_IRQHandler /* DMA2 Channel3 */ .long DMA2_CH4_IRQHandler /* DMA2 Channel4 */ .long DMA2_CH5_IRQHandler /* DMA2 Channel5 */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long COMP_IRQHandler /* COMP */ .long FLEXCAN2_IRQHandler /* FlexCAN2 */ .long 0 /* Reserved */ .long USBFS_IRQHandler /* USBFS */ .long DMA2_CH6_IRQHandler /* DMA2 Channel6 */ .long DMA2_CH7_IRQHandler /* DMA2 Channel7 */ .long DMA2_CH8_IRQHandler /* DMA2 Channel8 */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long RAM_IRQHandler /* RAM */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long QSPI_IRQHandler /* QSPI */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long LPTIM_IRQHandler /* LPTIM */ .long 0 /* Reserved */ .long LPUART_IRQHandler /* LPUART */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long 0 /* Reserved */ .long MDPWM_BRK_IRQHandler /* MDPWM_BRK */ .long MDPWM_UPERR_IRQHandler /* MDPWM_UPERR */ .long MDPWM_UP0_IRQHandler /* MDPWM_UP0 */ .long MDPWM_CC0_IRQHandler /* MDPWM_CC0 */ .long MDPWM_UP1_IRQHandler /* MDPWM_UP1 */ .long MDPWM_CC1_IRQHandler /* MDPWM_CC1 */ .long MDPWM_UP2_IRQHandler /* MDPWM_UP2 */ .long MDPWM_CC2_IRQHandler /* MDPWM_CC2 */ .long MDPWM_UP3_IRQHandler /* MDPWM_UP3 */ .long MDPWM_CC3_IRQHandler /* MDPWM_CC3 */ .space (470 * 4) /* Interrupts 10 .. 480 are left out */ __Vectors_End: .equ __Vectors_Size, __Vectors_End - __Vectors .size __Vectors, . - __Vectors .thumb .section .text .align 2 .thumb_func .type Reset_Handler, %function .globl Reset_Handler .fnstart Reset_Handler: ldr r0, =__INITIAL_SP msr psp, r0 ldr r0, =__STACK_LIMIT msr msplim, r0 msr psplim, r0 #if defined (__ARM_FEATURE_CMSE) && (__ARM_FEATURE_CMSE == 3U) ldr r0, =__STACK_SEAL ldr r1, =0xFEF5EDA5U strd r1,r1,[r0,#0] #endif bl SystemInit ldr r4, =__copy_table_start__ ldr r5, =__copy_table_end__ .L_loop0: cmp r4, r5 bge .L_loop0_done ldr r1, [r4] /* source address */ ldr r2, [r4, #4] /* destination address */ ldr r3, [r4, #8] /* word count */ lsls r3, r3, #2 /* byte count */ .L_loop0_0: subs r3, #4 /* decrement byte count */ ittt ge ldrge r0, [r1, r3] strge r0, [r2, r3] bge .L_loop0_0 adds r4, #12 b .L_loop0 .L_loop0_done: ldr r3, =__zero_table_start__ ldr r4, =__zero_table_end__ .L_loop2: cmp r3, r4 bge .L_loop2_done ldr r1, [r3] /* destination address */ ldr r2, [r3, #4] /* word count */ lsls r2, r2, #2 /* byte count */ movs r0, 0 .L_loop2_0: subs r2, #4 /* decrement byte count */ itt ge strge r0, [r1, r2] bge .L_loop2_0 adds r3, #8 b .L_loop2 .L_loop2_done: bl _start .fnend .size Reset_Handler, . - Reset_Handler /* The default macro is not used for HardFault_Handler * because this results in a poor debug illusion. */ .thumb_func .type HardFault_Handler, %function .weak HardFault_Handler .fnstart HardFault_Handler: b . .fnend .size HardFault_Handler, . - HardFault_Handler .thumb_func .type Default_Handler, %function .weak Default_Handler .fnstart Default_Handler: b . .fnend .size Default_Handler, . - Default_Handler /* Macro to define default exception/interrupt handlers. * Default handler are weak symbols with an endless loop. * They can be overwritten by real handlers. */ .macro Set_Default_Handler Handler_Name .weak \Handler_Name .set \Handler_Name, Default_Handler .endm /* Exception Handlers */ Set_Default_Handler NMI_Handler Set_Default_Handler MemManage_Handler Set_Default_Handler BusFault_Handler Set_Default_Handler UsageFault_Handler Set_Default_Handler DebugMonitor_Handler Set_Default_Handler SVCall_Handler Set_Default_Handler PendSV_Handler Set_Default_Handler SysTick_Handler /* Interrupts */ Set_Default_Handler WWDG_IWDG_IRQHandler /* WWDG IWDG */ Set_Default_Handler PVD_IRQHandler /* PVD */ Set_Default_Handler BKP_TAMPER_IRQHandler /* BKP TAMPER */ Set_Default_Handler RTC_IRQHandler /* RTC */ Set_Default_Handler FLASH_IRQHandler /* FLASH */ Set_Default_Handler RCC_CRS_IRQHandler /* RCC CRS */ Set_Default_Handler EXTI0_IRQHandler /* EXTI0 */ Set_Default_Handler EXTI1_IRQHandler /* EXTI1 */ Set_Default_Handler EXTI2_IRQHandler /* EXTI2 */ Set_Default_Handler EXTI3_IRQHandler /* EXTI3 */ Set_Default_Handler EXTI4_IRQHandler /* EXTI4 */ Set_Default_Handler DMA1_CH1_IRQHandler /* DMA1 Channel1 */ Set_Default_Handler DMA1_CH2_IRQHandler /* DMA1 Channel2 */ Set_Default_Handler DMA1_CH3_IRQHandler /* DMA1 Channel3 */ Set_Default_Handler DMA1_CH4_IRQHandler /* DMA1 Channel4 */ Set_Default_Handler DMA1_CH5_IRQHandler /* DMA1 Channel5 */ Set_Default_Handler DMA1_CH6_IRQHandler /* DMA1 Channel6 */ Set_Default_Handler DMA1_CH7_IRQHandler /* DMA1 Channel7 */ Set_Default_Handler ADC1_2_IRQHandler /* ADC1 ADC2 */ Set_Default_Handler DMA1_CH8_IRQHandler /* DMA1 Channel8 */ Set_Default_Handler FLEXCAN1_IRQHandler /* FlexCAN1 */ Set_Default_Handler EXTI9_5_IRQHandler /* EXTI9~5 */ Set_Default_Handler TIM1_BRK_IRQHandler /* TIM1 BRK */ Set_Default_Handler TIM1_UP_IRQHandler /* TIM1 UP */ Set_Default_Handler TIM1_TRG_COM_IRQHandler /* TIM1 TRG COM */ Set_Default_Handler TIM1_CC_IRQHandler /* TIM1 CC */ Set_Default_Handler TIM2_IRQHandler /* TIM2 */ Set_Default_Handler TIM3_IRQHandler /* TIM3 */ Set_Default_Handler TIM4_IRQHandler /* TIM4 */ Set_Default_Handler I2C1_IRQHandler /* I2C1 */ Set_Default_Handler I2C2_IRQHandler /* I2C2 */ Set_Default_Handler SPI1_IRQHandler /* SPI1 */ Set_Default_Handler SPI2_IRQHandler /* SPI2 */ Set_Default_Handler USART1_IRQHandler /* USART1 */ Set_Default_Handler USART2_IRQHandler /* USART2 */ Set_Default_Handler USART3_IRQHandler /* USART3 */ Set_Default_Handler EXTI15_10_IRQHandler /* EXTI15~10 */ Set_Default_Handler RTC_ALR_IRQHandler /* RTCAlarm */ Set_Default_Handler USB_WKUP_IRQHandler /* USB WKUP */ Set_Default_Handler TIM8_BRK_IRQHandler /* TIM8 BRK */ Set_Default_Handler TIM8_UP_IRQHandler /* TIM8 UP */ Set_Default_Handler TIM8_TRG_COM_IRQHandler /* TIM8 TRG COM */ Set_Default_Handler TIM8_CC_IRQHandler /* TIM8 CC */ Set_Default_Handler ADC3_IRQHandler /* ADC3 */ Set_Default_Handler TIM5_IRQHandler /* TIM5 */ Set_Default_Handler SPI3_IRQHandler /* SPI3 */ Set_Default_Handler USART4_IRQHandler /* USART4 */ Set_Default_Handler USART5_IRQHandler /* USART5 */ Set_Default_Handler TIM6_IRQHandler /* TIM6 */ Set_Default_Handler TIM7_IRQHandler /* TIM7 */ Set_Default_Handler DMA2_CH1_IRQHandler /* DMA2 Channel1 */ Set_Default_Handler DMA2_CH2_IRQHandler /* DMA2 Channel2 */ Set_Default_Handler DMA2_CH3_IRQHandler /* DMA2 Channel3 */ Set_Default_Handler DMA2_CH4_IRQHandler /* DMA2 Channel4 */ Set_Default_Handler DMA2_CH5_IRQHandler /* DMA2 Channel5 */ Set_Default_Handler COMP_IRQHandler /* COMP */ Set_Default_Handler FLEXCAN2_IRQHandler /* FlexCAN2 */ Set_Default_Handler USBFS_IRQHandler /* USBFS */ Set_Default_Handler DMA2_CH6_IRQHandler /* DMA2 Channel6 */ Set_Default_Handler DMA2_CH7_IRQHandler /* DMA2 Channel7 */ Set_Default_Handler DMA2_CH8_IRQHandler /* DMA2 Channel8 */ Set_Default_Handler RAM_IRQHandler /* RAM */ Set_Default_Handler QSPI_IRQHandler /* QSPI */ Set_Default_Handler LPTIM_IRQHandler /* LPTIM */ Set_Default_Handler LPUART_IRQHandler /* LPUART */ Set_Default_Handler MDPWM_BRK_IRQHandler /* MDPWM_BRK */ Set_Default_Handler MDPWM_UPERR_IRQHandler /* MDPWM_UPERR */ Set_Default_Handler MDPWM_UP0_IRQHandler /* MDPWM_UP0 */ Set_Default_Handler MDPWM_CC0_IRQHandler /* MDPWM_CC0 */ Set_Default_Handler MDPWM_UP1_IRQHandler /* MDPWM_UP1 */ Set_Default_Handler MDPWM_CC1_IRQHandler /* MDPWM_CC1 */ Set_Default_Handler MDPWM_UP2_IRQHandler /* MDPWM_UP2 */ Set_Default_Handler MDPWM_CC2_IRQHandler /* MDPWM_CC2 */ Set_Default_Handler MDPWM_UP3_IRQHandler /* MDPWM_UP3 */ Set_Default_Handler MDPWM_CC3_IRQHandler /* MDPWM_CC3 */ .end

【链接文件】

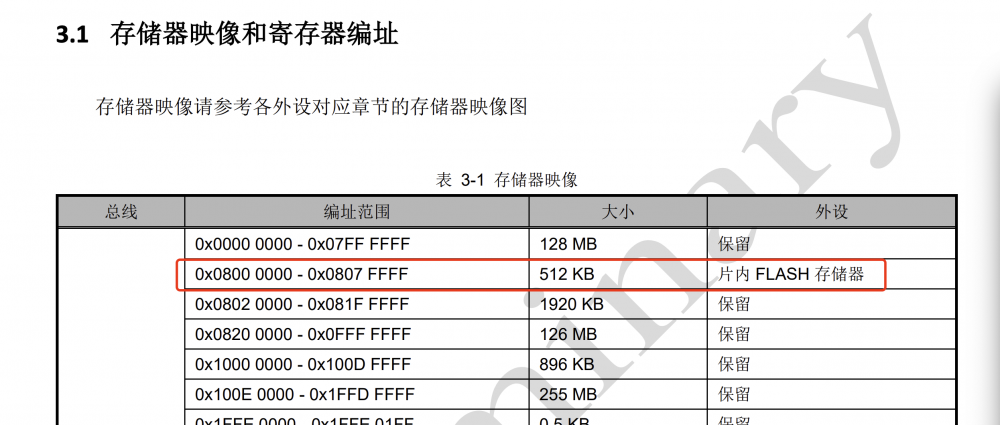

通过对用户手册文件进行查找,首先查找到flash的大小为512K,起始地址为0x80000000

/*---------------------- Flash Configuration ---------------------------------- <h> Flash Configuration <o0> Flash Base Address <0x0-0xFFFFFFFF:8> <o1> Flash Size (in Bytes) <0x0-0xFFFFFFFF:8> </h> -----------------------------------------------------------------------------*/ __ROM_BASE = 0x08000000; __ROM_SIZE = 0x00080000;

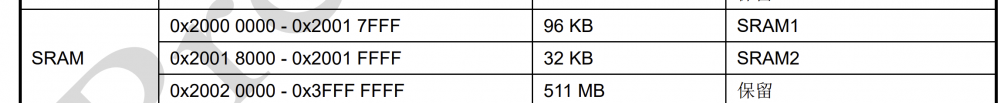

然后查找内存起始地址与大小:

/*---------------------- RAM Configuration ------------------------------------ <h> RAM Configuration <o0> RAM Base Address <0x0-0xFFFFFFFF:8> <o1> RAM Size (in Bytes) <0x0-0xFFFFFFFF:8> </h> -----------------------------------------------------------------------------*/ __RAM_BASE = 0x20000000; __RAM_SIZE = 0x00020000;

再定义堆栈大小:

/*--------------------- Stack / Heap Configuration ---------------------------- <h> Stack / Heap Configuration <o0> Stack Size (in Bytes) <0x0-0xFFFFFFFF:8> <o1> Heap Size (in Bytes) <0x0-0xFFFFFFFF:8> </h> -----------------------------------------------------------------------------*/ __STACK_SIZE = 0x00001000; __HEAP_SIZE = 0x00001000;

总体源码如下:

/*

*-------- <<< Use Configuration Wizard in Context Menu >>> -------------------

*/

/*---------------------- Flash Configuration ----------------------------------

<h> Flash Configuration

<o0> Flash Base Address <0x0-0xFFFFFFFF:8>

<o1> Flash Size (in Bytes) <0x0-0xFFFFFFFF:8>

</h>

-----------------------------------------------------------------------------*/

__ROM_BASE = 0x08000000;

__ROM_SIZE = 0x00080000;

/*---------------------- RAM Configuration ------------------------------------

<h> RAM Configuration

<o0> RAM Base Address <0x0-0xFFFFFFFF:8>

<o1> RAM Size (in Bytes) <0x0-0xFFFFFFFF:8>

</h>

-----------------------------------------------------------------------------*/

__RAM_BASE = 0x20000000;

__RAM_SIZE = 0x00020000;

/*--------------------- Stack / Heap Configuration ----------------------------

<h> Stack / Heap Configuration

<o0> Stack Size (in Bytes) <0x0-0xFFFFFFFF:8>

<o1> Heap Size (in Bytes) <0x0-0xFFFFFFFF:8>

</h>

-----------------------------------------------------------------------------*/

__STACK_SIZE = 0x00001000;

__HEAP_SIZE = 0x00001000;

/*

*-------------------- <<< end of configuration section >>> -------------------

*/

/* ARMv8-M stack sealing:

to use ARMv8-M stack sealing set __STACKSEAL_SIZE to 8 otherwise keep 0

*/

__STACKSEAL_SIZE = 0;

MEMORY

{

FLASH (rx) : ORIGIN = __ROM_BASE, LENGTH = __ROM_SIZE

RAM (rwx) : ORIGIN = __RAM_BASE, LENGTH = __RAM_SIZE

}

/* Linker script to place sections and symbol values. Should be used together

* with other linker script that defines memory regions FLASH and RAM.

* It references following symbols, which must be defined in code:

* Reset_Handler : Entry of reset handler

*

* It defines following symbols, which code can use without definition:

* __exidx_start

* __exidx_end

* __copy_table_start__

* __copy_table_end__

* __zero_table_start__

* __zero_table_end__

* __etext

* __data_start__

* __preinit_array_start

* __preinit_array_end

* __init_array_start

* __init_array_end

* __fini_array_start

* __fini_array_end

* __data_end__

* __bss_start__

* __bss_end__

* __end__

* end

* __HeapLimit

* __StackLimit

* __StackTop

* __stack

* __StackSeal (only if ARMv8-M stack sealing is used)

*/

ENTRY(Reset_Handler)

SECTIONS

{

.text :

{

KEEP(*(.vectors))

*(.text*)

KEEP(*(.init))

KEEP(*(.fini))

/* .ctors */

*crtbegin.o(.ctors)

*crtbegin?.o(.ctors)

*(EXCLUDE_FILE(*crtend?.o *crtend.o) .ctors)

*(SORT(.ctors.*))

*(.ctors)

/* .dtors */

*crtbegin.o(.dtors)

*crtbegin?.o(.dtors)

*(EXCLUDE_FILE(*crtend?.o *crtend.o) .dtors)

*(SORT(.dtors.*))

*(.dtors)

*(.rodata*)

KEEP(*(.eh_frame*))

} > FLASH

/*

* SG veneers:

* All SG veneers are placed in the special output section .gnu.sgstubs. Its start address

* must be set, either with the command line option ��--section-start�� or in a linker script,

* to indicate where to place these veneers in memory.

*/

/*

.gnu.sgstubs :

{

. = ALIGN(32);

} > FLASH

*/

.ARM.extab :

{

*(.ARM.extab* .gnu.linkonce.armextab.*)

} > FLASH

__exidx_start = .;

.ARM.exidx :

{

*(.ARM.exidx* .gnu.linkonce.armexidx.*)

} > FLASH

__exidx_end = .;

.copy.table :

{

. = ALIGN(4);

__copy_table_start__ = .;

LONG (__etext)

LONG (__data_start__)

LONG ((__data_end__ - __data_start__) / 4)

/* Add each additional data section here */

/*

LONG (__etext2)

LONG (__data2_start__)

LONG ((__data2_end__ - __data2_start__) / 4)

*/

__copy_table_end__ = .;

} > FLASH

.zero.table :

{

. = ALIGN(4);

__zero_table_start__ = .;

/* Add each additional bss section here */

/*

LONG (__bss2_start__)

LONG ((__bss2_end__ - __bss2_start__) / 4)

*/

__zero_table_end__ = .;

} > FLASH

/**

* Location counter can end up 2byte aligned with narrow Thumb code but

* __etext is assumed by startup code to be the LMA of a section in RAM

* which must be 4byte aligned

*/

__etext = ALIGN (4);

.data : AT (__etext)

{

__data_start__ = .;

*(vtable)

*(.data)

*(.data.*)

. = ALIGN(4);

/* preinit data */

PROVIDE_HIDDEN (__preinit_array_start = .);

KEEP(*(.preinit_array))

PROVIDE_HIDDEN (__preinit_array_end = .);

. = ALIGN(4);

/* init data */

PROVIDE_HIDDEN (__init_array_start = .);

KEEP(*(SORT(.init_array.*)))

KEEP(*(.init_array))

PROVIDE_HIDDEN (__init_array_end = .);

. = ALIGN(4);

/* finit data */

PROVIDE_HIDDEN (__fini_array_start = .);

KEEP(*(SORT(.fini_array.*)))

KEEP(*(.fini_array))

PROVIDE_HIDDEN (__fini_array_end = .);

KEEP(*(.jcr*))

. = ALIGN(4);

/* All data end */

__data_end__ = .;

} > RAM

/*

* Secondary data section, optional

*

* Remember to add each additional data section

* to the .copy.table above to asure proper

* initialization during startup.

*/

/*

__etext2 = ALIGN (4);

.data2 : AT (__etext2)

{

. = ALIGN(4);

__data2_start__ = .;

*(.data2)

*(.data2.*)

. = ALIGN(4);

__data2_end__ = .;

} > RAM2

*/

.bss :

{

. = ALIGN(4);

__bss_start__ = .;

*(.bss)

*(.bss.*)

*(COMMON)

. = ALIGN(4);

__bss_end__ = .;

} > RAM AT > RAM

/*

* Secondary bss section, optional

*

* Remember to add each additional bss section

* to the .zero.table above to asure proper

* initialization during startup.

*/

/*

.bss2 :

{

. = ALIGN(4);

__bss2_start__ = .;

*(.bss2)

*(.bss2.*)

. = ALIGN(4);

__bss2_end__ = .;

} > RAM2 AT > RAM2

*/

.heap (COPY) :

{

. = ALIGN(8);

__end__ = .;

PROVIDE(end = .);

. = . + __HEAP_SIZE;

. = ALIGN(8);

__HeapLimit = .;

} > RAM

.stack (ORIGIN(RAM) + LENGTH(RAM) - __STACK_SIZE - __STACKSEAL_SIZE) (COPY) :

{

. = ALIGN(8);

__StackLimit = .;

. = . + __STACK_SIZE;

. = ALIGN(8);

__StackTop = .;

} > RAM

PROVIDE(__stack = __StackTop);

/* ARMv8-M stack sealing:

to use ARMv8-M stack sealing uncomment '.stackseal' section

*/

/*

.stackseal (ORIGIN(RAM) + LENGTH(RAM) - __STACKSEAL_SIZE) (COPY) :

{

. = ALIGN(8);

__StackSeal = .;

. = . + 8;

. = ALIGN(8);

} > RAM

*/

/* Check if data + heap + stack exceeds RAM limit */

ASSERT(__StackLimit >= __HeapLimit, "region RAM overflowed with stack")

}到此必须的文 件就编写好,放入工程中进行编译测试:

[HEX] build_exec/template.elf -> build_exec/template.hex [BIN] build_exec/template.elf -> build_exec/template.bin [DUMP] build_exec/template.elf -> build_exec/template.S [SIZE] build_exec/template.elf text data bss dec hex filename 24396 504 368 25268 62b4 build_exec/template.elf -e Build Finish

这样就成功的编写在GCC下面编译环境的必需文件的编写。

我要赚赏金

我要赚赏金