如果设计好一个可靠的电源,需要对电源有一定的计划。

1. 电源需求分析

电压范围,确定每个器件所需的电压范围,3.3V、1.8V、1.2V等。

电流需求,计算每个器件在不同工作状态下的电流需求,确保电源能够提供足够的电流。

动态响应,分析电源在负载变化时的响应速度,确保电源能够快速调整输出电压以应对负载变化。

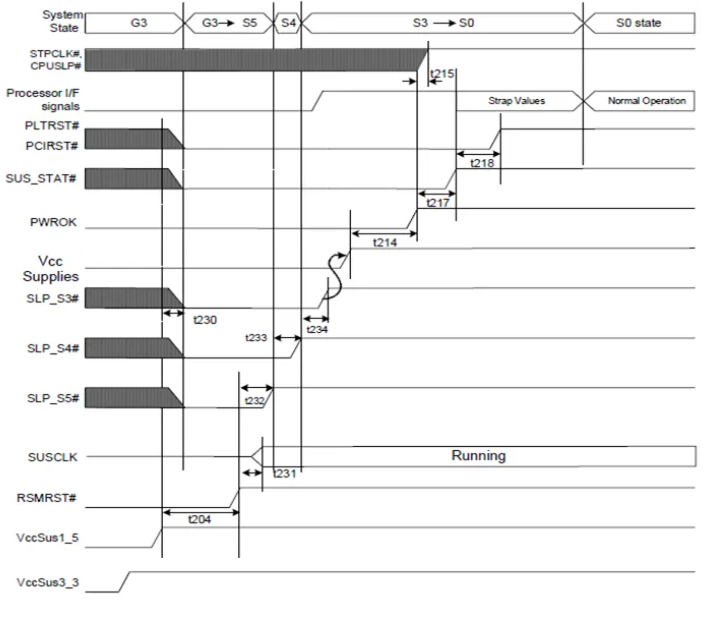

上电时序,确定各个电源的上电顺序和时间间隔,确保器件能够按照正确的顺序上电。

2. 电源设计

电源合并,对于相同电压的器件,尽量使用同一个电源输出,简化设计。

电源管理,使用电源管理芯片(PMIC)来实现复杂的上电时序和电压调节。

电源监控,添加电源监控电路,实时监测电源状态,确保系统稳定运行。

3. 案例分析

Intel器件,根据Intel提供的电源上电时序要求,设计相应的电源管理电路。

其他器件,分析网卡、FPGA等器件的电源需求,确保与Intel器件的电源设计兼容。

时钟专题分析

1. 时钟需求分析

电平标准,确定每个时钟输入的电平标准,LVDS、LVCMOS。

频率,确定每个时钟的频率需求,确保时钟信号能够满足器件的操作要求。

抖动,分析时钟信号的抖动特性,确保时钟信号的稳定性。

时钟时序,确定各个时钟信号的时序关系,确保器件能够按照正确的时序操作。

2. 时钟设计

时钟分配,使用时钟分配芯片或FPGA内部的时钟管理模块来分配时钟信号。

时钟优化,根据抖动和时序要求,优化时钟电路设计,使用低抖动时钟源、添加时钟缓冲器等。

时钟监控,添加时钟监控电路,实时监测时钟信号的质量。

3. 案例分析

时钟解决方案,根据器件的时钟需求,选择合适的时钟解决方案,使用PLL、DLL等。

管脚连接,分析每个时钟管脚的连接方式,确保电平标准和时序要求得到满足。

先看时钟树:

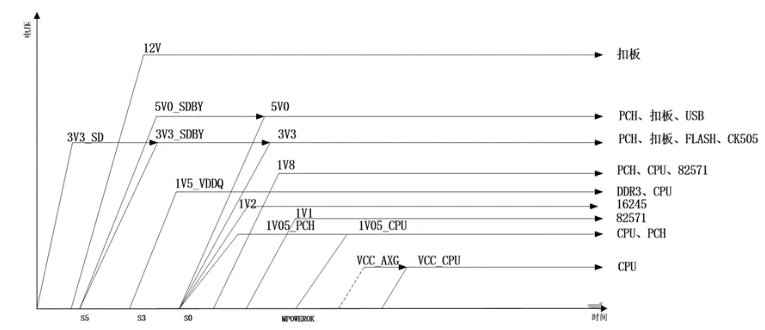

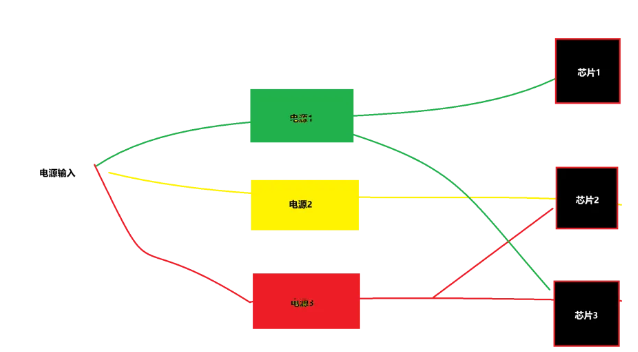

梳理出所有器件的用电需求,然后再合并共性需求。整理出整个单板的供电需求,以及供电时序的要求,如图所示。

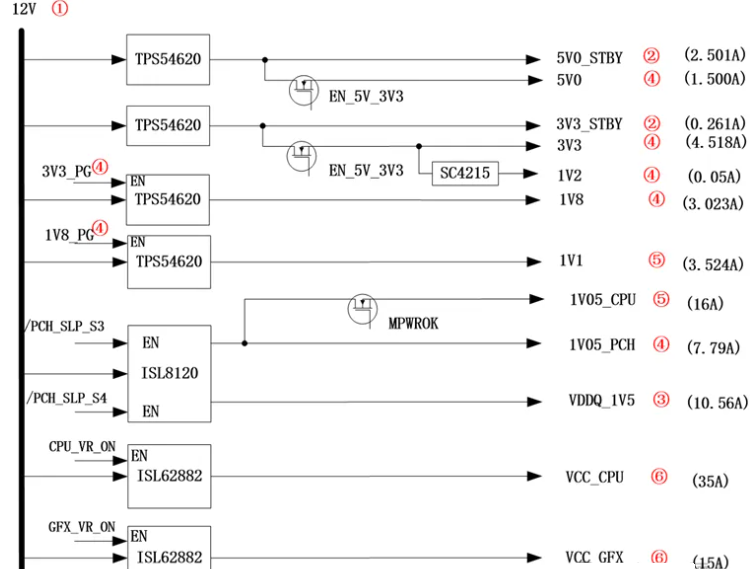

然后再根据需求,设计整板的电源方案,选择最合理、可靠性、性价比的电源方案,实现我们的整板电源方案。先形成功能框图,进行评审。

关键图表和文档

电源需求分析表:列出所有器件的电源需求,包含电压范围、电流需求、动态响应和上电时序等信息。

共性需求合并图:展示不同电压的器件合并后的供电需求。

整板电源方案框图:展示整板的电源架构设计,包括各个电源模块和它们之间的连接关系。

上电时序图:详细说明各个电源模块的上电顺序和时序要求,确保满足所有器件的需求。

文档化

1. 电源文档

电源需求表:列出所有器件的电源需求,包括电压范围、电流需求、动态响应和上电时序。

电源设计图:绘制电源设计图,标注各个电源的输出电压、电流和上电时序。

电源测试报告:记录电源测试结果,包括电压稳定性、动态响应和上电时序的验证。

2. 时钟文档

时钟需求表:列出所有器件的时钟需求,包括电平标准、频率、抖动和时序要求。

时钟设计图:绘制时钟设计图,标注各个时钟信号的频率、抖动和时序关系。

时钟测试报告:记录时钟测试结果,包括频率稳定性、抖动特性和时序验证。

下面结合实际来分析:

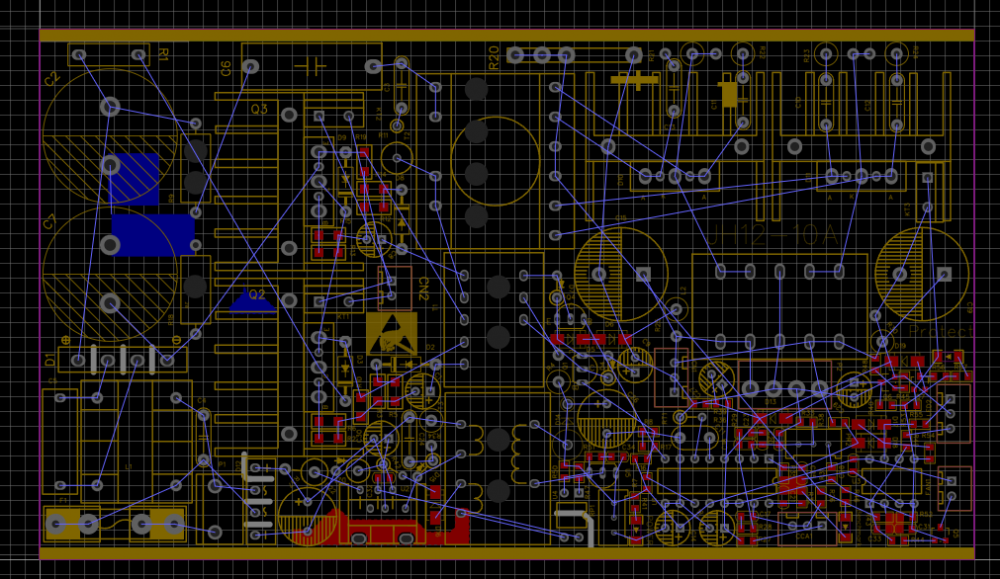

电源模块布局思考

在设计电源模块布局时,需要综合考虑电源输入和输出的情况,特别是主芯片及其配套大功率芯片的电源需求。

1. 电源输入布局

电源输入通常由背板、适配器、PoE、USB等形式提供直流输入。

输入合路设计,如果有多路输入,需设计合路电路,确保输入电源的稳定性和可靠性。

输入滤波,在电源输入处添加滤波电路电容、电感,减少噪声和干扰。

输入保护,添加过压、过流保护电路,防止异常情况损坏后续电路。

2. 电源输出布局

电源输出需根据用电器件的电源需求进行整理和合并,

器件位置关系,根据器件的位置分布,优化电源走线,减少路径长度和阻抗。

大电流电源优先,优先考虑主芯片及大功率芯片DDR的电源管脚分布,确保大电流路径最短、阻抗最低。

3. 主芯片电源布局

主芯片的电源布局是关键,

电源平面分配:

根据主芯片的电源管脚分布,合理分配电源平面。

确保每个电源平面独立,减少耦合,避免电源平面交织。

路径优化:

电源走线应尽量短,避免“绕远路”。

减少换层次数,降低阻抗和噪声。

完整电源平面:

关键电源CPU核心电源应尽量使用完整的电源平面,确保电流分布均匀,减少电压降。

去耦电容布置:

在主芯片的电源管脚附近布置去耦电容,提供瞬态电流,减少电源噪声。

4. 布局优化建议

减小耦合:

不同电源平面之间应保持足够距离,避免信号干扰。

使用地平面隔离不同电源平面,减少耦合。

最短路径:

电源走线应尽量短且直,减少路径阻抗和损耗。

大电流路径应加宽走线,降低电阻和温升。

减少换层:

尽量减少电源走线的换层次数,避免引入额外的阻抗和噪声。

如果必须换层,应在换层处添加过孔,并确保过孔数量和尺寸足够。

完整电源平面:

关键电源CPU核心电源应尽量使用完整的电源平面,确保电流分布均匀。

对于非关键电源,可以使用局部电源平面或走线。

5. 实际案例分析

以CPU和DDR电源为例:

CPU核心电源:

使用完整的电源平面,确保电流分布均匀。

在CPU电源管脚附近布置多个去耦电容,提供瞬态电流。

DDR电源:

根据DDR芯片的位置,优化电源走线,减少路径长度。

使用局部电源平面,确保电源稳定性。

输入电源不要满板跑

这是一条很简单的原则,但是容易被大家忽略。

第一、输入电源是外部供电,其引入的干扰不可控;

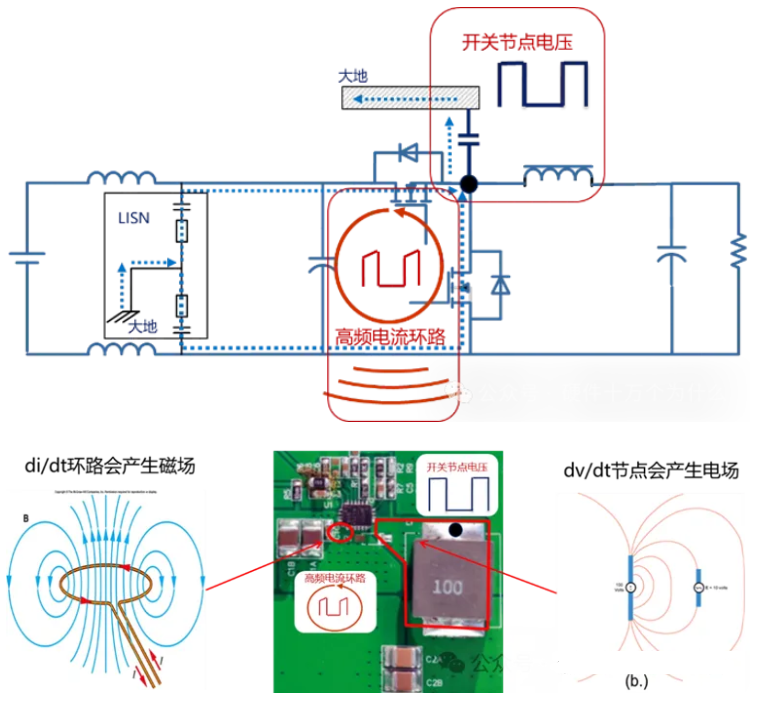

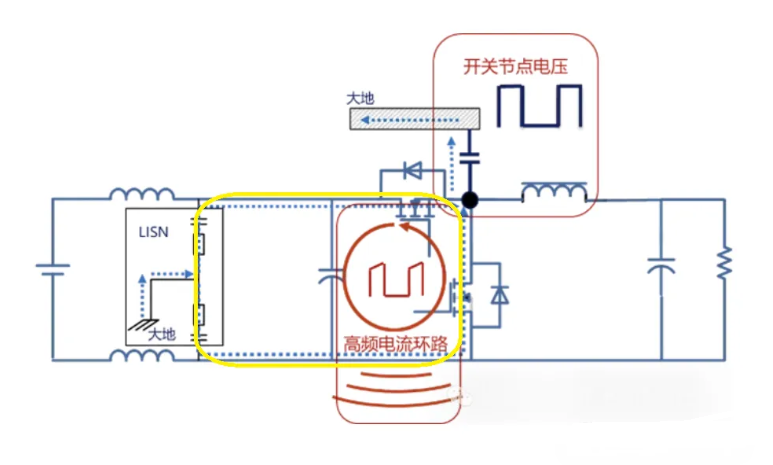

第二、输入电源给每个DC/DC供电,每个DC/DC的输入电容都往往都会有大功率的电流跳变,需要控制这个电流环的大小。

第三、即使通过空电流环的大小,输入电源与DC/DC之间会仍然会形成跳变的电流环,形成一个感性干扰源。

我们既要控制红色的环,也要控制黄色的环。

总结:电源和时钟的设计流程,包括需求分析、设计、案例分析等关键环节。通过电源需求分析表、共性需求合并图等图表,梳理出整板的供电需求和供电时序要求。在电源布局方面,需综合考虑输入和输出情况,优化走线、减小耦合、使用完整电源平面等策略。时钟设计也需关注电平标准、频率、抖动和时序要求。通过文档化记录设计过程和测试结果,确保电源和时钟的稳定性和可靠性。

我要赚赏金

我要赚赏金