接着上篇继续电源控制。

上篇连接:

https://forum.eepw.com.cn/thread/393692/1

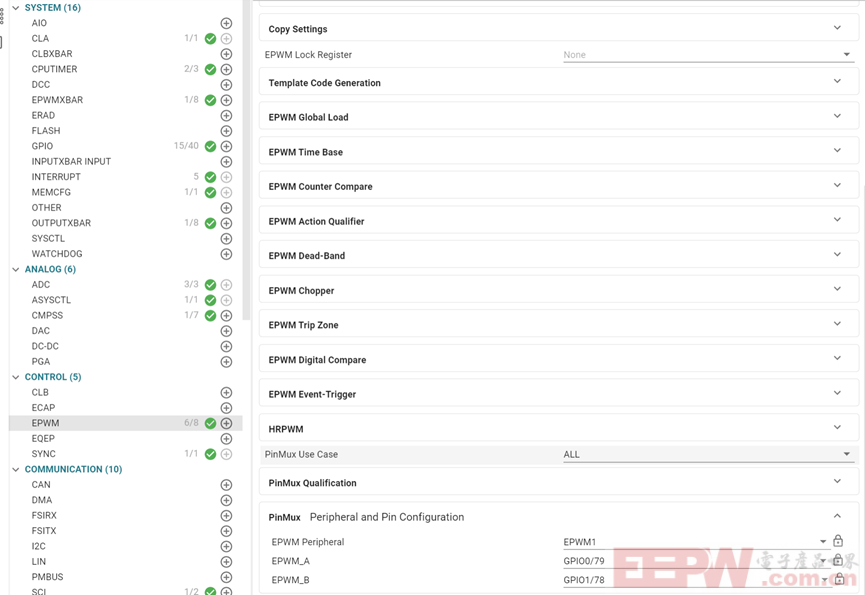

epwm部分

图中EPWM配置界面

核心功能配置

基础波形生成

Time Base,配置计数器工作模式(增/减/增减计数)、周期值(EPWM1_PERIOD)和时钟分频,决定PWM频率。若周期值=1000,系统时钟=100MHz → PWM频率=100kHz(增计数模式)。

Counter Compare,设置比较寄存器(CMPA/CMPB)值,控制占空比。结合Action Qualifier生成高低电平切换点。

输出控制

Action Qualifier,定义计数器匹配时的动作,CMPA匹配时拉高/拉低EPWMxA,CMPB匹配时翻转EPWMxB,用于生成互补PWM。

Dead-Band,插入死区时间(纳秒级),防止H桥上下管直通。支持上升沿/下降沿独立延迟配置。

高精度控制

HRPWM(高分辨率PWM),启用150ps级分辨率,适用于LLC谐振转换器等需精确时序的场景。

保护机制配置

Trip Zone硬件故障保护过流/过压触发时,强制PWM输出预设安全状态(高阻/拉低)。支持多级触发源(如GPIO、ADC故障信号)。

Digital Compare数字比较器实时监控PWM信号,触发条件(如占空比超限)可联动Trip Zone。

Event-Trigger配置ADC启动触发信号PWM周期中点采样,实现电流环同步采样。

引脚映射(PinMux)

EPWM1A → GPIO0/79

EPWM1B → GPIO1/78

将内部PWM信号路由到物理引脚,驱动外部功率器件(如MOSFET/IGBT)。

其他配置

Chopper,启用高频载波调制20kHz,减少电机驱动中的可闻噪声。

Global Load,同步更新多个寄存器CMPA/CMPB,避免动态调整时的波形畸变。

全桥互补波的SYSCONFIG配置,这里主要进行死区的配置

Sysctl enablePeripheral(SYSCTL PERIPH CLK TBCLKSYNC);

使用这行代码,同步两路互补波的时钟。

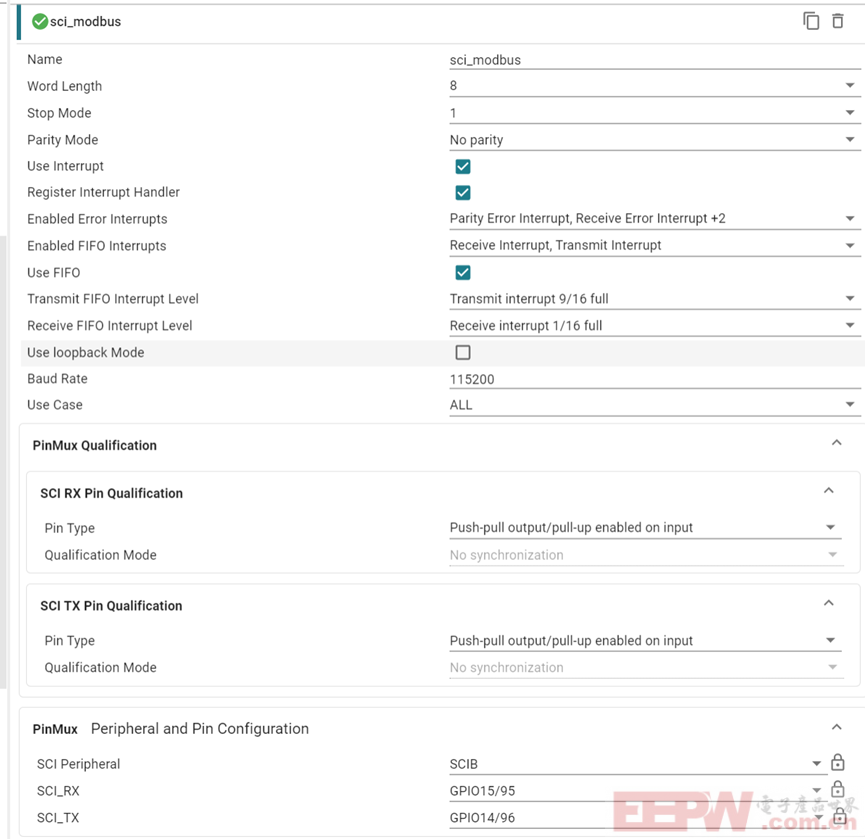

SCI +FIFO部分

SCI+FIFO的sysconfig配置

// 调试提示 - 需在硬件调试时使能DE引脚(用于RS485收发控制)

// GCK:注意后面这里实际调试的时候要使能DE引脚

// 定义串口接收中断服务函数(Modbus协议)

__interrupt void INT_sci_modbus_RX_ISR(void) {

// 检查并处理串口接收错误

if ((SCI_getRxStatus(sci_modbus_BASE) & SCI_RXSTATUS_ERROR) == SCI_RXSTATUS_ERROR) {

// 411行:清除接收错误中断标志(如帧错误/奇偶校验错)

SCI_clearInterruptStatus(sci_modbus_BASE, SCI_INT_RXERR);

// 强制复位接收FIFO(错误状态下必须复位才能恢复通信)

SCI_resetRxFIFO(sci_modbus_BASE);

// 停止超时定时器(防止错误状态下的误触发)

CPUTimer_stopTimer(CPUTIMER2_BASE);

// 清零接收计数器(丢弃错误数据)

rcvcounter = 0;

}

// 正常数据接收处理

else {

/* 从FIFO读取数据直到清空或缓冲区满 */

while (SCI_getRxFIFOStatus(sci_modbus_BASE) != SCI_FIFO_RX0

&& rcvcounter < RX_BUFFER_LEN) {

// 非阻塞读取字符并存入缓冲区

rcvbuffer[rcvcounter++] = SCI_readCharNonBlocking(sci_modbus_BASE);

}

}

// 启动空闲超时检测(收到数据后重置定时器)

if (rcvcounter != 0) {

// GCK注释:通过CPUTIMER2检测帧间隔超时

CPUTimer_reloadTimerCounter(CPUTIMER2_BASE); // 重载定时器计数值

CPUTimer_startTimer(CPUTIMER2_BASE); // 启动定时器

}

// 清除接收FIFO中断标志(允许下次中断触发)

SCI_clearInterruptStatus(sci_modbus_BASE, SCI_INT_RXFF);

// 清除PIE中断组应答标志(关键!否则无法响应后续中断)

Interrupt_clearACKGroup(INT_sci_modbus_RX_INTERRUPT_ACK_GROUP);

}SCI接收中断

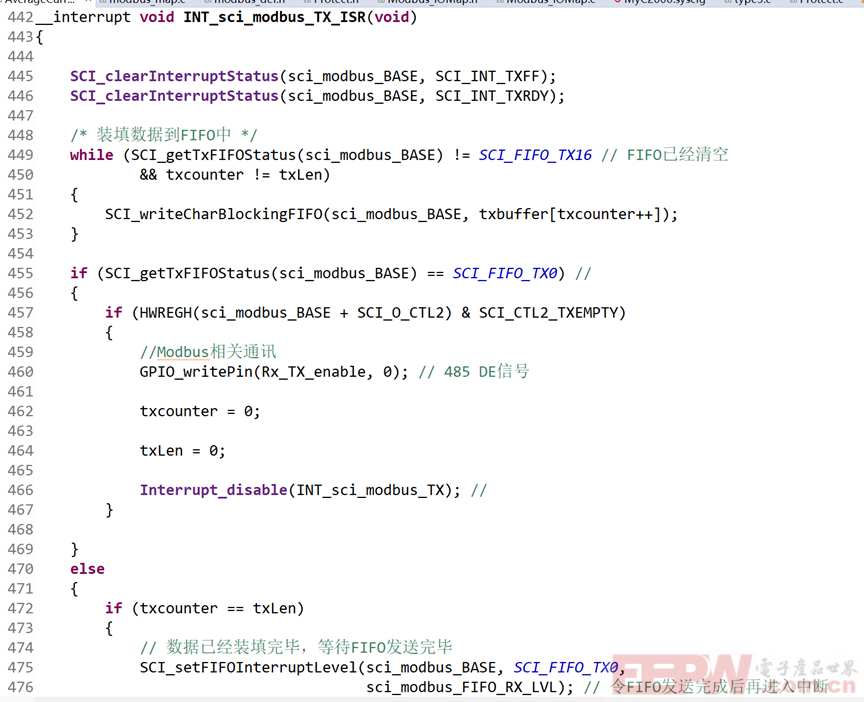

// Modbus发送中断服务函数声明

// - 触发条件:SCI发送FIFO状态变化(如FIFO空或阈值触发)

interrupt void INT_sci_modbus_TX_ISR(void) {

// 444-445:清除发送中断标志(双重清理确保可靠性)

SCI_clearInterruptStatus(sci_modbus_BASE, SCI_INT_TXFF); // 清除FIFO中断

SCI_clearInterruptStatus(sci_modbus_BASE, SCI_INT_TXRDY); // 清除发送就绪中断

// 向发送FIFO填充待传输数据

// - 循环条件:FIFO未满(!=SCI_FIFO_TX16)且缓冲区数据未发完(txcounter != txLen)

while (SCI_getTxFIFOStatus(sci_modbus_BASE) != SCI_FIFO_TX16 && txcounter != txLen) {

// 451:阻塞式写入字符到FIFO(自动触发硬件发送)

SCI_writeCharBlockingFIFO(sci_modbus_BASE, txbuffer[txcounter++]);

}

// 检查发送完成条件

if (SCI_getTxFIFOStatus(sci_modbus_BASE) == SCI_FIFO_TX0) { // FIFO完全空

// 455:检查发送移位寄存器是否空闲(确保最后一字节已发出)

if (HWREGH(sci_modbus_BASE + SCI_O_CTL2) & SCI_CTL2_TXEMPTY) {

// 457-462:Modbus通信结束处理

GPIO_writePin(Rx_TX_enable, 0); // RS485切换到接收模式(DE=0)

txcounter = 0; // 重置发送计数器

txLen = 0; // 清空数据长度标记

Interrupt_disable(INT_sci_modbus_TX); // 关闭发送中断(等待新数据)

}

}

// 未发送完但FIFO已空时的处理

else {

if (txcounter == txLen) { // 数据已全部装入FIFO,但未物理发送完毕

// 469-470:设置FIFO中断触发阈值为空(SCI_FIFO_TX0)

// - 当FIFO完全空时再次触发中断,执行最终状态检查

SCI_setFIFOInterruptLevel(sci_modbus_BASE, SCI_FIFO_TX0, SCI_modbus_FIFO_RX_LVL);

}

}

}

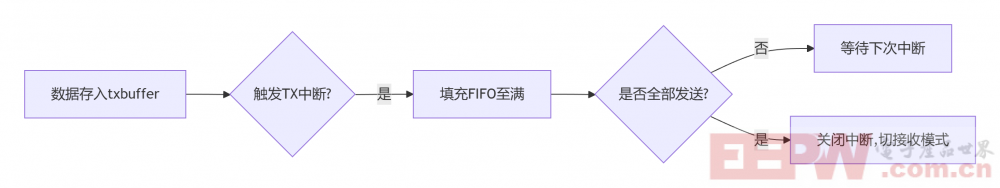

实际判断工作流程:

SCI发送中断

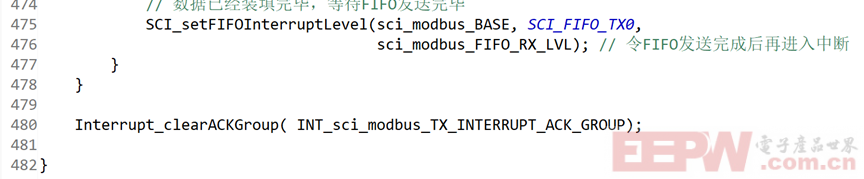

// 重设FIFO中断触发条件为"完全空"(SCI_FIFO_TX0) // - 目的:仅在FIFO和移位寄存器均空时触发中断,确保最后一字节已发出 // - 参数1:sci_modbus_BASE -> SCI模块基地址 // - 参数2:SCI_FIFO_TX0 -> 发送FIFO空触发阈值(0字节剩余) // - 参数3:sci_modbus_FIFO_RX_LVL -> 接收FIFO中断阈值(保持原配置) SCI_setFIFOInterruptLevel(sci_modbus_BASE, SCI_FIFO_TX0, sci_modbus_FIFO_RX_LVL); // 代码块结束符(对应前文的if/while逻辑) // 清除PIE中断组应答标志(关键操作!) // - 作用:允许后续同类型中断再次触发 // - 参数:INT_sci_modbus_TX_INTERRUPT_ACK_GROUP -> SCI发送中断所属的PIE组号 Interrupt_clearACKGroup(INT_sci_modbus_TX_INTERRUPT_ACK_GROUP); // 函数结束符(中断服务程序结尾)

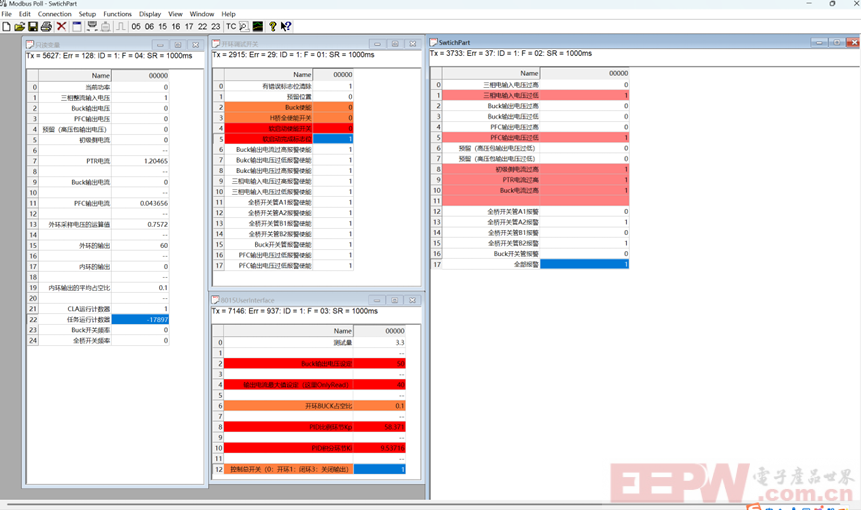

modbus上位机界面

epwm+compare的测试

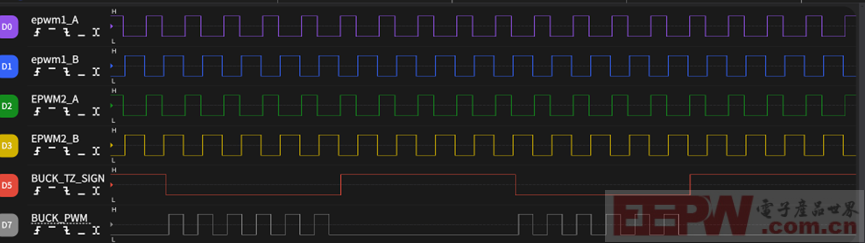

逻辑分析仪测试图片

对全桥和Buck的输出的pwm进行测试,可以看到全桥的A和B是一路互补的波形,epwm1和EPM2的时序相同,符合预期。对于Buck的pwm的OST模式进行测试,在BUCK_TZ_SIGNAl信号拉高时,BUCK_PWM信号被强制拉低。错误联防有效。

我要赚赏金

我要赚赏金