本文主要讲述芯片制造中的对准技术。

三维集成电路制造中,对准技术是确保多层芯片键合精度、实现高密度TSV与金属凸点正确互联的核心技术,直接影响芯片性能与集成密度,其高精度可避免互连失效或错误,并支持更小尺寸的TSV与凸点以节约面积。

主流量产采用“对准与键合分离”方案,先在专用设备完成高精度对准再转移键合,有效规避温度变化、硅片翘曲等因素干扰,同时通过分解键合前对准误差与键合滑移误差优化工艺,提升设备利用率。影响精度的关键因素包括键合方式(直接键合滑移小、精度高,高分子键合易滑移)、材料特性(CTE差异导致翘曲,临时键合中玻璃载片翘曲控制是重点)及表面形貌等;对准方法分直接与间接:透明材料(如去衬底SOI器件层)可通过双显微镜直接观测参考点对准,不透明材料则需间接对准(先固定一层参考点再调整另一层,精度稍低)。

当前主流技术涵盖晶圆级(红外/光学透视)、倒装芯片(光学系统定位)及自组装对准,其中SOI的创新应用通过透明结构实现光刻级高精度对准,推动3D IC向更小、更快、更集成方向演进。

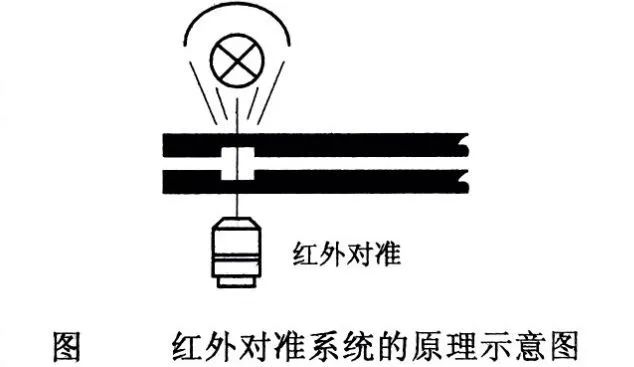

红外对准

红外对准技术作为三维集成电路键合工艺中的核心手段,凭借硅材料对近红外光(1.1-1.3eV)的透明特性,通过1.2μm波长左右的红外光源穿透硅片,实现上下层对准标记的精准定位,是早期键合对准的代表性技术。

其原理在于:红外光从晶圆底部照射,经由CCD或红外显微镜捕捉透射图像,通过调整两层硅片的相对位置完成对准,随后直接键合,有效避免了分离式对准中温度变化和硅片翘曲带来的误差。该技术设备结构简单、调整灵活,且支持原位对准,但受材料限制显著——硅氧化物(SiO₂)、氮化物(Si₃N₄)及金属互连层对红外光的吸收与反射会干扰成像,需通过预留对准窗口或采用双面抛光的高等级晶圆(厚度≤300μm)来优化透过率,同时需控制硅片电阻率(>0.01Ω·cm)以避免红外吸收率过高。

精度方面,红外对准的分辨率受波长、镜头放大倍数及机械系统控制精度影响,通常采用最短可用红外波长以提升可视度,并通过减小两层硅片间隙、将对准标记置于相对表面来降低偏差。近年来,推出的近红外显微镜系统(如MIR400)进一步优化了光学设计,支持900-1700nm波段、0.8μm分辨率的透射成像,结合长工作距离物镜(15mm)与高精度电动平台(重复定位精度0.5μm),实现了键合过程的实时监控与闭环控制,显著提升了工艺稳定性。

应用场景上,红外对准主要适用于晶圆级键合(W2W),在芯片级倒装(D2D)中因对准窗口尺寸大、互连布局干扰等问题应用受限,但通过绝缘体上硅(SOI)技术去除衬底后,器件层与玻璃辅助晶圆的透明化处理,可扩展其应用范围。材料与工艺层面,除晶圆抛光外,新型红外穿透塑料(如PC、PMMA)通过模具精度优化(表面粗糙度Ra<0.01μm)与注塑工艺改进,已实现90%以上的红外透过率,有效减少了表面散射对成像的干扰;同时,键合工艺参数(如超声功率110-120DAC、接触力25-35gf)的优化,提升了金丝键合的拉力值与信号传输可靠性,进一步保障了红外对准后的键合质量。

行业最新进展显示,红外对准技术正与机器视觉及AI深度融合,例如通过近红外图像的多光谱融合与深度学习算法,可自动识别复杂背景下的对准标记,降低人工干预需求;此外,中波红外(MWIR)传感器技术的突破(如非制冷量子点探测器、二维材料异质结),为未来更高精度的红外对准设备提供了性能更优、成本更低的检测组件,推动该技术向更微小尺寸TSV与更高密度3D集成方向发展。

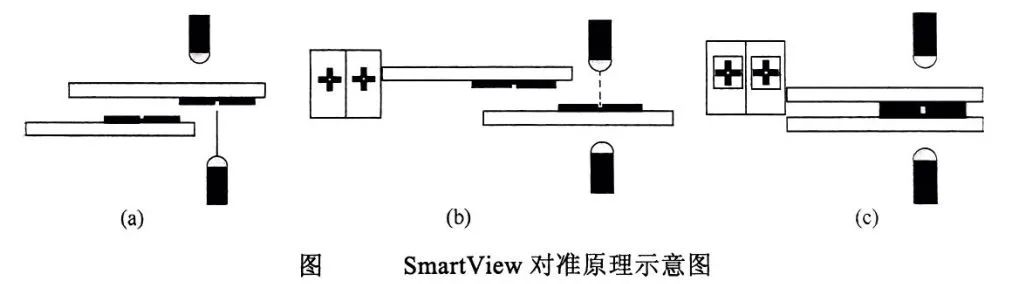

光学对准

光学对准技术作为三维集成电路键合工艺中实现高精度定位的核心手段,凭借其抗干扰能力强、适配性广及精度可控等优势,已成为量产设备的主流对准方案,有效弥补了红外对准在复杂材料环境下的性能局限。其核心原理在于通过可见光或特定波段光学系统直接观测上下层硅片的对准标记,结合精密机械调整实现位置匹配,过程直观且调整灵活。

早期代表性技术为背面对准方法,主要用于MEMS双面光刻领域。该技术通过将两层硅片面对背放置,使对准标记均朝向光学显微镜方向,利用间接位置调整完成对准,随后转移至键合机固定。其特点是对准标记朝向一致,但硅片物理方向相反,操作相对简单,但精度受限于标记间接调整的误差累积。

为进一步提升精度,推出SmartView技术,采用双显微镜双向观测系统:先固定第一层硅片并记录其物理位置,再通过上方显微镜捕捉第二层标记,计算两层相对位置差异后调整,实现面对面放置的高精度对准。尽管设备复杂度增加,但标记间距缩小显著提升了平移与旋转误差的控制能力,尤其适用于需要微米级调整的场景。

进一步突破开发片间对准(ISA)技术,通过分光镜将光学系统伸入两硅片间隙,同步观测上下层标记并融合图像,直接调整相对位置。该技术逻辑简单、观测直观,且面对面标记设计大幅降低间隙影响,早期精度达±2μm,近年随精密光学与机械控制技术升级(如真空环境辅助、压膜阻尼优化),已实现深亚微米级精度,成为高精度键合的首选方案。

对准标记的设计是精度优化的关键,通常采用游标式与十字形结合结构:游标设计细化平移误差判断,长间距并列标记则通过增大基线距离抑制旋转误差。材料层面,低粗糙度双面抛光晶圆(表面粗糙度Ra<0.5nm)与高透光率薄膜(如SiO₂/Si₃N₄优化层)可减少光散射,提升标记成像清晰度;工艺上,动态闭环控制算法(如实时误差反馈)与AI图像识别技术(如深度学习标记定位)的集成,进一步降低了人为干预需求,提高了生产效率。

目前,SmartView NT系统通过多光谱融合与亚像素级图像处理,将对准精度提升至0.1μm以下;Suss的ISA技术结合真空环境与低振动平台,有效抑制了接触过程中的漂移现象;同时,新型纳米级对准标记(如200nm线宽图形)与超薄晶圆(厚度<50μm)的应用,正推动光学对准向更微小尺寸TSV与更高密度3D集成方向发展,为先进封装技术的持续演进提供关键支撑。

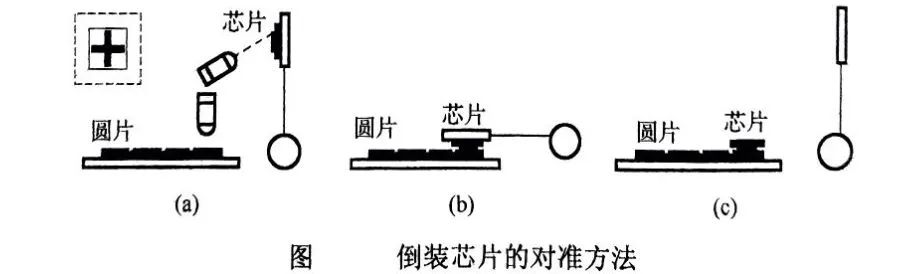

倒装芯片

倒装芯片技术作为三维集成电路中实现芯片级互连的核心手段,凭借其直接金属凸点键合与高密度集成优势,已成为D2D(芯片到芯片)与D2W(芯片到晶圆)对准的关键工艺。

其基本流程为:下层芯片固定于高精度工作台,上层芯片通过机械臂吸附并调整姿态,光学成像系统同步捕捉上下层对准标记(如十字形或游标式图形),通过亚微米级运动平台调整位置,随后施加可控压力(利用杠杆原理加载重物)并加热实现金属凸点熔融键合。传统设备的对准精度受限于机械调整速度与热压工艺稳定性,通常在1-20μm范围内,且精度与生产效率呈负相关——更高精度需延长对准时间,导致单点键合周期增加。

早期倒装芯片设备以封装应用为主,强调生产效率而非极致精度,其集成化设计(对准与键合模块一体)虽简化流程,但在三维集成中暴露出局限性:串行操作模式导致多层键合效率低下,且多次热循环易引发热应力累积,影响器件可靠性。此外,传统摆臂式结构在D2D对准中难以兼顾大范围调整与微米级精度,限制了其在高密度3D IC中的应用。

材料与工艺层面,新型低熔点金属合金(如Sn-Ag-Cu无铅焊料)与纳米级凸点(直径<10μm)的应用,进一步降低了键合温度与压力需求;而AI驱动的图像识别系统(如深度学习对准标记定位)与数字孪生技术,则通过实时误差预测与补偿,减少了人工干预,提升了良率。行业数据显示,采用高精度倒装芯片设备的3D IC产线,其TSV密度已突破105/cm²,互连电阻降低30%以上,为先进封装(如CoWoS、HBM)的持续演进提供了关键支撑。

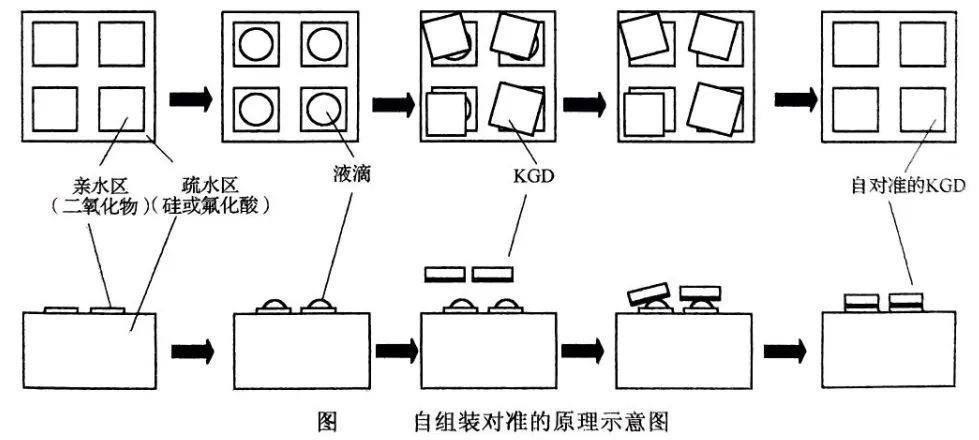

芯片自组装对准

芯片自组装对准技术作为三维集成电路制造中的创新方案,凭借其独特的流体动力学机制与高效率特性,正在小尺寸器件集成领域展现显著优势。

该技术核心原理在于利用液体表面张力驱动的物理特性实现精准定位:通过在基底表面构建亲水与疏水区域的差异(如SiO₂沉积结合光刻刻蚀工艺),配合低熔点焊料、环氧树脂或丙烯酸酯等流体介质,使液滴仅停留在预设亲水区,随后将待对准芯片放置于液滴表面,借助表面张力的自动调整功能完成位置与角度的校正。

自组装技术的突出优势在于其超高速与高精度特性——单芯片对准可在0.06秒内完成,精度达±1μm级,且支持并行处理模式,百颗芯片同步对准的时间与单颗芯片无显著差异,极大提升了生产效率。相较于传统倒装芯片技术,其非接触式调整机制避免了机械磨损,同时流体介质的缓冲作用降低了热应力风险,有利于提升垂直互连密度与器件可靠性。然而,该技术也存在局限性:需对芯片表面进行亲水处理(如涂覆特定材料),增加了工艺复杂度;液体环境可能对含MEMS悬空结构或传感器的芯片造成粘连风险;多层堆叠时,已键合层表面的亲疏水区域二次处理难度较高;正方形芯片还需初始方向预对准以避免旋转偏差。

模版对准

模板对准技术作为三维集成电路制造中的创新物理结构对准方案,由美国伦斯勒理工学院与清华大学联合开发,凭借其高效率、强适应性及工艺简化优势,在D2W(芯片到晶圆)键合领域展现出独特价值。该技术核心在于通过底层晶圆深槽与上层芯片垂直台阶的机械接触实现精确定位,规避了传统光学对准对复杂成像系统的依赖,同时支持键合设备内原位对准,有效避免了转移过程中的位置偏移风险。

其工艺流程分为三步:首先在底层晶圆表面旋涂低应力苯并环丁烯(BCB)有机聚合物,通过等离子体干法刻蚀构建各向异性深槽结构,顶角与侧壁精确定义芯片的x/y方向坐标。此步骤需优化刻蚀参数(如功率、压强、气体成分比),以最小化横向刻蚀导致的定位偏差,确保深槽底部清洁无残留;第二步在上层芯片边缘刻蚀垂直台阶,采用干法刻蚀替代传统砂轮切割以提升侧壁平整度(表面粗糙度Ra<10nm),台阶高度需略大于深槽深度以避免悬空接触;最后通过倒装设备将芯片翻转装载至深槽内,借助离心力(高速旋转晶圆)使台阶侧壁与深槽侧壁紧密贴合,完成亚微米级对准。

该技术优势显著:物理接触式定位不受光学系统分辨率限制,可在键合腔体内直接完成对准-键合流程,支持D2D、D2W及W2W多种键合模式,并兼容MEMS与传感器器件(避免液体环境导致的结构粘连)。然而,其局限性在于需对芯片衬底进行刻蚀,牺牲部分面积提升成本,且多层堆叠时上层深槽的参照标记易受下层工艺影响,导致对准精度逐层衰减(通常3层以上精度下降超30%)。

我要赚赏金

我要赚赏金