本文主要讲述半导体与CMOS工艺。

概述

天然沙子里富含二氧化硅(SiO₂),人们能够从沙子中提取高纯度单晶硅,以此制造集成电路。单晶硅对纯度要求极高,需达到99.9999999%(即9个9)以上,且硅原子需按照金刚石结构排列形成晶核。当晶核的晶面取向一致时,就能形成单晶硅;若晶面取向不同,则会形成多晶硅(Polysilicon)。

单晶硅与多晶硅均能用于集成电路制造,其中单晶硅主要用于构建硅衬底,多晶硅则可用来制作MOS管的栅极、多晶硅电阻或是电容等元器件。

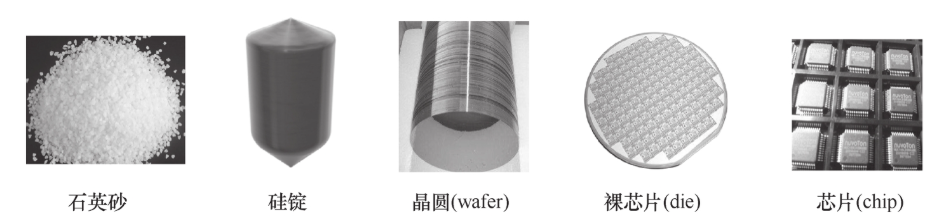

如图1所示,从沙子到芯片的制作流程如下:首先以石英砂为原料制备单晶硅——石英砂的二氧化硅含量高于普通沙子,经过提炼处理后可得到冶金级硅;接着对冶金级硅进行提纯、精炼与沉积,就能生成多晶硅;再通过拉制工艺,多晶硅可转化为单晶硅锭。将单晶硅锭切割成薄片,即可得到晶圆(wafer);每片晶圆上都能制作出大量集成电路裸芯片(die),这些裸芯片经过切片、测试与封装后,最终可制成集成电路芯片(chip)产品。

本征半导体

本征半导体指的是不含杂质原子且无结构缺陷的纯净晶体。锗(Ge)与硅(Si)均为4价元素,是常用的半导体材料。在本征半导体中,原子最外层的4个价电子虽能与周围原子的最外层电子形成共价键,但在热能或光能的激发作用下,部分共价键中的电子可能会脱离共价键束缚,进而形成导带电子与价带空穴,这两种粒子被统称为载流子。由于本征半导体中的两种载流子始终成对出现,且处于热平衡状态,在外加电场作用下,这些载流子可定向移动形成电流,使材料具备一定导电性,因此这类半导体被称为本征半导体。

若向本征半导体中掺入一定量的特定杂质原子,它就会转变为非本征半导体。其中,掺入5价元素的非本征半导体被称作N型半导体,这类5价元素被称为施主杂质;而掺入3价元素的非本征半导体则被称为P型半导体,这类3价元素相应地被称作受主杂质。与本征半导体的热平衡状态不同,非本征半导体中的两种载流子始终处于非平衡状态:占主导地位的载流子被称为多数载流子(简称多子),占次要地位的载流子被称为少数载流子(简称少子)。由于N型半导体掺入了5价元素,其多子为自由电子;而P型半导体掺入了3价元素,其多子为空穴。

在本征半导体内部,处于热平衡状态下的两种载流子(导带电子与价带空穴),其浓度保持一致,这一浓度被称为本征载流子浓度。该浓度并非恒定值,而是取决于半导体的具体材质与所处温度——温度越高,本征载流子的浓度会随之明显升高。

而在非本征半导体中,多数载流子(多子)的浓度大致与杂质的掺杂浓度相当,通常比本征载流子浓度高出数个数量级;少数载流子(少子)的浓度则普遍低于本征载流子浓度,二者同样存在数个数量级的差距。因此,相较于多子浓度,少子浓度极低,在多数计算与分析场景中可忽略不计。

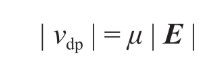

载流子在电场力驱动下会产生定向的漂移运动。在弱电场环境中,载流子的平均漂移速度 v 与电场强度 E 之间满足正比关系,数学表达式为

(式中,比例系数 μ 称作载流子的迁移率,其单位为厘米每伏秒,即 cm/(V・s))。

载流子的这种漂移运动可形成漂移电流,并且漂移电流的大小与载流子迁移率存在正相关关系。需要注意的是,虽然在电场力的作用下,空穴与自由电子的实际漂移方向相反,但它们各自形成的漂移电流方向却完全相同,所以半导体内部的总漂移电流,等于空穴漂移电流与自由电子漂移电流的叠加结果。

当外加电场强度相同时,半导体的漂移电流密度越大,说明其导电能力越强。进一步分析可知,漂移电流密度不仅与载流子的迁移率成正比,还与载流子的浓度成正比。虽然本征半导体的载流子浓度不为零,在电场作用下也能产生微弱的漂移电流,但非本征半导体的多子浓度通常比本征载流子浓度高出多个数量级,这使得非本征半导体的漂移电流密度远大于本征半导体。因此,在进行漂移电流计算时,本征半导体的漂移电流密度通常可忽略不计。

P型与N型半导体

由于本征半导体的漂移电流密度极小,相较于非本征半导体,本征半导体通常可看作绝缘体。也正因为如此,实际制造集成电路时,所采用的半导体材料均为非本征半导体。非本征半导体的导电能力与多子的迁移率 μ 密切相关:迁移率越大,半导体的导电能力越强,基于该半导体制作的器件工作速度也越快。

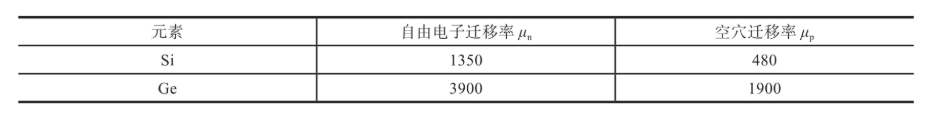

锗(Ge)与硅(Si)的载流子迁移率数据如表 2 所示(表中,自由电子迁移率记为 μₙ,空穴迁移率记为 μₚ)。无论是 Ge 还是 Si,其自由电子迁移率 μₙ都远大于空穴迁移率 μₚ,因此在增益、频率特性及驱动能力等关键性能指标上,N 型半导体器件的表现要显著优于 P 型半导体器件。

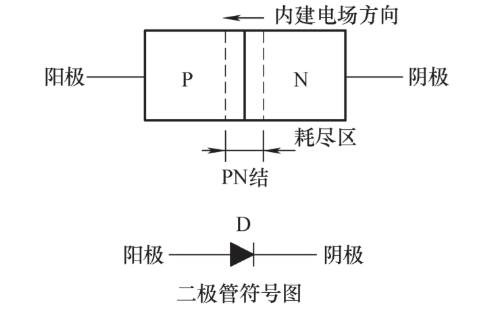

如图2所示,当N型半导体与P型半导体实现紧密接触时,二者交界面处会形成PN结。在交界区域内,N区中的自由电子会向P区扩散,同时P区中的空穴会向N区扩散。这种扩散运动发生后,交界面处会形成一个由N区指向P区的内电场;随着内电场强度逐渐增大,最终扩散力与内电场力达到平衡状态,扩散运动随之停止。此时,交界面处会形成一个不存在自由电子与空穴的区域,该区域被称为空间电荷区,也常称作耗尽区。若在PN结的两端分别引出电极,即可构成二极管——从P区引出的电极为阳极,从N区引出的电极为阴极。

给二极管两端施加电压,能够打破扩散力与电场力原本的平衡状态。若施加的电压满足阴极电位高于阳极电位,外加电压会增强内电场力,导致载流子仍无法开展扩散运动——由于不存在扩散电流,二极管呈现截止状态。反之,外加电压会削弱内电场力,载流子重新开始扩散,二极管内部产生扩散电流,此时二极管进入导通状态。这种随外加电压变化而切换导通或截止的特性,使二极管具备单向导电性,进而在电路中发挥关键作用。在CMOS工艺中,会形成多种类型的PN结,这些PN结不仅可用于制造集成电路中的二极管,处于反偏状态的二极管还能实现器件之间的电气隔离。

将5价或3价元素引入半导体的过程称为掺杂,掺杂工艺常用的是离子注入(ion implantation)法。当离子注入浓度较低时,为轻掺杂(用N⁻、n⁻或P⁻、p⁻表示);当离子注入浓度较高时,则为重掺杂(用N⁺、n⁺或P⁺、p⁺表示)。显然,重掺杂半导体的导电性能优于轻掺杂半导体。

在大面积的轻掺杂区域内进行局部重掺杂处理时,轻掺杂区域一般称作衬底,重掺杂区域则称为扩散区(diffusion)或有源区(active)。扩散区与衬底的半导体类型既可以相同(同为N型或同为P型),也可以不同(异型)。在CMOS工艺里,同型掺杂与异型掺杂两种情况均会存在:其中,同型掺杂主要用于通过欧姆接触引出电极并实现连接,异型掺杂则主要用于构建MOS器件与衬底之间的隔离结构,下文将分别对这两种掺杂的应用展开说明。

半导体器件需通过金属引出电极。当半导体与金属接触时,重掺杂可让电子借助隧道效应穿过接触势垒,从而形成低电阻值的欧姆接触,因此能用于引出电极;但轻掺杂情况下,半导体与金属的接触电阻极大,电极连接效果不佳,无法用于引出电极。所以,要从低掺杂的衬底引出电极,需先对衬底局部进行同型重掺杂处理,之后再引出金属电极。

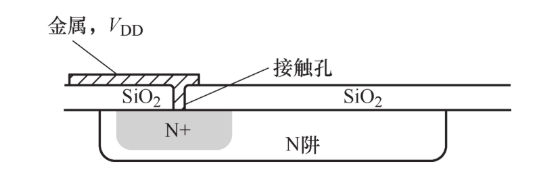

如图3所示为N阱与金属通过欧姆接触连接的剖面结构。N阱属于轻掺杂的N型半导体,常被用作衬底,并且需要连接至电源VDD。为实现有效连接,需在N阱内进行同型重掺杂,形成N⁺扩散区,从而与金属构建欧姆接触。需要说明的是,图3中的二氧化硅(SiO₂)用于实现金属与半导体之间的绝缘隔离,为使金属与N⁺扩散区形成欧姆接触,需在SiO₂层上开设孔洞,该孔洞被称为接触孔。

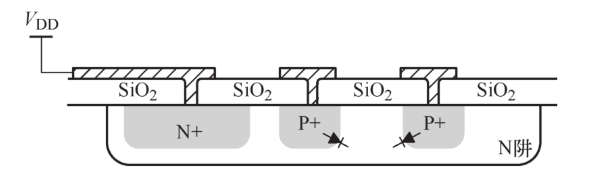

由于异型离子注入能在扩散区与衬底之间形成PN结二极管,因此,只需合理控制偏压,使二极管始终处于反偏状态,就能让同一衬底上的多个扩散区通过二极管实现相互隔离。如图4所示为两个P⁺扩散区的二极管隔离剖面结构:N阱内部的两个P⁺扩散区分别与N阱构成两个独立的二极管,且N阱通过N⁺扩散区连接至最高电位VDD,如此便能确保两个二极管始终处于反偏状态,进而实现两个P⁺扩散区之间的二极管隔离。

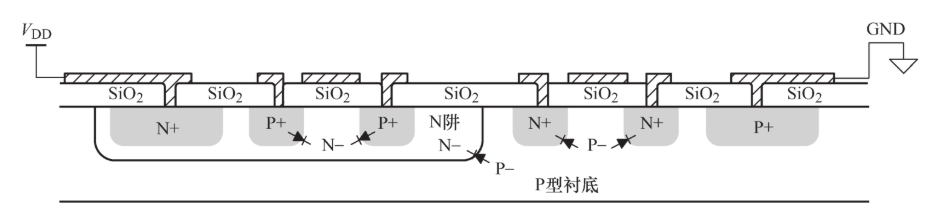

同理,若将P型衬底连接至最低电位GND,即可实现多个N⁺扩散区之间的二极管隔离。如图5所示为N阱工艺的二极管隔离剖面结构,图中同时展示了两个P⁺扩散区之间以及两个N⁺扩散区之间的二极管隔离结构。图中整个晶圆的基底为P型衬底,N阱制作于P型衬底之上。结合图5中的电位关系可看出,N阱与P型衬底之间的PN结二极管同样处于反偏状态,从而保证了N阱与P型衬底之间的隔离。这种仅包含N阱、不设置P阱的工艺,被称为N阱工艺。

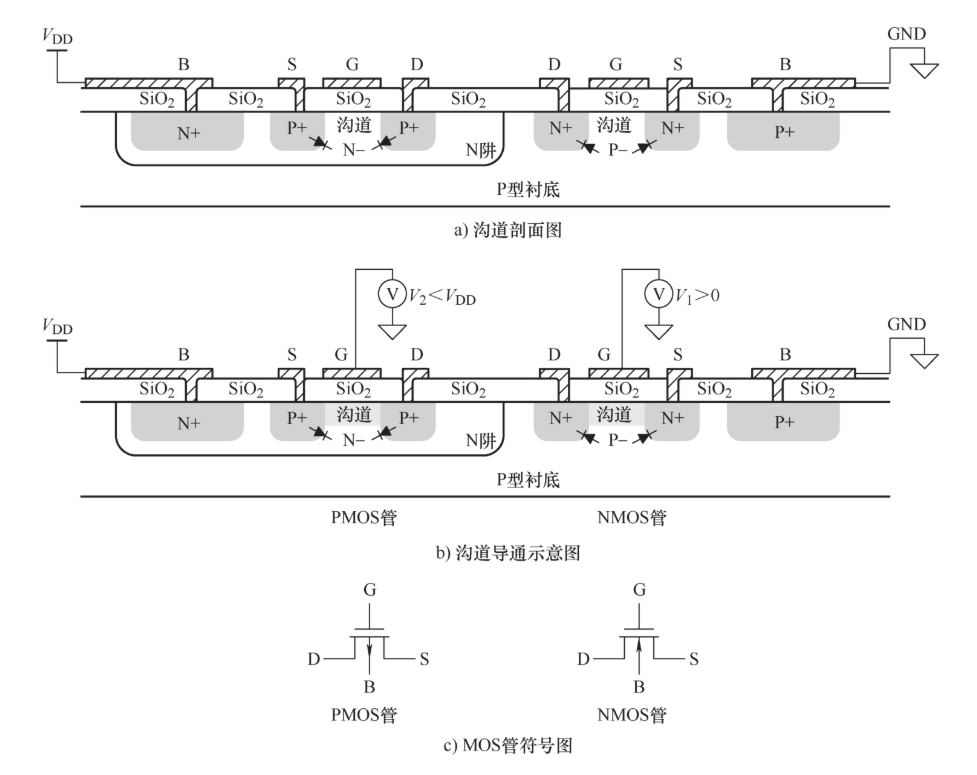

如图6a所示,若在N阱中注入两个P+扩散区,或在P型衬底中注入两个N+扩散区,那么两个扩散区之间的区域被定义为沟道,且沟道与所在衬底是一个整体。衬底用字母B指代,沟道两侧的扩散区用S和D表示,二者通过接触孔与金属相连。在沟道的正上方制作金属电极,该电极用字母G表示。结合图6中施加的电压关系可知,N阱与P型衬底之间的PN结二极管处于反偏状态,沟道两侧的扩散区与各自衬底之间同样处于反偏状态,因此图中所有S与D之间均不导通。需要说明的是,图中存在两组相互独立的S、D、G和B,此处使用相同字母,仅为方便后续对MOS管引脚进行命名。

在图6b中,两个N+扩散区之间的沟道属于P型衬底,且该衬底已连接至GND。此时,若向沟道上方的G施加一个正电压V₁,G与沟道之间产生的电场会吸引部分电子,这些电子会填充沟道内的空穴。若V₁足够高,电子填满空穴后仍有剩余,沟道就会从P型转变为N型,进而连通两个N+扩散区,使S与D导通。当V₁的电压降至0后,沟道会恢复为P型,再次将S与D隔离。因此,S与D相当于电子开关的两端,其接通与断开由G的电压控制。

同理,图6b中N阱内两个P+扩散区之间的沟道即为N阱,且N阱已连接至VDD。此时,向该沟道上方的G施加一个低于VDD的电压V₂,G与沟道之间的电场会排斥沟道内的电子。当V₂足够低时,不仅自由电子被排斥出沟道,部分共价键中的电子也会被排斥,进而在沟道内形成空穴。如此一来,沟道会从N型转变为P型,从而连通两个P+扩散区,使S与D导通。当V₂的电压重新升高至VDD后,沟道会恢复为N型,再次将S与D隔离,因此该结构同样是一个由G控制的电子开关。

CMOS

沟道两侧的扩散区分别称为源极(Source,简称S)和漏极(Drain,简称D),沟道上方的电极板称为栅极(Gate,简称G),这三者与衬底背栅(Backgate,简称B)共同构成MOS管。其中,两个N+扩散区与其对应的栅极构成的器件称为NMOS管,两个P+扩散区与其对应的栅极构成的器件称为PMOS管,二者的符号如图6c所示。

早期MOS管的栅极材料为铝,属于金属(Metal)范畴;栅极与沟道之间的二氧化硅属于氧化物(Oxide);沟道则属于半导体(Semiconductor)。将Metal-Oxide-Semiconductor三个英文单词的首字母组合,便得到MOS(即金属-氧化物-半导体),MOS管也由此得名。需要指出的是,在实际工艺中,栅极下方的二氧化硅层厚度需小于其他区域的二氧化硅层厚度。

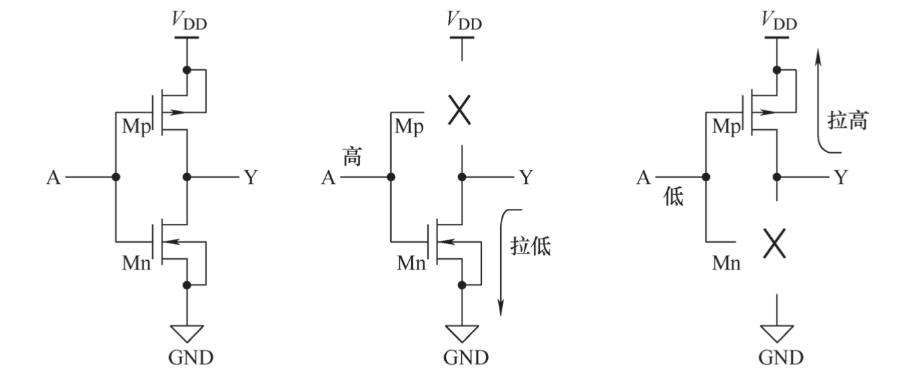

MOS管可简单理解为受栅极电压控制的电子开关:NMOS管在栅极电压为高电平时导通,PMOS管则在栅极电压为低电平时导通。如图7所示,将PMOS管与NMOS管在VDD和GND之间串联,将两个栅极连接在一起作为输入端口A,同时将两个MOS管的漏极连接在一起作为输出端口Y。当A为高电平时,NMOS管导通、PMOS管截止,输出端Y被拉低;当A为低电平时,NMOS管截止、PMOS管导通,输出端Y被拉高。由此,A与Y形成反相关系,该电路也因此被称为反相器。

在图7所示的反相器中,由于PMOS管与NMOS管的栅极相连,且二者导通所需的栅极电压相反,因此NMOS管与PMOS管不会同时导通,电源与地之间无电流通路,相当于不存在静态功耗。除反相器外,通过NMOS管与PMOS管的相互配合,还可构成其他各类逻辑门,这些逻辑门在静态工作状态下同样无直流功耗。由于NMOS管与PMOS管的互补特性极为完善,人们将由二者构成的电路命名为互补金属-氧化物-半导体(Complementary Metal-Oxide-Semiconductor,简称CMOS)。

尽管CMOS逻辑门在静态时,电源与地之间无直流通路(即无静态功耗),但在逻辑门状态翻转过程中,NMOS管与PMOS管会出现短暂的同时导通现象,这会产生一定的动态功耗。此外,逻辑门对负载电容进行充放电的过程也会产生功耗。由于这些功耗均与逻辑门的翻转相关,因此时钟频率越高,CMOS电路的功耗越大;而现代大规模集成电路的时钟频率普遍较高,因此解决功耗与散热问题仍是CMOS集成电路设计中的难点。

随着CMOS工艺依据摩尔定律持续发展,栅极与沟道之间的二氧化硅层厚度不断减小,栅极漏电现象愈发严重。这一问题在深亚微米工艺阶段之前尚不明显,但进入几十纳米工艺节点后,栅极漏电功耗已成为电路总功耗的主要来源。在深亚微米工艺阶段之前,只需关断时钟(clock gating),即可等效于关断电路;但深亚微米工艺之后,情况发生变化——除关断时钟外,还需降低电源电压或抬高衬底电压,才能最大限度降低栅极漏电功耗。随着集成电路规模的不断扩大,功耗与散热已成为设计瓶颈。只有通过更多技术创新,才能确保摩尔定律持续推进,进一步提升芯片的集成度。

我要赚赏金

我要赚赏金