大功率 PCB 设计不仅仅是管理电压和电流,更是管理它们的乘积:功率,而功率最终绝大多数会转化为热量。同时,高功率开关电路还会产生强烈的电磁场。本文将探讨功率设计中的场效应、热生成和材料选择。

1. 高功率场效应

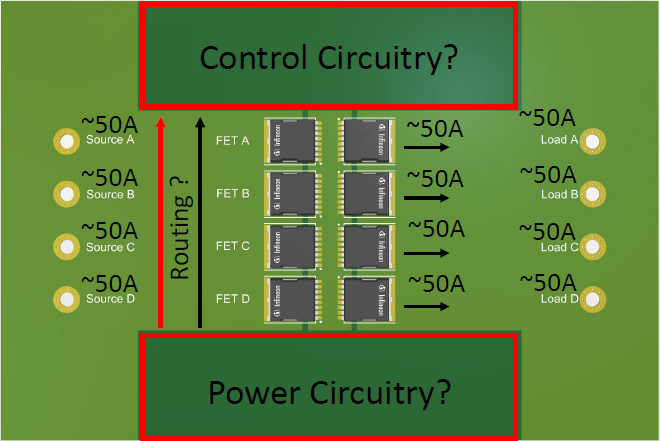

高功率路径(特别是高di/dt,即电流变化率高的路径)会产生强大的电磁场。这些场会耦合到附近的敏感电路上,如控制电路、门极驱动(Gate Drive)信号和温度检测电路。在理想情况下,高功率路径应与其返回路径紧密耦合(例如在相邻层上反向布线),以使其产生的场相互抵消。

大功率 PCB 设计需要考虑的一些通用问题,包括:

大功率路径附近是否有敏感电路?

在您的设计中,大功率路径是否与其回流路径紧密耦合?

某些系统可能存在机械结构限制,导致无法(使路径)紧密耦合。

电池的端子(或:接线柱)通常相距很远,且两者之间几乎没有空间允许紧密耦合。在这种情况下,请确保您有策略来保护信号免受大功率能量的干扰。

在大功率路径下方走信号线或电源线,会使它们面临极大的风险,容易受到来自大功率路径瞬态能量的干扰。对于栅极驱动信号或温度测量电路而言,这种情况是不可避免的。在这种情况下,应保持信号(与其回流路径)紧密耦合,并在层叠设计中使其尽可能远离大功率(路径)。

信号完整性 (SI) 和电源完整性 (PI) 的设计准则同样适用于大功率设计

随着功率/能量等级的增加,(不良)设计所导致后果的严重程度也会随之增加。

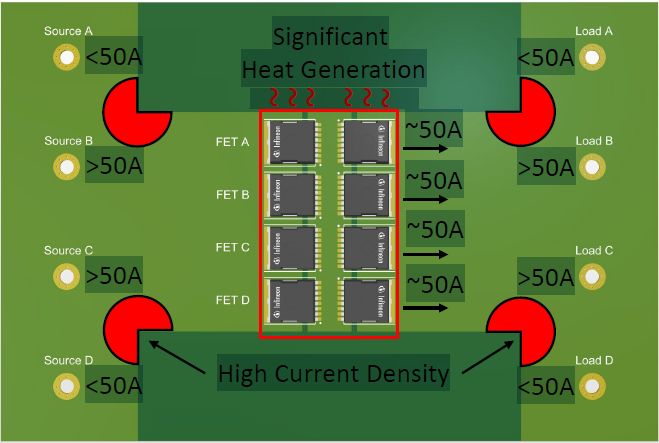

2. 热量生成与管理

设计中最大的敌人是热量。您必须准确识别热源:

高电流密度区域:电流“拐角”和导体瓶颈处。

大功率元件:如 FET、二极管和电阻器。

您必须了解设计的热限制:

材料玻璃化转变温度 (Tg)

元件最高温度:所有元件(包括无源元件)的最高工作温度。

冷却方式:设计是依赖自然对流(被动冷却)还是风扇(主动冷却)?

还需要注意的一些事项:

您或许能够手算出一些发热量的值,但许多情况仍需要通过IR(红外)/CFD(计算流体力学)类型的仿真来确定温升。

局部的发热区域会给 PCB层叠结构带来应力。

X/Y 轴(平面)的膨胀会受到玻璃纤维布(Glass Weave)的约束。

Z 轴(垂直方向)将承受更大的热膨胀。

在热循环过程中,电镀通孔(Plated Through Holes, PTH) 会产生疲劳,如果 Z 轴膨胀不受控制,(这些通孔)可能会失效。

3. 热机械应力与材料 (Tg)

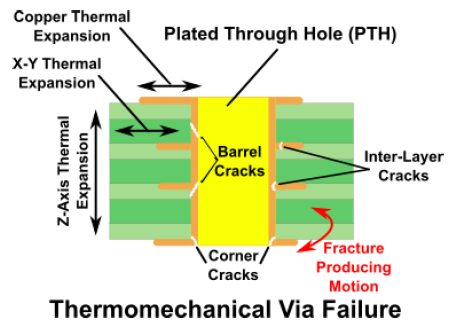

当 PCB 受热时,它会膨胀。这对可靠性有着致命的影响。

Z 轴膨胀 (Z-Axis Expansion):PCB在X-Y平面(水平方向)由于有玻璃纤维布的束缚,膨胀系数(CTE)较低。但在Z轴(垂直方向),CTE要高得多。

过孔疲劳:当 Z 轴在热循环中反复膨胀和收缩时,会对镀通孔(PTH)的桶壁施加巨大的应力。这会导致桶壁裂纹 (Barrel Cracks)或拐角裂纹 (Corner Cracks),最终导致过孔开路。

解决方案:选择正确的材料

玻璃化转变温度 (Tg)是 PCB 基材从坚硬的玻璃态转变为柔软的橡胶态的温度。

设计规则:必须选择Tg 高于设计最高工作温度的材料。当 PCB 接近其 Tg 时,它会软化,Z 轴膨胀会急剧增加,极易导致分层和过孔失效。

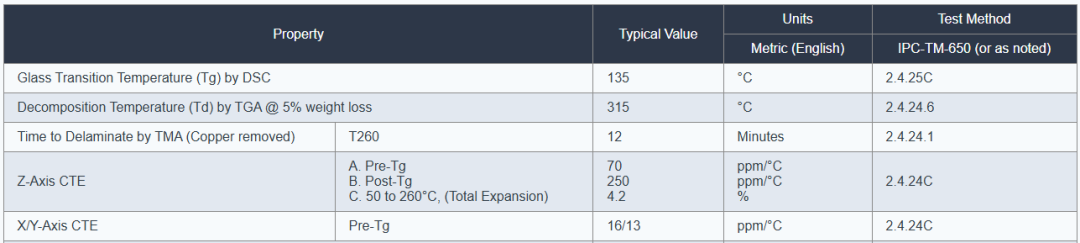

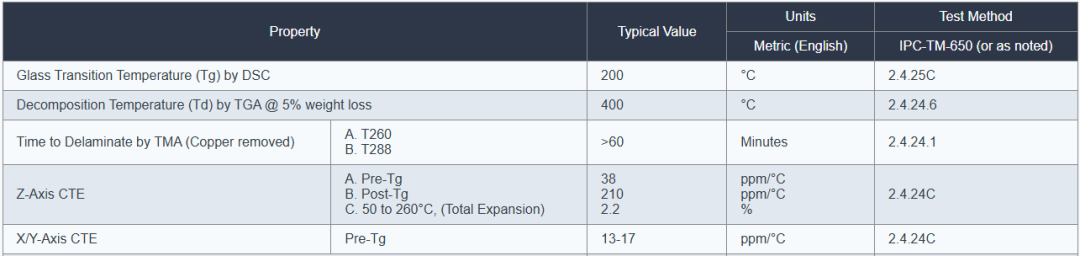

材料对比 :

不良选择 (如标准FR-4):

Tg: 135°C

Z轴CTE (Tg前): 70 ppm/°C

总膨胀 (50-260°C):4.2%

更优选择 (如高Tg材料):

Tg:200°C

Z轴CTE (Tg前):38 ppm/°C

总膨胀 (50-260°C):2.2%

选择低Z轴膨胀和高Tg的材料,是确保高功率PCB在热循环下保持长期可靠性的关键。

4. 层叠(Stack-up) 的挑战

在高功率设计中,我们希望使用厚铜(如多层2oz)来承载电流。然而,这给需要控制阻抗的信号(如差分对)带来了巨大挑战。

阻抗由走线宽度、介电常数(Dk)和介质厚度(走线到参考平面的距离)决定。

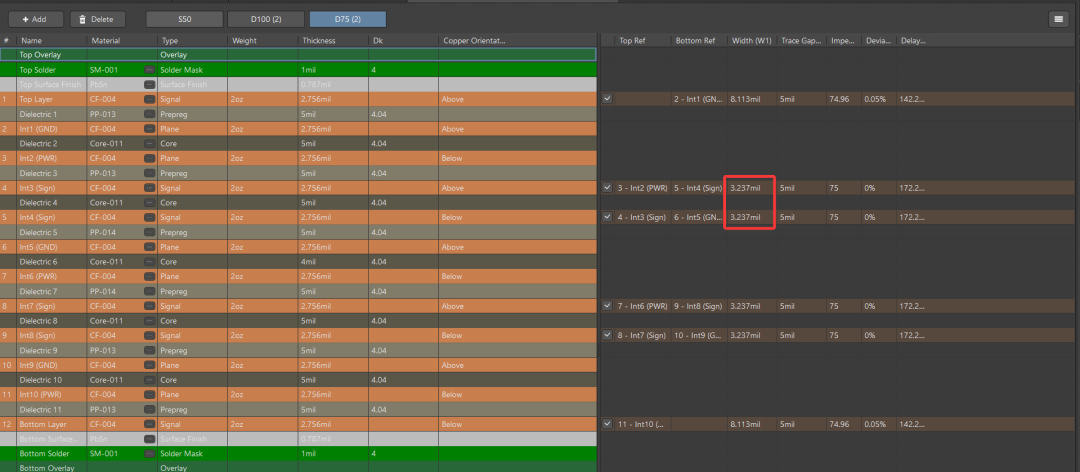

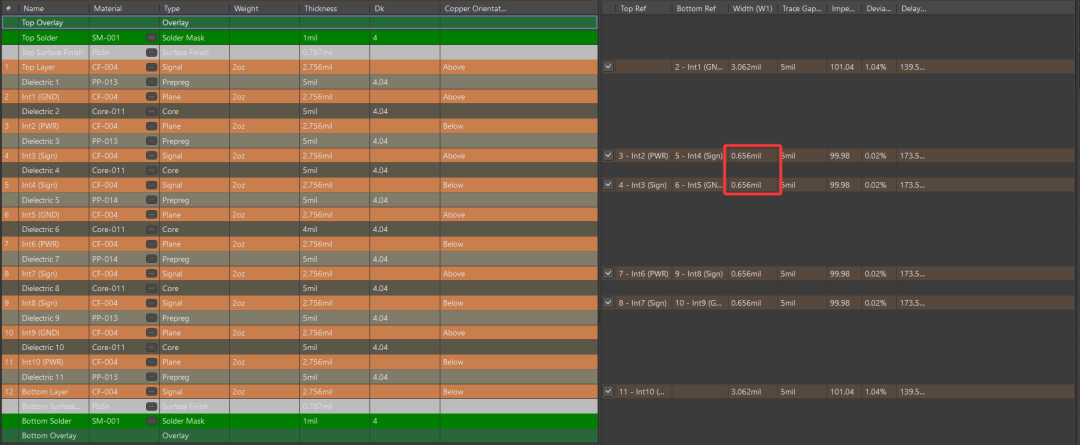

问题1:如果使用厚铜(2oz)和薄介质(例如5mil)

假设在内层为了实现差分对 75Ω 或 100Ω 阻抗,计算出的走线宽度会非常细。分别为 3.237 mil 及 0.656mil。单端的更是无法实现。

这种宽度在 2oz 铜上是无法制造的。

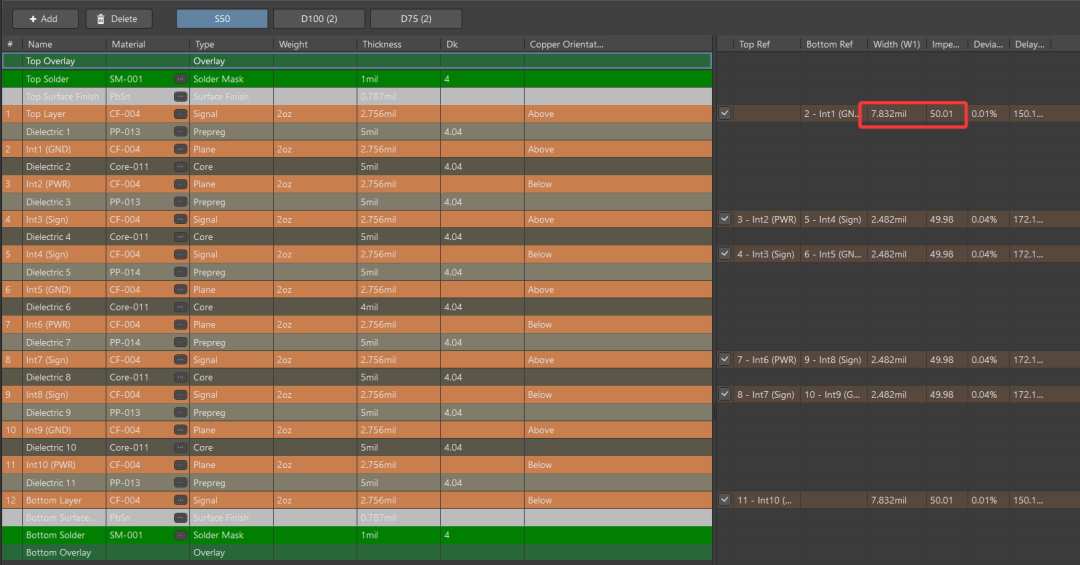

如果需要在外层(顶层或底层)实现 50Ω 阻抗,线宽需要 7.832 mil。这对于那些 pitch 比较下的器件而言又太宽了!

问题2:如果为了解决可制造性问题(线宽太小),可以加厚介质(例如 8 mil)或者增加差分对的间隙。

比如,对于 100Ω 阻抗的差分对而言,将间隙调整为 15mil,走线宽度则可调整为 4.413 mil。但 15mil 的差分对间隙对信号完整性而言并不是一个合理的值

增加介质厚度是一个方案。但是,这会显著增加PCB的总厚度(例如从0.089"增加到0.110")。

连锁反应:板厚的增加会恶化钻孔的纵横比(Aspect Ratio)。

8mil 成孔(最终孔径),纵横比 0.110” / 0.008” =13.75

10mil 成孔(最终孔径),纵横比 0.110” / 0.010” =11

12mil 成孔(最终孔径),纵横比 0.110” / 0.012” =9.17

高纵横比的孔非常难以电镀均匀,增加了过孔失效的风险。

结论:大功率PCB的叠层设计充满了权衡。您必须在载流能力(厚铜)、信号完整性(阻抗控制)、可制造性(走线宽度)和可靠性(钻孔纵横比)之间找到一个可接受的平衡点。

我要赚赏金

我要赚赏金