一、概述

氮化镓(GaN)作为一种第三代宽禁带半导体材料,凭借其高电子迁移率和高击穿电场等优异特性,已在5G通信基站、数据中心电源及消费电子快充等领域实现规模化应用。在电动汽车领域,GaN器件依托其高频与高效率优势,正逐步应用于车载充电器(OBC)、DC-DC转换器等关键系统中。

然而,GaN芯片的高性能实现离不开先进封装技术的支撑,这对封装提出了更高要求,如高效散热能力、低寄生电感、良好的电气隔离及机械应力管理等。目前主流的GaN封装技术包括倒装芯片封装、铜柱键合、多芯片集成封装和嵌入式封装等,这些技术能有效减少寄生电感、提高散热性能,从而确保GaN芯片在高频、高功率工况下的稳定性和效率。

研究GaN芯片封装技术具有重要意义。一方面,它可以提升功率转换效率,推动5G通信、无线充电及新能源汽车等领域的技术进步;另一方面,通过优化散热设计、提高器件可靠性,有助于延长芯片使用寿命。此外,借助先进封装技术降低系统复杂度与成本、提高集成度,可实现更高的系统性能,进而推动高频、高功率密度应用的普及,带动整个功率半导体产业链的升级。本文将从GaN芯片封装的基本原理出发,综述目前主流的分立与合封封装技术,并结合先进封装趋势,探讨其发展路径、关键技术挑战及未来市场需求。

二、GaN 材料特性

GaN 材料具有禁带宽度大(≈3.4 eV,是硅的3倍)、临界击穿电场强度高(≈3.3 MV/cm,是硅的10倍)、电子饱和漂移速度快(≈2.5×107 cm/s,是硅的2倍)等优异特性,在高频、高功率、高温等应用场景中表现出显著优势。GaN 在200 ℃结温下仍保持>80%的电子迁移率(传统硅基器件在150 ℃即失效);在高频响应上,载流子渡越时间缩短至皮秒级,支持Kα 波段(26.5~40 GHz)信号处理;单位面积导通电阻低至2 mΩ·cm2,允许芯片承受>1 000 V/μs 的电压斜率,使器件功率密度跃升。

与传统的硅和砷化镓相比,GaN 器件能够在更高的电压和毫米波频率下工作,同时具有更低的导通损耗和更高的功率密度,这些特性使得GaN 在微波通信、功率电子、军事雷达、5G 基站等领域具有广泛的应用前景。此外,先进的封装材料(如高性能导热界面材料和高温胶黏剂)也在GaN 芯片封装中发挥了重要作用,有效提升了散热性能和机械强度。

三、主要GaN 封装技术

分立器件

晶体管外形(TO)封装作为一种经典的分立器件封装形式,在功率半导体器件中应用广泛,能够为功率MOSFET、绝缘栅双极型晶体管(IGBT)以及GaN高电子迁移率晶体管(HEMT)等器件提供优良的电气性能和热性能。近年来,随着功率器件朝着高功率密度、高频率和高可靠性方向发展,TO封装的设计与优化已成为研究热点。例如,一种创新的晶体管外形无引线(TOLL)封装结构,如图所示。该封装通过缩短引线长度并优化引线框架设计,显著降低了封装电阻,提升了电流承载能力,并在汽车电子应用中表现出优越的性能。TOLL封装不仅有助于提高功率密度,还通过引入“侵入式模具边缘”专利技术,进一步增强了制造过程中的工艺可控性与结构稳定性。然而,TO封装在高温环境下的可靠性问题依然存在,特别是在因热机械应力引起的焊料疲劳方面,仍需通过材料与结构优化进一步改进。

TOLL 封装设计

对于GaN HEMT器件而言,TO封装中的热管理问题尤为突出。JORDA等人[7]在分析GaN HEMT采用TO-247封装时的自然对流散热方案时指出,该封装的热阻主要来源于内部导热路径,尤其是焊料层与基板之间的热传导效率。SONG等人进一步研究了TO封装中GaN HEMT的功率循环测试,发现焊料层因热疲劳成为器件失效的关键因素,特别是在高温循环条件下,热机械应力会导致焊料层热阻上升,从而影响器件的可靠性。

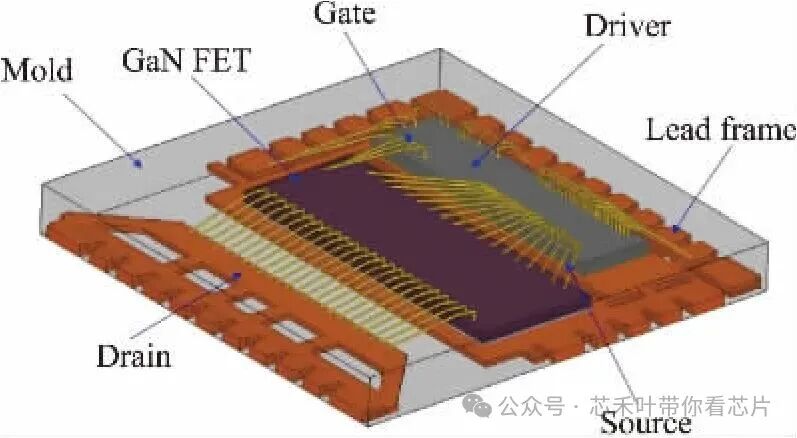

四边扁平无引线(QFN)封装因其低电感、高散热性能和紧凑的尺寸,逐渐成为GaN HEMT 器件封装的主流选择。QFN 封装通过其无引线设计,减少了寄生电感,特别适合高频和高功率应用。通过系统级协同设计,成功将600 V GaN FET 与集成驱动器封装在32 引脚QFN- 系统级封装(SiP)中,尺寸为8 mm×8 mm,展示了QFN 封装在高功率密度和高效率应用中的潜力,如图 所示。研究表明,通过优化封装和PCB 布局,可以显著降低寄生电感,从而提升器件的开关性能和可靠性。

采用8 mm×8 mm QFN-SiP 封装的器件

在QFN 封装中,热管理是一个重要的挑战。GaN HEMT 器件在高功率条件下工作时会产生大量热量,若不能有效散热,器件性能将下降甚至失效。QFN 封装通过暴露的散热焊盘能够有效传导热量,尤其是在高功率应用中,QFN封装的DSC 设计可以显著降低器件的热阻;通过使用铜柱(CuP)凸点技术和倒装芯片工艺,可以进一步优化QFN 封装的热性能,减少热阻并提高器件的可靠性

此外,QFN 及同类封装在射频器件中的应用也取得了显著进展。通过ANSYS 仿真和实验验证,展示了双边扁平无引线(DFN)封装在GaN 基射频器件中的优异散热性能。DFN封装通过优化引线键合和散热设计,能够有效降低器件的结温,从而提高其崩溃电压和开关稳定性。特别是在高频应用中,DFN 封装的低寄生电感和高散热性能使其成为GaN 射频器件的理想选择。

合封器件

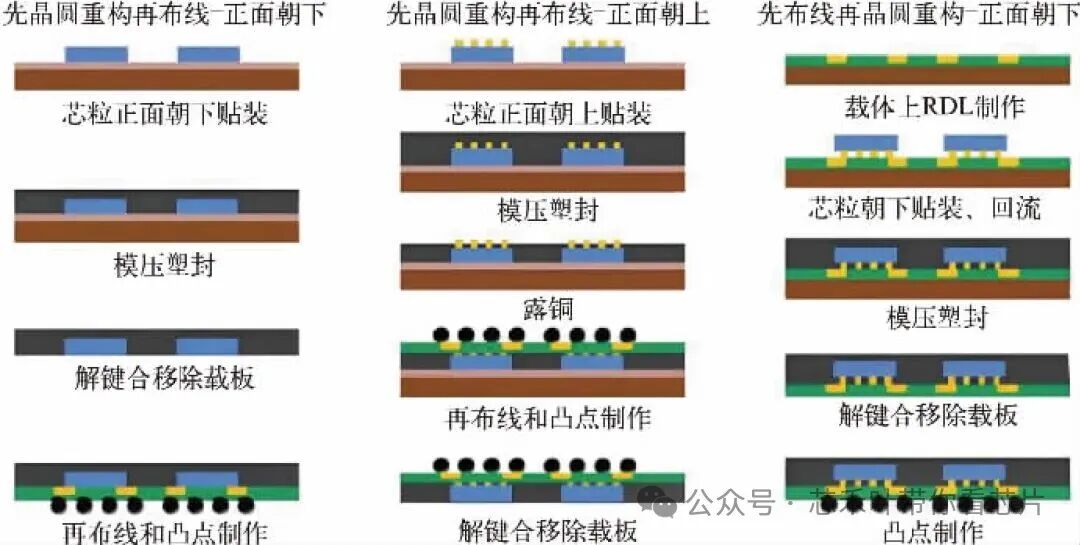

近年来,扇出型晶圆级封装(FOWLP)技术因其在异构集成和热管理方面的优势,逐渐成为GaN 器件封装的主流选择之一。其基本结构是将切割后的裸芯片重新排列在临时载板上,通过EMC 包封形成重构晶圆,在其表面利用光刻和电镀工艺制作多层重新布线层(RDL),扩展I/O 接口,并植入焊球实现无基板的高密度互连封装。FOWLP 工艺流程大致分为晶圆重构再布线和先布线再晶圆重构2 种,如图所示。

FOWLP 工艺流程

封装设计对器件热阻的影响非常显著。通过研磨GaN器件的硅衬底并采用银烧结技术将其背面连接到直接覆铜(DBC)基板上,结合顶部与背面冷却方式,可将器件的热阻从15 ℃/W降至4.5 ℃/W。这种改进主要得益于DBC基板的高热导率以及银烧结工艺优异的传热性能。此外,通过有限元仿真验证了DBC基板在热管理中的优势:其热阻显著低于传统印制电路板,尤其在高功率密度应用中表现出更好的散热能力。

通过多尺度热仿真分析了扇出型晶圆级封装中GaN功率放大器的热特性,发现多层PCB相比单层PCB在热管理上优势明显,可将最高结温降低25 ℃。通过将导通电阻Rds_on作为温度敏感参数,可以实现GaN器件的热阻测试:通过实验验证了Rds_on与结温之间的相关性,并提出了一种基于Rds_on的热阻测试方法,适用于不同电压等级和封装形式的GaN器件;通过在线S参数测量证实了GaN HEMT中Rds_on作为温度敏感参数的有效性,其温度依赖性与散射参数(如S11频移)相关,可实现动态结温反演,误差范围与内置传感器相当,且无需额外硬件;D电热联合仿真结果表明,SiC MOSFET的正温度系数特性可抑制并联模块的电流失衡,结合热阻差异建模后,电流不均衡度从2.61 A降至1.31 A,最大温差由10 ℃优化至4.67 ℃,间接反映了热阻分布特性。然而,该方法受器件参数分散性、热耦合效应及测量带宽等因素影响,需通过参数校准和三维热阻抗建模等协同设计提升其鲁棒性。综上,Rds_on的温度敏感性为热阻评估提供了理论依据,但其工程应用仍需兼顾器件特性和系统级优化。此外,通过瞬态热仿真研究了扇出型晶圆级封装中GaN器件的热响应时间,发现器件可在0.8秒内达到稳态温度,进一步验证了该封装在热管理方面的高效性。

多芯片模块封装技术广泛应用于功率电子器件,尤其是GaN功率器件。该技术基于层压有机基板、陶瓷基板或薄膜基板集成多种工艺裸片,通过引线键合或倒装焊与基板内多层布线实现互连,并采用金属、陶瓷或塑料外壳提供保护与散热功能。MCM封装通过将多个芯片集成在同一基板上,可有效降低寄生电感、提升热管理效率,并提高系统功率密度和可靠性。

通过研究MCM-LED封装的热管理,提出了基于热阻网络的热分析模型,并通过有限元仿真验证了其有效性。MCM-LED封装散热系统的原型结构如图所示。研究表明,该封装结构的总热阻为6.53 K/W,结温为77.2 ℃,仿真与理论计算结果基本一致。此外,通过正交实验优化了封装结构参数,发现焊球直径对热性能的影响最为显著。该研究为GaN器件的MCM封装提供了重要的热管理参考依据。

MCM-LED 封装散热系统的原型结构

FOWLP 和MCM 封装技术在GaN 器件封装中各具特色。FOWLP 将芯片嵌入封装体并利用RDL 实现电气连接,能够显著减小封装尺寸,提高集成密度,同时具备优异的热管理性能,尤其是在多层PCB 结构中,能够有效降低结温并实现快速热响应。MCM 封装则通过将多个芯片集成在同一基板上,减少寄生电感,提升热管理效率和系统功率密度,特别适用于高功率密度和多芯片协同工作的场景,如高功率LED 和DC-DC 转换器。总体而言,FOWLP 更适合高集成密度和快速热响应的应用,而MCM 则在高功率和多芯片集成领域表现更优,需根据应用需求进行选择。

我要赚赏金

我要赚赏金