1. 为何要做Target Board?

NiosII IDE提供了一个烧写flash的工具Flash Programmer(在Tools菜单下,如图1所示)。

图1 Nois II IDE中Tools菜单下Flash Programmer

但在使用Flash Programmer之前,必须指定当前project的Target Board(在SOPC Builder里System Content页中指定,如图2)。图2中,指定的Target Board为UP3_Board。Altera给自己开发版都提供了对应的Target Board,但是对于用户自己做的板子来说,Altera提供的Target Board一般都不适用。所以用户要根据自己的板子,制作一个自己板子专用的Target Board。

图2 在SOPC Builder中指定Target Board

2. Target Board是什么?

Altera的文档中是这么定义的:“the term “target board” refers to the set of files used by SOPC Builder to determine board characteristics on which the system is being implemented”。

就我理解,Target Board主要记录的是板子上各种flash芯片的信息(flash的容量等)。做一个Target Board就是做一个project用于烧写板子上的flash芯片。当使用IDE中的Flash Programmer烧写flash芯片的时候。IDE把这个Target Board的project下载到FPGA上,并使用对应的软件程序来烧写板上的flash芯片。

3. 如何制作Target Board?(以UP3为实例)

⑴ 打开Nios II SDK shell。Programs >Altera > Nios II Development Kit > Nios SDK

shell,如图3所示:

图3 打开Nios II SDK shell

⑵ 使用cd命令将当前目录改变到存放Target Board的project的目录下。这个目录放置在硬盘上的任何地方。如图4所示,这里将要把Target Board的project放在f:/up3这个目录下:

图4 改变当前目录

⑶ 执行mk_target_board命令来建立Target Board的project模板。mk_target_board命令的有以下一些参数:

--name=<name>:Target Board的名称;

--family=<family>:板子上的FPG的类型,有效值是“stratix”或者“cyclone”;

--clock=<freq>:Target Board的project中Nios II系统的时钟频率。这个频率必须大于等于50MHz。如果FPGA输入的时钟频率小于50MHz,那么必须在Nios II系统外加个PLL使得Nios II系统的时钟频率大于50MHz;

--index=<index>:FPGA芯片在JTAG链中的编号,如果JTAG口上就只连接一个FPGA芯片,那么值为1;

--epcs=<refdes>:如果板子上要使用EPCS串行配置器件来配置FPGA,并且打算通过Flash Programmer来对它进行烧写的话,才需要设置该参数。指定EPCS串行配置器件的标号,这个标号可任意设置,只要保证板子上其他flash芯片不使用这个标号即可;

--buffer_size=<size>:这个值取决于板子上FPGA芯片的型号,参照下表。

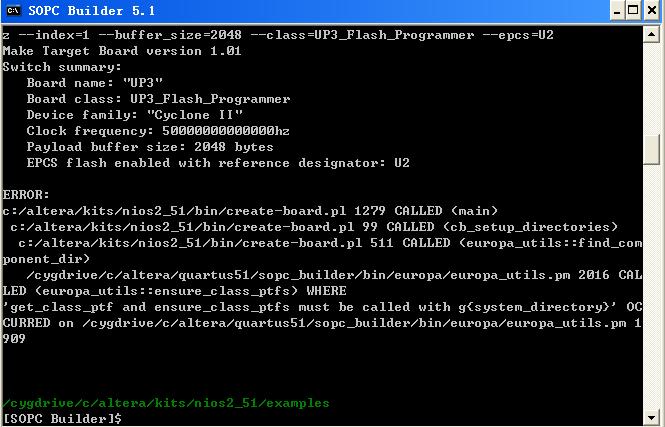

如图5,这里建立名称为UP3_Board的Target Board。mk_target_board命令执行后的提示会因为Nios II Development Kit的版本不同而有些区别。图5是Nios II Development Kit评估版5.0上执行后的结果。

图5 执行mk_target_board命令来建立Target Board的project模板

UP3板子上的FPGA芯片使EP

这个步骤完成后,可在所设置目录下看到UP3_Board文件夹,里面有执行mk_target_board命令所建立的Target Board的project模板。

⑷ 打开Target Board的project模板。可从Quartus II中打开,也可以直接双击.qpf文件。

⑸ 在Assignments > Device中设置板子上的FPGA的型号,然后点击OK。如图6;

图6 设置FPGA型号

⑹ 打开SOPC Builder(Tools菜单),选择System Contents页,如图7。Target Board为Unspecified Board,Clock为96.0MHz。这些都不需要进行改动;

⑺ 修改JTAG UART的设置。mk_target_board自动生成了Module Name为jtag_uart_0的部件,但是不同版本生成的该部件设置有些区别。双击该部件,若两个Constuct using registers instead of memory blocks的选项没有选定,那么必须选定。如果不这么修改的话,在后面编译的时候会出现memory block不够用的错误。修改后,如图8;

图8 修改JTAG UART设置

⑻ 修改Module Name为asmi部件的设置参数。这个部件实际上对应板子上的EPCS器件。因为UP3板子上使用的是EPCS1,而mk_target_board默认设置的是EPC4,所以更改asmi设置。如图9;

图9 修改asmi的设置

⑼ 添加Avalon Tri-State Bridge。选择Bridges > Avalon Tri-State Bridge。如图10;

图10 添加Avalon Tri-State Bridge

⑽ 添加板子上所有与FPGA相连的flash器件。选择Memory > Flash Memory (Common Flash Interface)。

板子上有多少与FPGA相连的flash器件要通过Nios II IDE提供的Flash Programmer来烧写,那么就要添加多少个对应的flash部件。其中,板子上的EPCS器件不需要添加,因为mk_target_board执行时,已经把它添加到Nios II系统中了,即module name为asmi的部件。如果板子上flahs部件与Altera提供的flash部件不同,那么就要自己来设置参数。每个flash芯片都要有一个标号,这个标号我觉得是用于烧写时指定要烧写的flash芯片用的,所以flash芯片和标号必须一一对应,两个不同的flash不能使用同一个标号。这里添加的UP3板子上的flash芯片,参数的设置如图11、12;

图11 UP3上flash芯片的attributes设置

图12 UP3上flash芯片的Timing设置

⑾ 可根据自己需要修改部件的Module Name。这个步骤不是必须的。修改后的System Contents页,如图13;

图13 各个部件设置好之后的System Contents页

⑿ 选择More “Board_System” Settings页,设置硬件映象。可根据需要设置多个硬件映象。在本实例中只设置一个user模式的硬件映象。如图14:

图14 设置硬件映象

这里设置user模式下,配置文件存在asmi上,偏移地址为0。这样设置可以Nios II IDE的Flash Programmer将配置文件烧写到asmi上,这样板子一上电EPCS芯片能够配置FPGA;

⒀ 生成系统。选择System Generation页,取消simulation的选定,然后点击Generate;

⒁ 退出SOPC Builder。系统生成完成以后,点击Exit;

⒂ 配置Target Board的project的顶层实体。这是关键步骤,必须细心的检查设置。

在.bdf文件中,首先更新Nios II系统;然后添加必要的逻辑,例如对Nios II系统引出来的逻辑以及flash的逻辑要设置正确;凡是共享总线的非flash器件都要禁用,具体方法就是把片选信号直接接vcc或者gnd(根据片选信号的逻辑来接vcc还是接gnd),使它disable;添加input、output、biput等。针对UP3板子,这里还需要添加PLL,用来产生96MHz的clk信号。对板子上的flash芯片如图15;

图15 设置好的.bdf文件

⒃ 逻辑综合、配置引脚、编译。这个和普通project流程一样。

编译完成后,Target Board就做好。制作Target Board的关键步骤在SOPC Builder里的配置和project顶层实体的配置。

4. 如何添加Target Board?

若自己制作了Target Board,那么在SOPC Builder里的Target Board下拉菜单中就会有对应的Target Board可选,如图16。

<!--[endif]-->

<!--[endif]-->

图16 Target Board下拉菜单

如果没有的话,或者直接现成的Target Board的话,需要添加Target Board的路径。添加方法是在SOPC Builder里,选择File > SOPC Builder Setup,在Componet/Kit Library Search Path里添加,如图17。这里添加了两个Target Board的路径。

图17 添加Target Board的路径

5. 小结

⑴ 制作Target Board,必须明白FPGA芯片是如何配置的,Nios系统是如何启动的,建议用户阅读相关资料。例如Nios II Flash Programmer User Guide;

⑵ 制作Target Board,需要对了解板子上所有flash芯片,建议制作之前阅读flash芯片的datasheet;

⑶ 制作Target Board,需要了解板子上flash芯片的连接情况,建议制作之前查看板子的原理图。 [align=right][color=#000066][此贴子已经被作者于2007-4-24 18:01:29编辑过][/color][/align]

我要赚赏金

我要赚赏金