我用quartusII的megawizard生成了一个锁相环,请问怎么用moelsim来仿真?

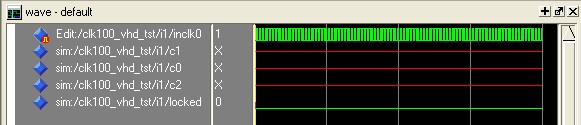

我把库编译好了,然而仿真时输出是不定态,如下图所示。我觉得不应该是输出还没有锁定,因为我的输入时钟周期是20ns的,而我仿真时长为2us,不可能还没锁定,而且即使没有锁定也不该是不定态,也是有输出的,请问是怎么回事呢?

我自己新建了一个工程:Quartus II V9.1, Modelsim SE 6.5C, EP2C35F672C6, Verilog

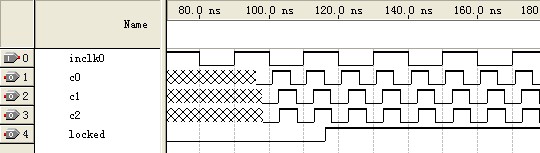

Modelsim下做行为仿真,结果正确:

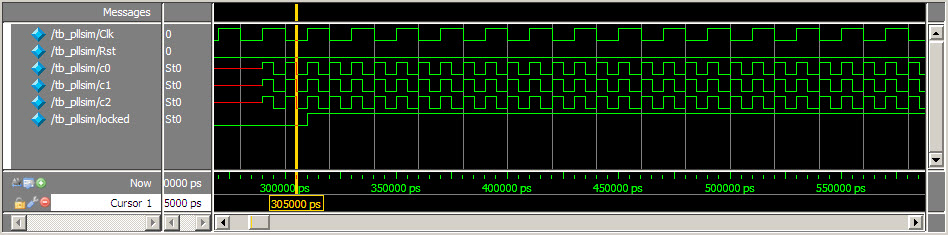

Quartus II下仿真结果和你的一样。

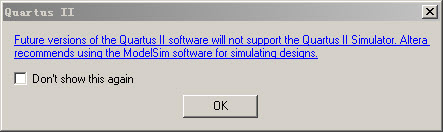

Quartus II做仿真时有提示如下:

我想应该就是这个原因。看来Altera打算放弃自己的Simulator了。

如果需要的话,我可以把工程上传。

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |