2.Virtex系列FPGA

Virtex系列是赛灵思的高端产品,也是业界的顶级FPGA产品,赛灵思公司正是凭借Virtex系列产品赢得市场,从而获得FPGA供应商领头羊的地位。可以说赛灵思以其Virtex-5、Virtex-4、Virtex-2 Pro和Virtex-2系列FPGA产品引领现场可编程门阵列行业。主要面向电信基础设施、汽车工业、高端消费电子等应用。目前的主流芯片包括:Vitrex-2、Virtex-2 Pro、Virtex-4和Virtex-5等种类。

(1)Vitrex-2系列

Vitrex-2系列具有优秀的平台解决方案,这进一步提升了其性能;且内置IP核硬核技术,可以将硬IP核分配到芯片的任何地方,具有比Virtex系列更多的资源和更高的性能。其主要特征如下所示: 采用0.15/0.12 工艺; 核电压为1.5V,工作时钟可以达到420MHz; 支持20多种I/O接口标准; 内嵌了多个 硬核乘法器,提高了DSP处理能力; 具有完全的系统时钟管理功能,多达12个DCM模块。

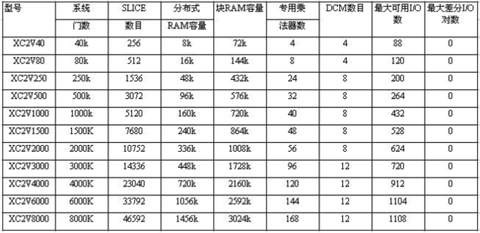

Virtex-2系列产品的主要技术特征如下表所示。

表3-10 Virtex-2系列 FPGA主要技术特征

(2)Virtex-2Pro系列

Virtex-2 Pro系列在Virtex-2的基础上,增强了嵌入式处理功能,内嵌了PowerPC™405内核,还包括了先进的主动互联(Active Interconnect)技术,以解决高性能系统所面临的挑战。此外还增加了高速串行收发器,提供了千兆以太网的解决方案。其主要特征如下所示: 采用0.13 工艺; 核电压为1.5V,工作时钟可以达到420MHz; 支持20多种I/O接口标准; 增加了2个高性能RISC技术、频率高达400MHz的PowerPC™处理器;增加多个3.125Gbps速率的Rocket串行收发器; 内嵌了多个 硬核乘法器,提高了DSP处理能力; 具有完全的系统时钟管理功能,多达12个DCM模块。

Virtex-2 Pro系列产品的主要技术特征如下表所示。

表3-11 Virtex-2 Pro系列 FPGA主要技术特征

(3)Virtex-4系列

Virtex-4器件整合了高达200,000个的逻辑单元,高达500 MHz的性能和无可比拟的系统特性。Virtex-4产品基于新的高级硅片组合模块(ASMBL)架构,提供了一个多平台方式(LX、SX、FX),使设计者可以根据需求选用不同的开发平台;逻辑密度高,时钟频率能够达到500MHz;具备DCM模块、PMCD相位匹配时钟分频器、片上差分时钟网络;采用了集成FIFO控制逻辑的500MHz SmartRAM技术,每个I/O都集成了ChipSync源同步技术的1 Gbps I/O和Xtreme DSP逻辑片。其主要特点如下: 采用了90 工艺,集成了高达20万的逻辑单元;系统时钟500MHz; 采用了集成FIFO控制逻辑的500MHz Smart RAM 技术; 具有DCM模块、PMCD相位匹配时钟分频器和片上差分时钟网络; 每个I/O都集成了ChipSync源同步技术的1Gbps I/O; 具有超强的信号处理能力,集成了数以百计的XtremeDSP Slice,单片最大的处理速率为 。 Virtex-4 LX平台FPGA的特点是密度高达20万逻辑单元,是全球逻辑密度最高的FPGA系列之一,适合对逻辑门需求高的设计应用。

Virtex-4 SX平台提高了DSP、RAM单元与逻辑单元的比例,最多可以提供512个XtremeDSP硬核,可以工作在500MHz,其最大的处理速率为 ,并可以以其创建40多种不同功能,并能多个组合实现更大规模的DSP模块。与Virtex-2 Pro系列相比,还大大降低了成本和功耗,具有极低的DSP成本。SX平台的FPGA非常适合应用于高速、实时的数字信号处理领域。

Virtex-4 FX平台内嵌了1~2个32位RISC PowerPC™处理器,提供了4个1300 Dhrystone MIPS、10/100/1000自适应的以太网MAC内核,协处理器控制器单元(APU)允许处理器在FPGA中构造专用指令,使FX器件的性能达到固定指令方式的20倍;此外,还包含24个Rocket I/O串行高速收发器,支持常用的0.6Gbps、1.25 Gbps、2.5 Gbps、3.125 Gbps、4 Gbps、6.25 Gbps、10 Gbps等高速传输速率。FX平台适用于复杂计算和嵌入式处理应用。

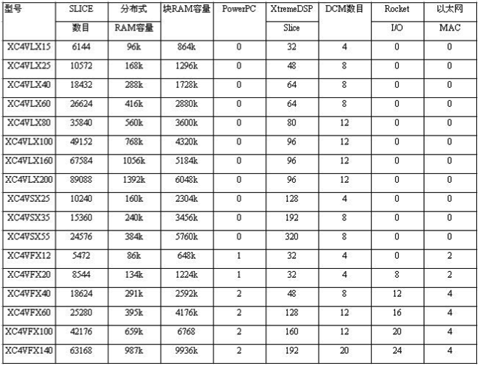

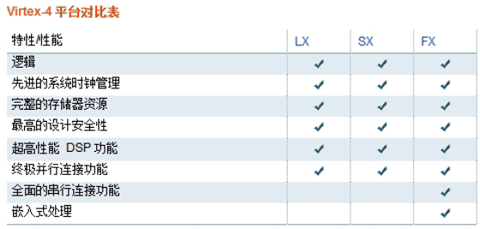

Virtex-4系列产品的主要技术特征如下表所示。

表3-12 Virtex-4系列 FPGA主要技术特征

表3-13 Virtex-4系列平台性能对比

(5)Virtex-5系列

Virtex®-5 FPGA 是世界上首款 65nm FPGA 系列,采用 1.0v、三栅极氧化层工艺技术制造而成,并且根据所选器件可以提供 330,000 个逻辑单元、1,200 个 I/O 引脚、48 个低功耗收发器以及内置式PowerPC™440、PCIe® 端点和以太网 MAC 模块。已经提供了5种系列平台,分别是LX、LXT 、SXT、FXT、TXT,每种平台都在高性能逻辑、串行连接功能、信号处理和嵌入式处理性能方面实现了最佳平衡。例如LX针对高性能逻辑进行了优化,LXT针对具有低功耗串行连接功能的高性能逻辑进行了优化,SXT针对具有低功耗串行连接功能的DSP 和存储器密集型应用进行了优化。Virtex-5 FXT 则用于实现具有速率最高的串行连接功能的嵌入式处理,Virtex-5 TXT可用于实现超高带宽应用,如有线通信与数据通信系统内的桥接、开关和集聚。

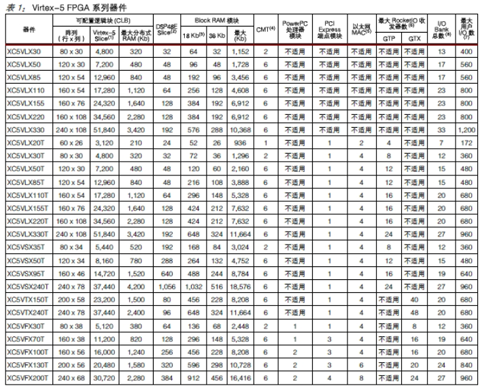

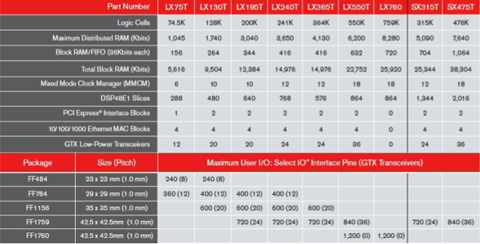

现有的Virtex-5系列产品的主要技术特征如下表所示。

表3-14 Virtex-5系列 FPGA主要技术特征

其主要特点如下:

采用了最新的65工艺,结合低功耗IP块将动态功耗降低了35%;此外,还利用65nm三栅极氧化层技术保持低静态功耗; 利用65nm ExpressFabric技术,实现了真正的6输入LUT,并将性能提高了2个速度级别。内置有用于构建更大型阵列的FIFO逻辑和ECC的增强型36 Kbit Block RAM带有低功耗电路,可以关闭未使用的存储器。 逻辑单元多达330,000个,可以实现无与伦比的高性能; I/O引脚多达1,200个,可以实现高带宽存储器/网络接口,1.25 Gbps LVDS; 低功耗收发器多达24个,可以实现100 Mbps - 3.75 Gbps高速串行接口; 核电压为1V,550 MHz系统时钟; 550 MHz DSP48E slice内置有25 x 18 MAC,提供352 GMACS的性能,能够在将资源使用率降低50%的情况下,实现单精度浮点运算; 利用内置式PCIe端点和以太网MAC模块提高面积效率 ; 更加灵活的时钟管理管道(Clock Management Tile)结合了用于进行精确时钟相位控制与抖动滤除的新型PLL和用于各种时钟综合的数字时钟管理器(DCM); 采用了第二代sparse chevron封装,改善了信号完整性,并降低了系统成本; 增强了器件配置,支持商用flash存储器,从而降低了成本。

注:一个Virtex-5 Slice具有4个LUT和4个触发器,而一个前文所提及的常规Slice只包含2个LUT个2个触发器。每个DSP48E包含一个25*18位的硬核乘法器、一个加法器和一个累加器。

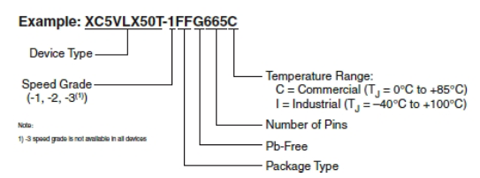

Virtex-5 FPGA 订购信息适用于所有封装,包括无铅封装

(6)Virtex-6 FPGA系列

基于采用第三代Xilinx ASMBL™ 架构的40nm制造工艺,Virtex-6 FPGA系列还拥有新一代开发工具和早已针对Virtex-5 FPGA而开发的广泛IP库支持。这些都为多产的开发和设计移植提供了强大的支持。 与竞争厂商提供的40nm FPGA产品相比,新的Virtex-6 FPGA系列器件性能提高15%,功耗降低15%。新器件在1.0v内核电压上操作,同时还有可选的0.9v低功耗版本。 这些使得系统设计师可在设计中采用Virtex-6 FPGA,从而支持建设“绿色”中心办公室和数据中心。对于电信行业这一点特别重要,因为该行业正在扩展对因特网视频和富媒体内容的支持。

Virtex- 6 FPGA系列包括三个面向应用领域而优化的FPGA平台,分别提供了不同的特性和功能组合来更好地满足不同客户应用的需求:

Virtex-6 LXT FPGA—优化目标应用需要高性能逻辑、DSP以及基于低功耗GTX 6.5Gbps串行收发器的串行连接能力。

Virtex-6 SXT FPGA—优化目标应用需要超高性能DSP以及基于低功耗GTX 6.5Gbps串行收发器的串行连接能力。

Virtex-6 HXT FPGA—作为优化的通信应用需要最高的串行连接能力,多达64个GTH串行收发器可提供高达11.2Gbps带宽 。

Virtex-6 FPGA把先进的硬件芯片技术、创新的电路设计技术以及架构上的增强完美结合在一起,与前一代Virtex器件以及竞争FPGA产品相比,功耗大大降低,性能更高并且成本更低。表3-15显示了Virtex-6FPGA系列主要技术特征。

表3-15 Virtex-6 FPGA系列主要技术特征

(7)Xilinx PROM芯片介绍

赛灵思公司的Platform Flash PROM能为所有型号的Xilinx FPGA提供非易失性存储。全系列PROM的容量范围为1Mbit到32Mbit,兼容任何一款Xilinx FPGA芯片,具备完整的工业温度特性(-40°C 到 +85°C),支持IEEE1149.1所定义的JTAG边界扫描协议。

PROM芯片可以分成3.3V核电压的 系列和1.8V核电压的 系列两大类,前者主要面向底端引用,串行传输数据,且容量较小,不具备数据压缩的功能;后者主要面向高端的FPGA芯片,支持并行配置、设计修订(Designing Revisioning)和数据压缩(Compression)等高级功能,以容量大、速度快著称,其详细参数如下表所示。

表3-16 赛灵思公司PROM芯片总结 (截至2008年11月数据)

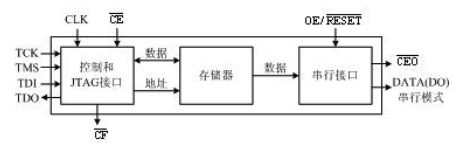

该系列包含XCF01S、XCF02S和XCF04S(容量分别为:1Mb、2Mb和4Mb),其共同特征有3.3V核电压,串行配置接口以及SOIC封装的VO20封装。 内部控制信号、数据信号、时钟信号和JTAG信号的整体结构如图3-2所示。

图3-2 XCF01S/XCF02S/XCF04S PROM结构组成框图

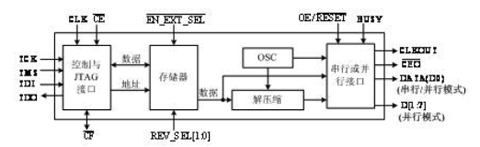

系列有XCP08P、XCF16P和XCF32P(容量分别为:8Mb、16Mb和32Mb),其共同特征有1.8V核电压、串行或并行配置接口、设计修订、内嵌的数据压缩器、FS48封装或VQ48封装和内嵌振荡器。 内部控制信号、数据信号、时钟信号和JTAG信号的整体结构如图3-3所示,其先进的结构和更高的集成度在使用中带来了极大的灵活性。

图3-3 XCP08P/XCF16P/XCF32P PROM结构组成框图

值得一提的是系列设计修正和数据压缩这两个功能。设计修订功能在FPGA加电启动时改变其配置数据,根据所需来改变FPGA的功能,允许用户在单个PROM中将多种配置存储为不同的修订版本,从而简化FPGA配置更改,在FPGA内部加入少量的逻辑,用户就能在PROM中存储多达4个不同修订版本之间的动态切换。数据压缩功能可以节省PROM的空间,最高可节约50%的存储空间,从而降低成本,是一项非常实用的技术。当然如果编程时在软件端采用了压缩模式,则需要一定的硬件配置来完成相应的解压缩。

我要赚赏金

我要赚赏金