不知大家注意过这个问题没有,最近在画一电路图,发现了很多平时不太注意的问题,现拿来大家讨论一下,今就先拿JTAG说事吧:不实际动手不知道,今在画JTAG管脚的时候偶尔多搜了一下,发现个很奇怪的问题,在ST提供的中文版的datasheet上有下面一段话

● JNTRST:带上拉的输入

● JTDI:带上拉的输入

● JTMS/SWDIO:带上拉的输入

● JICK/SWCLK:带下拉的输入

● JTDO:浮动输入

软件可以把这些I/O口作为普通的I/O口使用。

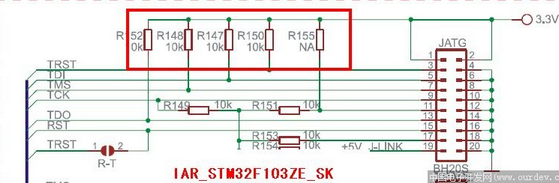

注意: JTAG IEEE标准建议对TDI,TMS和nTRST上拉,而对TCK没有特别的建议。但在STM32F10xxx中,JTCK引脚带有下拉。内嵌的上拉和下拉使芯片不再需要外加外部电阻。“内嵌的上拉和下拉使芯片不再需要外加外部电阻。” 但是在 “STM3210E-EVAL”的sch里,发现它却没按手册里面来操作,瞬感无从下手,于是多找了几个图来看,发现真是千奇百怪啊:如下图。

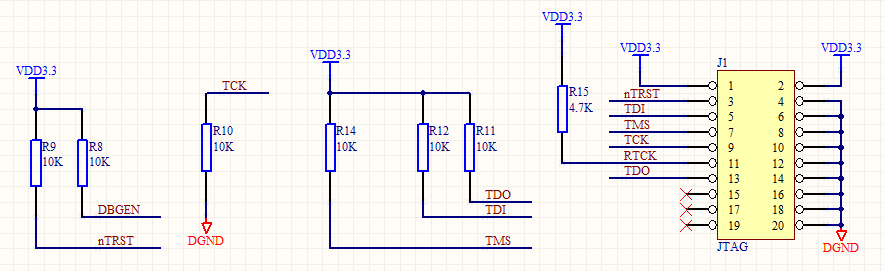

再来一个

图三

图三

图四

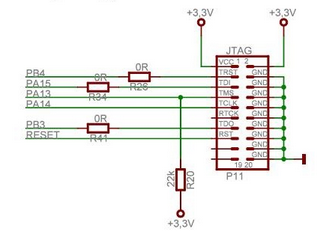

这个是我采用的,10管教的

大家说说自己的看法呗。。。

探讨一个关于JTAG管脚上下拉电阻的问题

关键词: 探讨 一个 关于 脚上 下拉 电阻 问题

回复

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金

我要赚赏金