传统收发器设计中,50 Ω单端接口广泛用于射频和中频电路。当电路进行互连时,应全部具有匹配的50 Ω输出和输入阻抗。然而在现代收发器设计中,差分接口常用在中频电路中以获得更好的性能,但实际设计过程中,工程师需要处理几个常见问题,包括阻抗匹配、共模电压匹配以及复杂的增益计算。了解发射机和接收机中的差分电路对优化增益匹配和系统性能很有帮助。

差分接口优势

差分接口有三大主要优势。首先,差分接口可抑制外部干扰和接地噪声。其次,它可以抑制偶次阶输出失真。这对于零中频(ZIF)接收机非常重要,因为出现在低频信号中的偶次阶成分无法滤除。第三,输出电压可达到单端输出的两倍,从而将给定电源上的输出线性度提高6 dB。

本文论述三种情况下的接口解决方案:ZIF接收机、超外差式接收机和发射机。这三种架构广泛用于射频拉远单元(RRU)、数字直放站和其他无线测试仪器中。

ZIF接收机接口设计和增益计算

在零中频(ZIF)接收机设计中,IF信号是复信号,直流和低频率信号来提供有用信息。典型解调器在驱动200 Ω至450 Ω负载时可提供最佳性能,同时ADC驱动器的输入阻抗一般并非50 Ω,因此设计系统时采用直流耦合很重要也很困难。

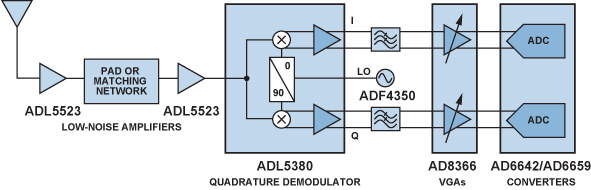

图1显示了一个ZIF接收机配置,它使用两个低噪声放大器(LNA) ADL5523 一个400MHz至6000MHz正交I/Q解调器ADL5380、一个作为本振(LO)的宽带频率合成器ADF4350以及一个双通道数字可编程可变增益放大器(VGA)AD8366。表1显示了相关ADL5380接口和增益参数。

图1. ZIF接收机框图

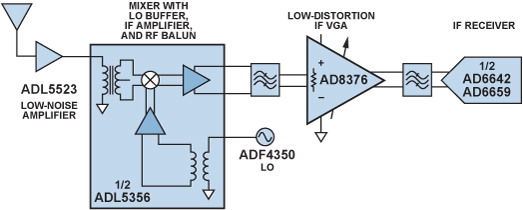

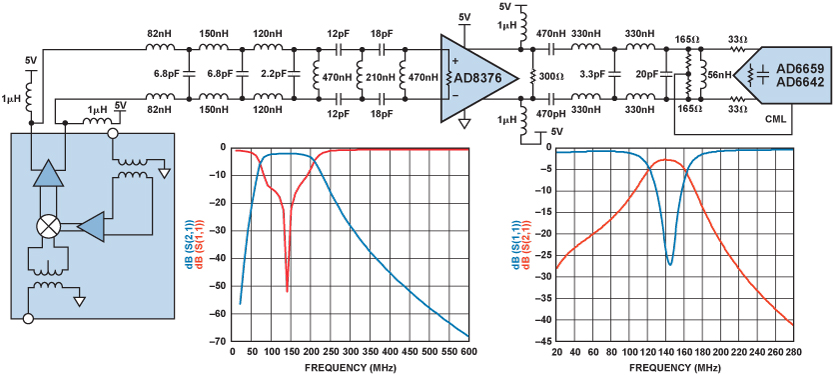

图4.超外差式接收机接口框图和滤波器仿真结果

图4.超外差式接收机接口框图和滤波器仿真结果

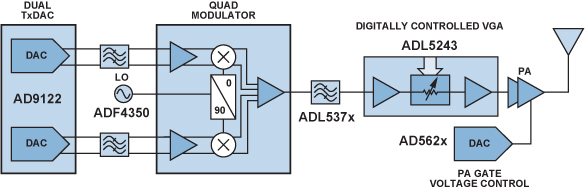

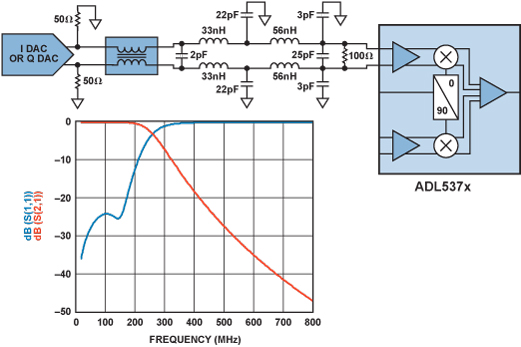

图6.直流耦合发射机IF接口框图和滤波器仿真结果

图6.直流耦合发射机IF接口框图和滤波器仿真结果

我要赚赏金

我要赚赏金