接口元件简介

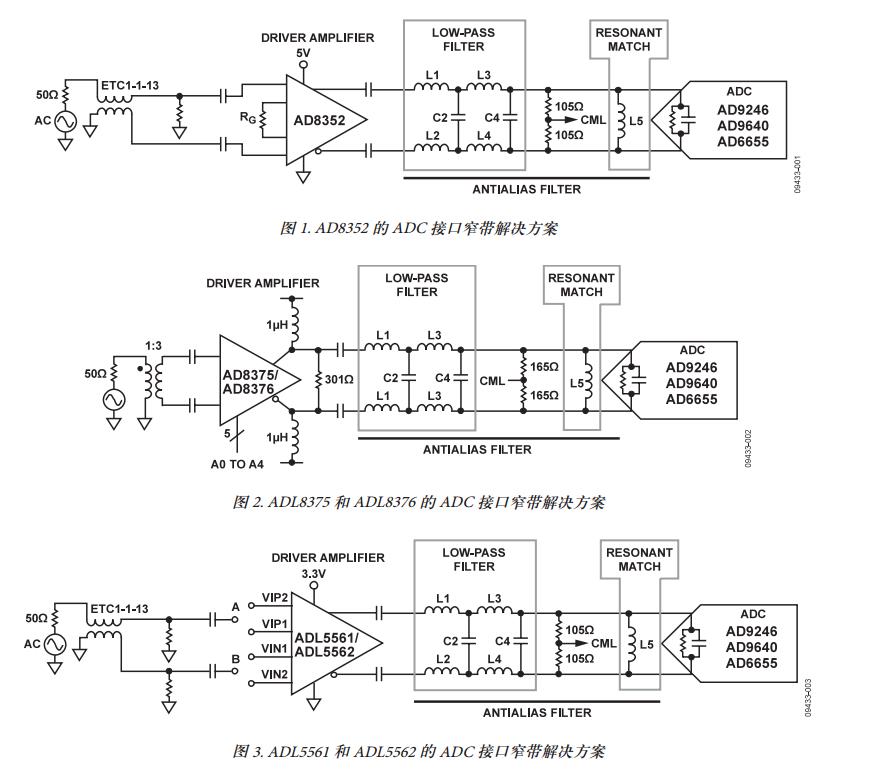

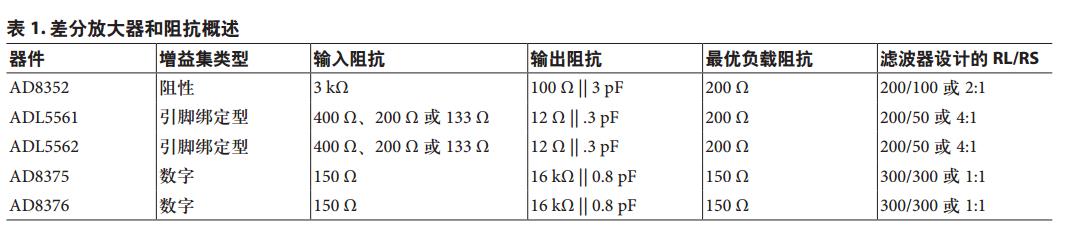

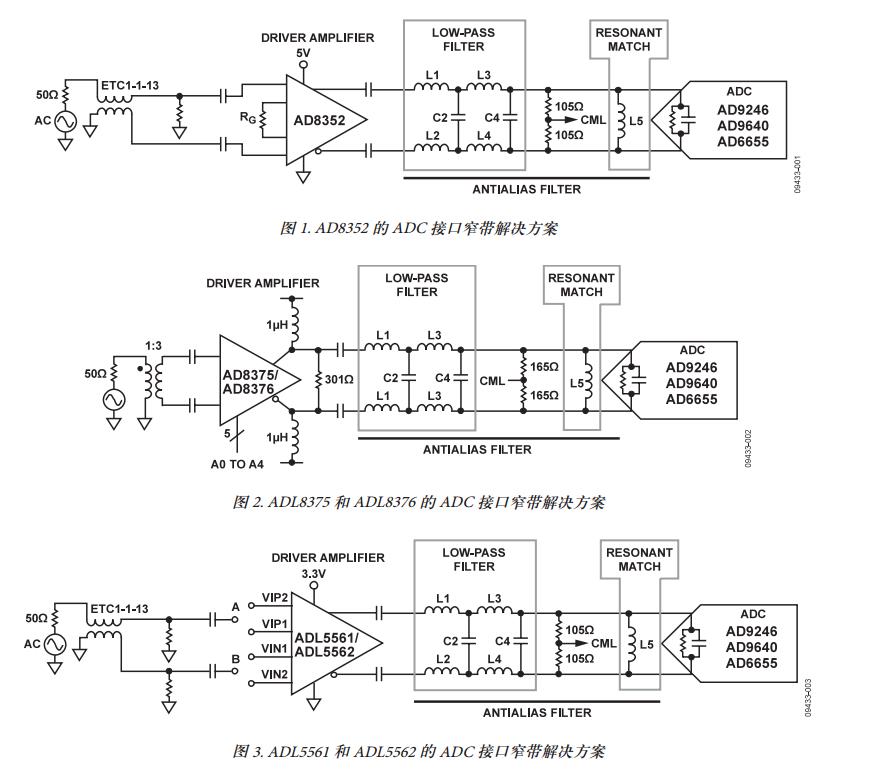

窄带接口用来提供带通滤波,同时提供足够的阻抗变换。图 1、2 和 3 所示为不同放大器 ADC 接口窄带方案的功能框图。这四种主要元件模块,即驱动放大器、低通滤波器、共振匹配和 ADC,在接口定义中起到了关键作用,每一种都需要审慎对待。下列章节介绍每一种元件的具体要求。

差分驱动放大器

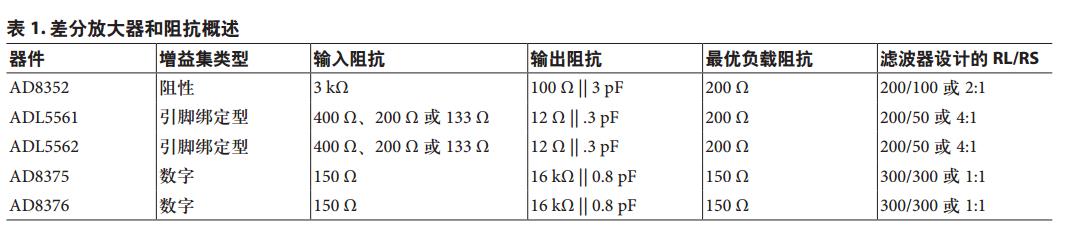

ADI 公司差分放大器产品齐全,其中包括 AD8352、AD8375、AD8376、ADL5561 和 ADL5562,提供三种基本的增益控制类型 :电阻设定增益、并联数字控制和引脚绑定增益。为优化性能,这些增益控制类型各具有自己的输出阻抗集和所需阻抗负载,具体如表 1 所概述。

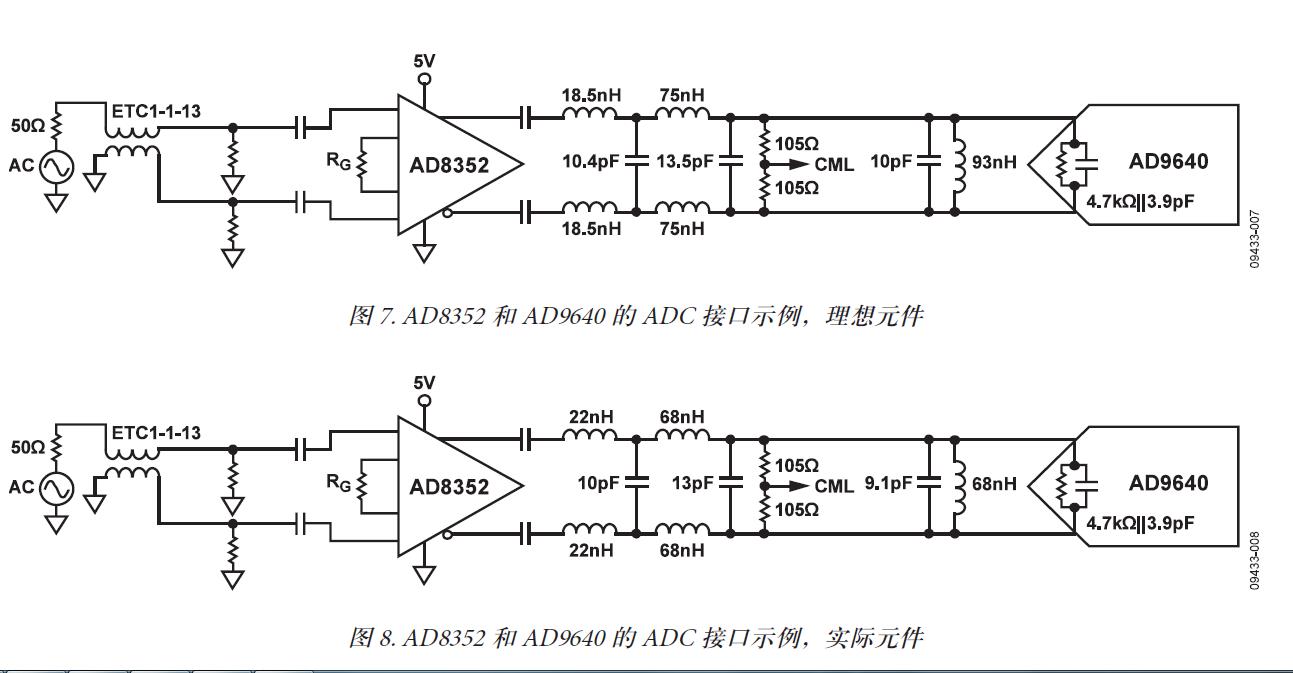

AD8352

AD8352 使用增益设置电阻 RG 来设置增益,该电阻具有将器件与信号输入隔离的缓冲器。因此,对于 3 dB 至 25 dB的增益,AD8352 可保持恒定的 3 kΩ 输入电阻,从而降低了匹配和输入驱动要求。有关增益调节的详情,请参见AD8352 的数据手册。

建议在输入和输出上连接交流耦合电容以隔离 VCC/2 偏压与源和平衡负载。

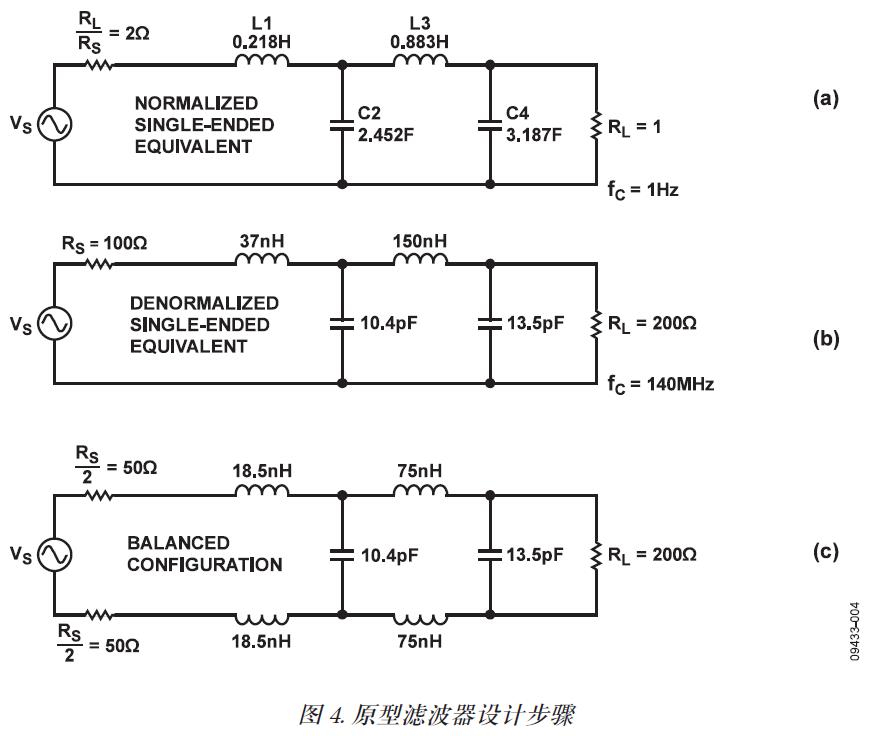

AD8352 具有 100 Ω 的标称差分输出电阻,在负载阻抗等于200 Ω时可实现最佳交流性能。这需要2:1的RL/RS 滤波器比,其中 RS 为滤波器源阻抗,RL 为负载阻抗。

AD8375 和 AD8376

AD8375 是一款单通道、数字控制、可变增益放大器,而AD8376 是其双通道版本。各通道通过独立的 5 位二进制代码来编程,以 1 dB 步进改变各衰减器的设置,使得各放大器通道的增益设置范围为 +20 dB(代码 0)至 −4 dB(代码 24 及更高)。

AD8375 和 AD8376 提供 150Ω 输入阻抗,经调谐驱动 150 Ω负载阻抗,以获得最佳性能。开集输出结构要求通过外部偏置网络实现直流偏置。每个通道输出端均采用一组 1 μH扼流圈电感,用来向开集输出引脚提供偏置,这些引脚具有 16 kΩ 的差分输出阻抗。由于差分输出偏置为正电源,需要连接交流耦合电容,最好是 0.1 μF。同样,输入引脚处于高于地约 2 V 的偏置电压下,也应进行交流耦合。

在没有任何输出匹配的情况下,如果 RL/RS 滤波器比很小,构成滤波器可能需要不切实际的大电感值和极小的电容值。阻抗比越大,对元件 Q 值和布局寄生就越要谨慎。建议采用大约 300 Ω 的分流输入和输出电阻来端接抗混叠滤波器。在图 2 示例中,滤波器两端的分流电阻在输入端为301 Ω,在输出端为 330 Ω(通过两个 165 Ω 偏置设置电阻),两者一起为 AD8375 或 AD8376 提供形成标称 150 Ω 负载阻抗,并产生更有利的 RL/RS 滤波器比1:1。

ADL5561 和 ADL5562

ADL5561 和 ADL5562 通过引脚绑定输入配置来设置增益。

对 VIP1 施加输入 A、对 VIN1 施加输入 B 时,增益为 6 dB(最小增益)。对 VIP2 施加输入 A、对 VIN2 施加输入 B 时,增益为 12 dB(最小增益)。对 VIP1 和 VIP2 施加输入 A、对VIN1和VIN2施加输入B时,增益为15.5 dB(最小增益)。注意,差分输入阻抗随增益绑定选择而变化 :最小、中等和最大增益设置分别对应 400 Ω、200 Ω 和 133 Ω。有关输入匹配的详情,请参见 ADL5561 或 ADL5562 数据手册。

建议在输入和输出上连接交流耦合电容以隔离 VCC/2 偏压与源和平衡负载。

该负载应等于 200 Ω 以提供最佳交流性能。ADL5561 和ADL5562 的差分输入阻抗为 12 Ω。阻抗比越大,对元件 Q值和布局寄生就越要谨慎。为了简化滤波器设计,可在每个差分输出端增加约 15 Ω 的额外串联填充,以采用更有利的 RL/RS 滤波器比 4:1。注意,添加的串联元件将衰减驱动器放大器输出。

ADC 特性

在现代无线接收器设计中,高采样率的模数转换器 (ADC)通常被用作中频复合调制信号的采样。基于 CMOS 开关电容的 ADC 因其低成本和低功耗而成为这类设计的首选。这类 ADC 的前端为非缓冲型,直接耦合至采样网络,所以 ADC 的输入阻抗会随时间(跟踪和保持模式切换时)变化,这就对驱动 ADC 的放大器提出了挑战。为了在驱动 ADC 的同时获得极小的噪声和信号失真,有必要设计一种无源网络接口,实现宽带噪声抑制和采样保持阻抗的变换,从而为驱动放大器提供一个更匹配的负载阻抗。建议在多个常用 IF 频率下采用谐振法将采样保持阻抗变换为可预测性的负载,从而更精确地设计抗混叠滤波器。

抗混叠滤波器

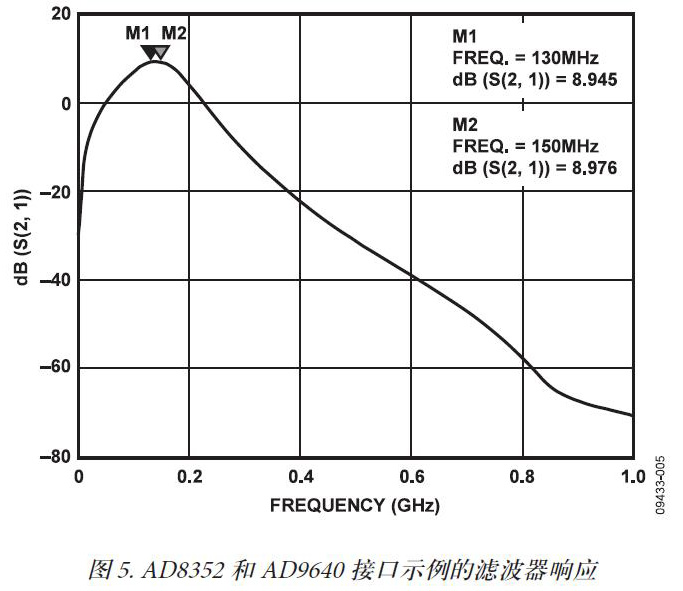

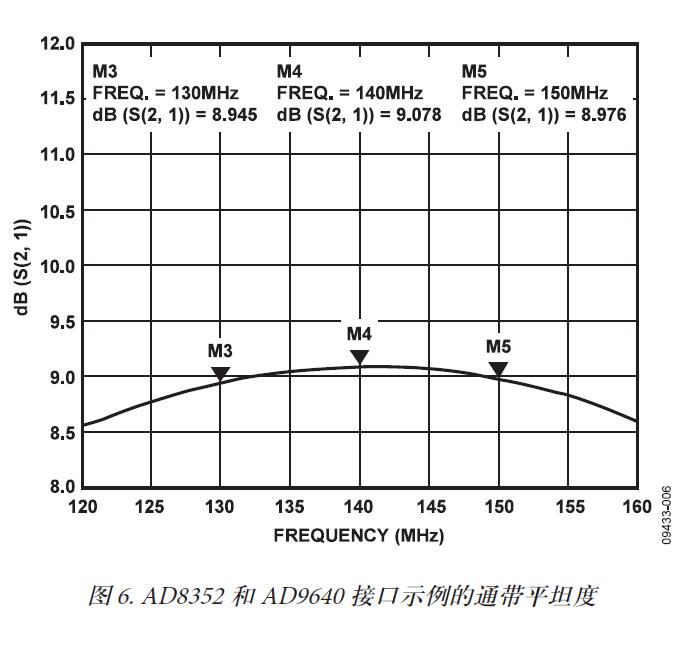

抗混叠滤波器由四阶巴特沃兹低通滤波器和谐振电路组成。谐振电路通过谐振消除 ADC 负载的容性部分,有助于确保 ADC 输入在目标中心频率看起来像一个真正的电阻(参见应用笔记 AN-742 和 AN-827)。整体频率响应呈现出带通特性,有助于抑制目标奈奎斯特频率区域外的噪声。一般而言,若用一个恰当阶数的抗混叠滤波器,SNR性能会提高数个 dB。

低通滤波器

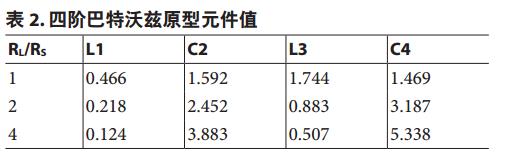

用作抗混叠滤波器的低通滤波器往往采用 LC 网络设计,必须完好定义源阻抗和负载阻抗以获得所需阻带。为设计滤波器网络,可使用各种滤波器合成的手册。通常用切比雪夫 (Chebyshev) 或巴特沃兹 (Butterworth) 多项式来定义滤波器传递函数。有几种基于软件的滤波器设计程序有助于简化这一问题,如来自 Nuhertz Technologies 的 Filter Free4.0 或 Agilent Technologies 推 出 的 Advanced Design System(ADS,高级设计系统)。RL/RS 滤波器比和滤波器阶数必须小心对待,其中 RS 为滤波器源阻抗,RL 为负载阻抗。增加阶次会增加不必要的复杂度,递减效益,所以本应用笔记建议采用差分四阶巴特沃兹滤波器。

谐振匹配

谐振匹配或储能电路有助于确保 ADC 输入在目标中心频率处看起来像一个真实电阻(详情见 AN-742 和 AN-827 应用笔记)。分流电感 L5 与片内 ADC 输入电容和低通滤波器 C4 最后一级所提供电容的一部分并联,形成一个谐振电路。

谐振电路的窄谐振频带可为抗混叠滤波器提供整体带通频率响应,从而有助于抑制目标奈奎斯特频率区域外的噪声。

我要赚赏金

我要赚赏金