交作业失败,这是第二次编辑发布了

作业完成得不够认真,还请版主见谅!

以下时完成作业时的一些记录,和一些问题,希望能够得到答复。

顺序是:先完成子图,然后再用层次原理图设计思想将子图连接起来的。

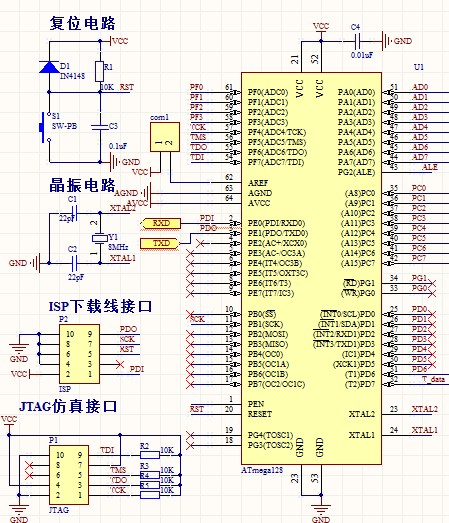

1. AVR单片机——最小系统(建立原理图库)

不知道单片机的最小系统由哪些模块组成,应该是这样的:最小系统=复位电路+晶振电路+单片机芯片+下载/调试电路+电源电路。至于电源,不管电源电路怎样,在原理图中给个VCC,GND应该就可以了。参考开发板原理图,见下载/调试电路其实并没有电路,只是一个接口而已,那最小系统中就没有这部分了。那单片机的最小系统就是:

最小系统=复位电路+晶振电路+单片机芯片(接电源)+下载/调试接口

1. 画MEGA128的原理图封装库

(1)重新画封装库吧,先建立自己的封装库,新建一个后缀名为.schlib的库文件,以后在往这个库里加其它库。

(2)打开原理图库后,再左下脚有个SCH library的窗口,打开后可以edit默认的元件,或add一个新的元件。

(3)开始画原理图库,好像可以想怎么画就怎么画,借助自带的基本画图工具,充分发挥你的想象。画了之后调整也很方便。操作更画原理图时差不多一致吧。

疑问:

(1)放置引脚时(快捷键P+P),引脚的属性除了引脚编号和引脚名,其它有属性有没有必要更改?例如该引脚是IO还是Input,还有引脚的符号,作业一中的元件库是指定了引脚IO类型的,但128开发板的原理图似乎没有指定。不过有的引脚类型也不知道是什么类型。我就先把知道类型的还是指定下类型,不知道的就只改引脚编号后引脚名了。

(2)引脚名上的上划线,应该是低电平有效的意思,不知怎么画?我DIY的做法是用划线工具在引脚名上画了根小横线。不过这样做还有设置栅格距离(View—>Grids),不然小横线画不上去,这样画不知是不是正确的画法?

(3)隐藏引脚,参考原理图上有的引脚没有画出,这个建立元件库时,是否有必要把所有引脚都画出,然后再设置隐藏?如果不画出,是否回影响以后关联的的PCB库的制作?

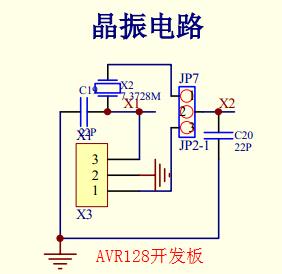

2.晶振电路

AVR 128开发板的晶振电路不太懂,是外部时钟还是什么意思?

我还是用作业一和手册中的晶体振荡器电路吧,用8MHz的晶体振荡器应该不会错。

3. 最小系统电路

最小系统电路就这样么,几个开发板的原理图中ISP/JTAG口的接法有些出入,版主看下可以这样接不?

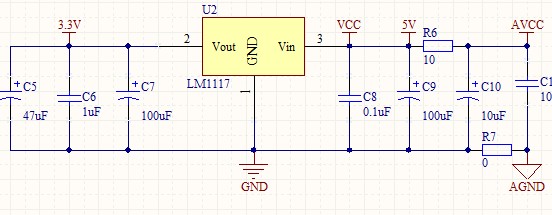

2. 电源模块——USB供电

128的工作电压是4.5V~5.5V,那么我直接用USB供电就可以了。USB接口的电源如今到处都是,这个不用愁了。就这样加上电,电源设计模块也太简单了,那加个USB-RS232芯片,笔记本没有串口,直接插上就可以当串口了。

(1)USB接口(改现有的原理图封装)

官方库里面虽没有USB接口库,但有4口的连接口库,先添加这个4口接口,改一下它的引脚就可以。Properties—>Edit Pins...

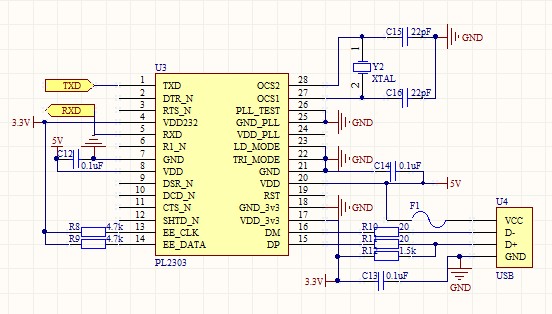

(2)USB串口芯片使用PL2303

这个芯片需要3.3V的电源,那就加一个3.3V的稳压管,其它的电路可能也需要3.3V。

3. USB串口电路

串口引脚复用:128开发板的原理图对串口0进行了复用,ISP下载口与串口进行了复用。因为两者不在同时进行,且ISP下载时使用了复位引脚,因此引脚复用应该没有错。

4. 其它模块

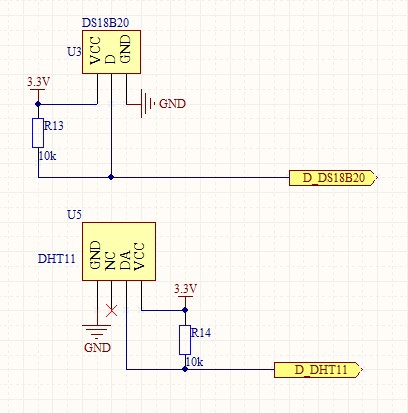

由于时间关系,就只做了温度、湿度传感器

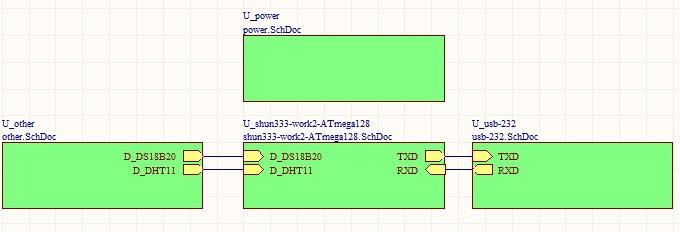

5.层次原理图设计

层次原理图原理就是将子原理图当作符号,在另一个原理图,通过端口“Port”连接起来。

建立好各子原理图后,对于子原理图间的连接,需要使用工具栏中的"Place Port"作为原理图的IO口,如在不同原理图中使用相同的网络标号,编译是不许可的,但应该也不影响PCB布线。

看见参考文档中,有个原理图的各个子图间没有使用“Port”端口,母图就直接将子图放到一起了。

过程:

新建一个原理图,作为母图。

在母图中,右键——>sheet Action ——>Creat sheet Symbol From Sheet,如此可将刚才建的各个原理图文件,以符号的形式放在母图中。连接需要连接的“Port”

在母图中打开子图“Ctrl+双击”

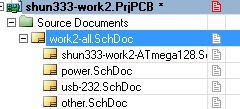

编译过后,这些子图就在母图的目录树下了,如下图所示。

6.编译问题

完成作业后,编译出现错误:duplicate net;网络重复定义了么?

1.原来是不同子图间的网络标号不能相同,只能通过“port”的方式将有关系的子图连接起来,真麻烦。不知道通过设置可不可以更改这个限制?

2.不同子图间的网络标号只允许同时使用VCC和GND符号,网络编号不允许。

我要赚赏金

我要赚赏金