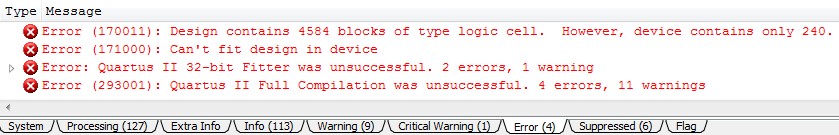

芯片的逻辑单元是有限的,比如我们用的就只有240个。超过了就会报错。这就要我们在编程时注意代码的效率。比如:

1、if...else等含有else的语句,在使用if语句的门闩功能时就会省掉else,这就使得该语句属于不完整的条件表达式,会生成一个含有7位寄存器的结构,引起电路不必要的开销。

2、在定义变量和信号类型的时候,最好规定范围,比如用到整形的时候,我只用到0~9这十个数字,那定义语句为: signal gewei : integer range 0 to 9 ; 它比不规定范围的语句: signal gewei : integer; 要节省好多资源。

3、尽量少用乘法和除法,因为这两个运算占用的资源太多。可以用其他的逻辑语句和加减来代替的尽量代替。

总之VHDL语言是一门严格精确的语言,在使用时注意代码的效率。

我要赚赏金

我要赚赏金