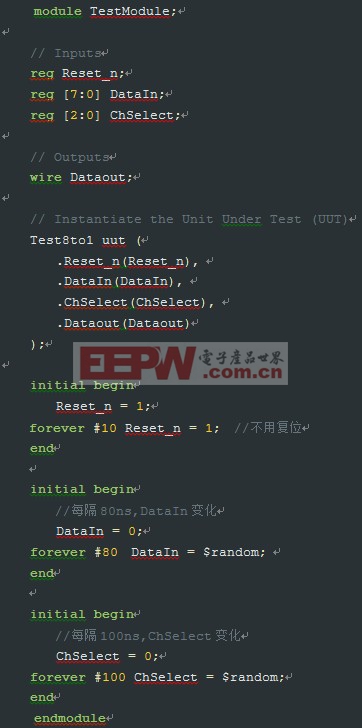

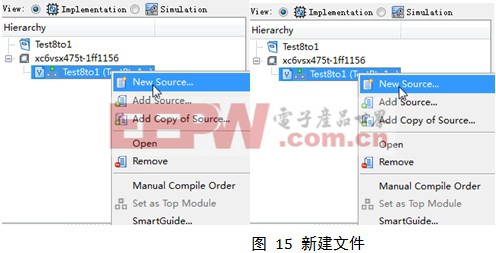

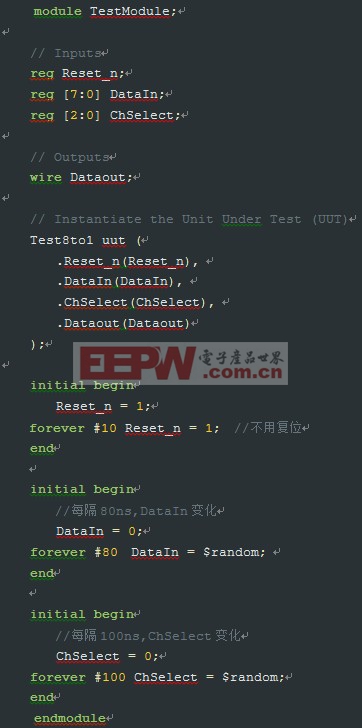

点击Finish就完成了仿真文件的建立,ISE会帮助你将测试模块与被测模块建立好连接,并给出初始化代码,在文件中添加进自己的测试代码,示列代码如下:

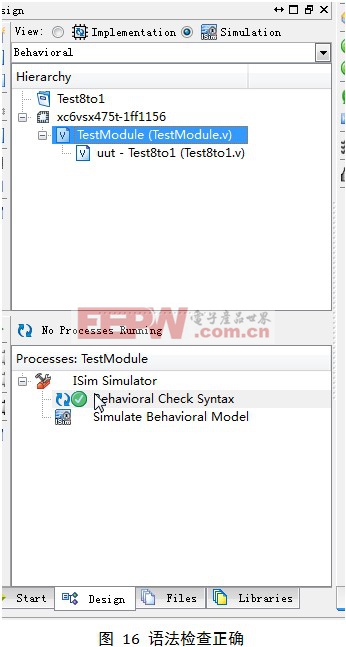

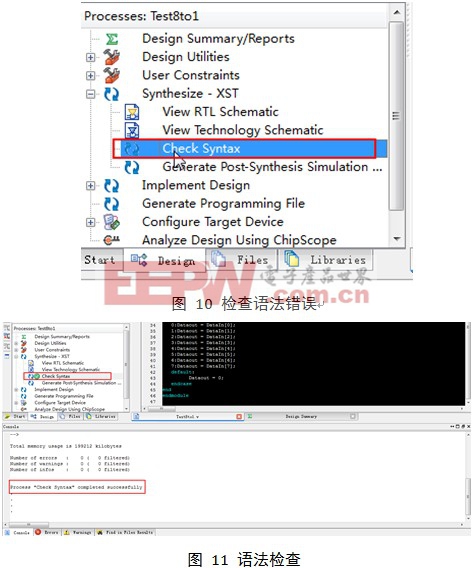

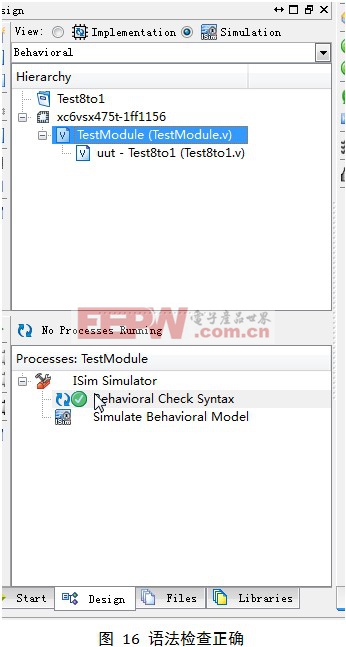

同编写程序一样,编写完成后也需要检查是否有语法错误,点击 Behavioral Check Syntax(如果在建立项目时,选择的不是Isim,将不会出现图16所示的界面,即无法检查语法错误),如果没有语法错误则会出现一个绿色的对勾,如图16所示,此时距离胜利只剩一步了。

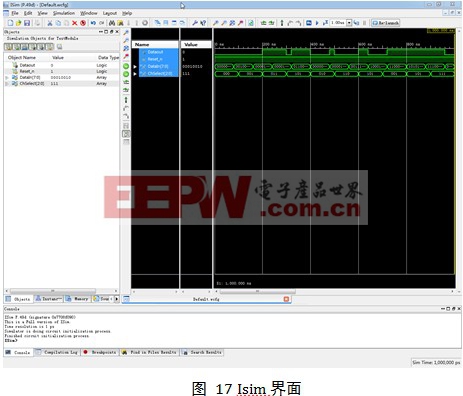

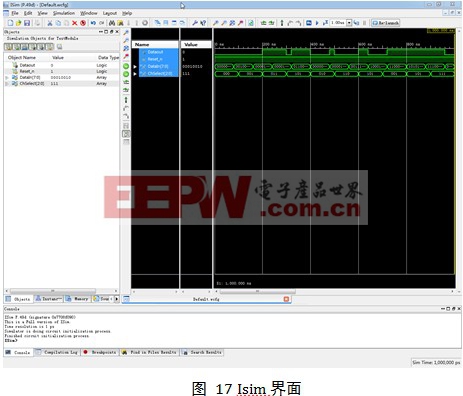

双击 Simulate Behavioral Model,将进入ISE自带的仿真软件,如图17所示,从波形图中可以清楚的看到自己写的程序是否达到了自己所需的功能要求,当然也可以利用Isim进行断点调试,查看中间变量是否正确,也可以利用Isim查看用IP核生成的存储器内部的值。Isim虽然是ISE自带的仿真软件,与专业的仿真软件还有一定距离,但是不可否认的是Isim很方便快捷,很多时候利用Isim进行仿真已经完全足够了。

如果你只是完成一个功能任务,不用下载到硬件板卡上,仿真结果也是正确的,那么此时你的任务已经完成了,深深的祝福你,完成了任务哈。

如果需要下载到硬件平台上,下一步需要建立引脚约束文件(即将模块的输入和输出连接到真实的引脚上),然后生成bit文件,下载到板卡上即可。

在编写Verilog时常见的错误如下:

写了begin,忘了写end,检查时将代码的缩进调整好,每一级都有不同的缩进,这样一眼就看出哪里少了end。

case语句少了endcase,这个地方比较容易遗忘,一旦少了endcase,endcase之后的语句都会报语法错误(Syntax error),如果只是根据编译器提示的错误行,那就没法找到错误了,编程的时候习惯一定要好,写一个case,顺便就把,default和endcase都写上吧。

if语句少了else,这个和第二错误类似,else之后的语句都会报语法错误,加上else之后,错误全都没有了。

输入了中文标点符号,如逗号和分号,这个时候一般错误只定位到一行上,你可能觉得没有错误,不妨把这行删掉再写一次试试。

信号没有初始化,仿真是全是x,一个原因是真的没有初始化,ISE定义的一个信号,如果不给初始值的话,默认就是x;另外一个原因是,模块与模块之间连线没有连上,如果一个模块的信号不是和顶层连在一起而是和另外一个模块连接在一起,则需要再定义,否则是没有连上的。笔者曾经因为犯了这个错误,仿真时一直没有信号输出,苦恼了很久的。

阻塞赋值和非阻塞赋值用在了同一个always里面,这个是不允许的,阻塞(=)赋值是执行完了这一句才会执行下一句,非阻塞(<=)赋值是整个always都跑完了才执行。不过这个错误比较容易找,ISE报错时会定位到相应的行。

我要赚赏金

我要赚赏金