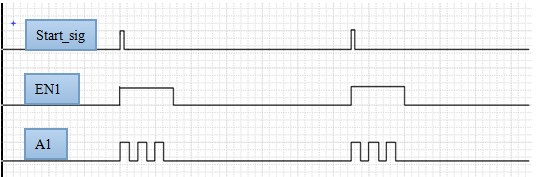

系统时钟为50M 两个脉冲之间的时间为200us 既周期为200us 每当检测到Start_sig EN1拉高12us

A1以4us为周期进行翻转 。

EN1 和A1 这两个信号和start_sig不同步也可以。

下面是我写的程序:

module jifa (

clk, //50m

reset, //低电频有效

start_sig, //触发信号 使模块开始工作

EN1, //第一路ADG1436使能 激发换能器

A1 //第一路ADG1436控制信号

) ;

input clk ;

input reset ;

input start_sig ;

output EN1;

output A1;

reg EN1;

reg A1;

reg [13:0] cnt;

//检测 start_sig 并开始计数

always @(posedge clk or negedge reset)

//if(!reset || start_sig)

if(!reset)

cnt <= 14'd0;

else if(start_sig)

cnt <= 14'd0;

else

cnt <= cnt+1'd1;

//产生ADG1436使能信号EN1

always @(posedge clk or negedge reset)

//if(!reset || start_sig)

if(!reset)

EN1 <= 1'b0;

else if(start_sig) //----->修改对cnt的判断时间以改变EN持续的时间

EN1 <= 1'b0;

else if (cnt == 99 || cnt == 699) //>0<cnt<99时EN为0 cnt计到100使EN翻转为高 700再翻转为低

EN1 <= ~EN1; //600*20ns 使EN持续12us

//产生ADG1436的控制信号

always @(posedge clk or negedge reset) //同上

//if (!reset || start_sig)

if(!reset)

A1 <= 1'b0;

else if(start_sig)

A1 <= 1'b0;

else if (cnt==99 || cnt==199 || cnt==299 || cnt==399 || cnt==499 || cnt==599 || cnt==699)

A1 <= ~A1;

endmodule

有两个问题

第一个问题:感觉我这个程序里面的计数并不是被start_sig控制的 start_sig只不过用来复位

怎么写才能让每当检测到start_sig 就开始不停计数。

第二个问题: //if (!reset || start_sig) 为什么我用这个就不能通过编译,应该怎么修改

新手求教,望指导 谢谢

[丨]

我要赚赏金

我要赚赏金