在运放的应用中,不可避免的会碰到运放的输入失调电压Vos问题,尤其对直流信号进行放大时,由于输入失调电压Vos的存在,放大电路的输出端总会叠加我们不期望的误差。举个简单,老套,而经典的例子,由于输入失调电压的存在,会让我们的电子秤在没经调校时,还没放东西,就会有重量显示。我们总不希望,买到的重量与实际重有差异吧,买苹果差点还没什么,要是买白金戒指时,差一克可是不少的money哦。下面介绍一下运放的失调电压,以及它的计算。最后再介绍一些TI的低输入失调电压运放。不足之处,多多拍砖。

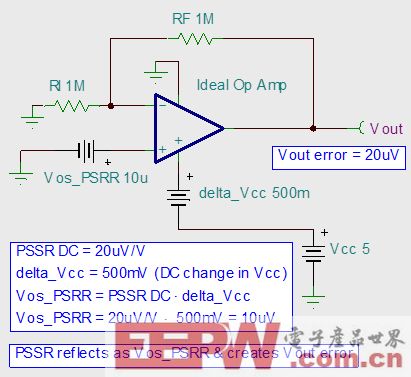

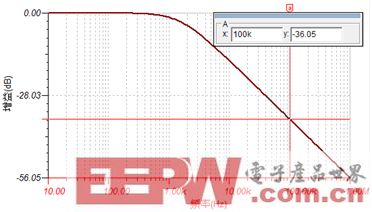

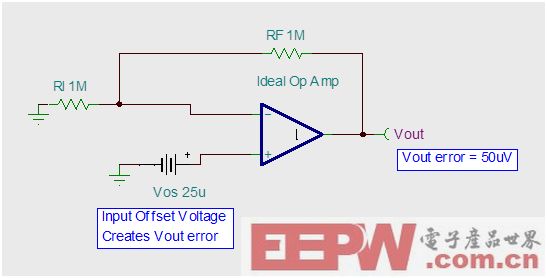

理想情况下,当运放两个输入端的输入电压相同时,运放的输出电压应为0V,但实际情况确是,即使两输入端的电压相同,放大电路也会有一个小的电压输出。如下图,这就是由运放的输入失调电压引起的。

当然严格的定义应为,为了使运放的输出电压等于0,必需在运放两个输入端加一个小的电压。这个需要加的小电压即为输入失调电压Vos。注意,是为了使出电压为0,而加的输入电压,而不是输入相同时,输出失调电压除以增益(微小区别)。

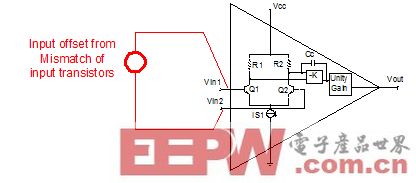

运放的输入失调电压来源于运放差分输入级两个管子的不匹配。如下图。受工艺水平的限制,这个不匹配是不可避免的。差分输入级的不匹配是个坏孩子,它还会引起很多其他的问题,以后介绍。

曾经请教过资深的运放设计工程师,据他讲,两个管子的匹配度在一定范围内是与管子的面积的平方根成正比,也就是说匹配度提高为原来的两倍。面积要增加四倍,当到达一个水平时,即使再增加面积也不会提高匹配度了。提高面积是要增加IC的成本的哦。所在有一个常被使用的办法,就是在运放生产出来后,进行测试,然后再Trim(可以理解为调校了)。这样就能使运放的精度大在提高。当然,测试和Trim都是需要成本的哦。所以精密运放的价格都比较贵。这段只当闲聊,呵呵。

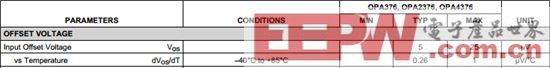

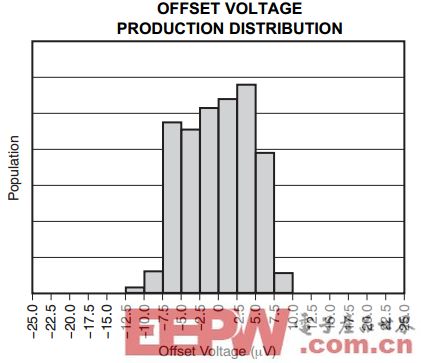

我们关注输入失调电压,是因为他会给放大电路带来误差。下面就要分析它带来的误差。在计算之前,我们再认识一个让我们不太爽的参数,失调电压的温漂,也就是说,上面提到的输入失调电压会随着温度的变化而变化。而我们的实际电路的应用环境温度总是变化的,这又给我们带来了棘手的问题。下表就是在OPA376 datasheet上截取下来的参数。它温漂最大值为1uV/℃(-40℃to 85℃)。一大批运放的Vos是符合正态分布的,因此datasheet一般还会给出offset分布的直方图。

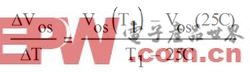

当温度变化时,输入失调电压温漂的定义为:

刚忘记了另一个重要的参数,就是运放输入失调电压的长期漂移,一般会给出类似uV/1000hours或uV/moth等。有些datasheet会给出这一参数。

下面举例计算一下OPA376,在85℃时的最大失调电压,主要是两部分,一部分是25度时的输入失调电压,另一部分是温度变化引起的失调电压漂移。

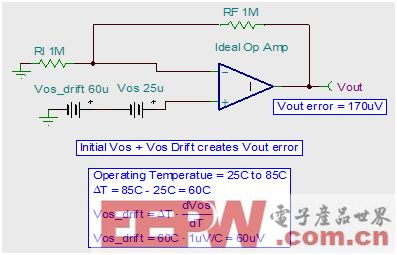

具体步聚如下图。从结果来看似1uV/℃温漂,在乘上温度变化时,就成为了误差的主导。因此,如果设计的电路在宽的温度范围下应用,需在特别关注温漂。

Vos(85℃)= 25uV+60uV=85uV.

如果放大电路的Gain改为100,则最大输出失调电压就为8.5mV。这是最差的情况。

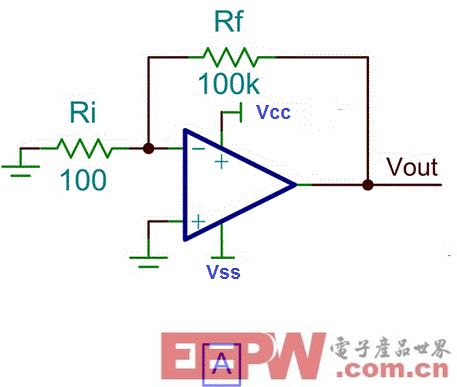

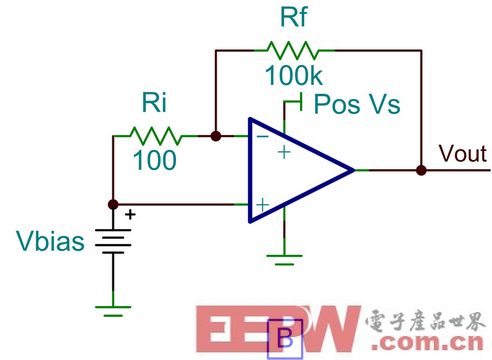

关于输入失调电压的测试在"运放参数的详细解释和分析-part2,如何测量输入偏置电流Ib,失调电流Ios"中有介绍,感兴趣的话,可以去看看。还有简单的测试方法,如下图:

Vos = Vout/1001

需要提醒的是,使用简易方法测试单电源运放的输入失调电压时,需要将输入端短路并提供一个低噪声的稳定电压偏置。如下图。

TI的运放水平在全球一直处于领选地位,下面列一些TI的低温漂运放,它们的最大漂移只有0.05uV/℃。输入失调电压Vio最大值只有5uV。

OPA734

OPA735

OPA334

OPA335

还有一些温漂很小的运放,

OPA333,OPA188

感兴趣的可以在下面的列表中找到。

http://www.ti.com.cn/paramsearch/cn/docs/parametricsearch.tsp?family=analog&familyId=3028&uiTemplateId=NODE_STRY_PGE_T