每个人都知道运放应该使用靠近运放供电管脚的退耦电容,对吗?但为什么要使用这个退耦电容呢?举个例子,如果没有合适的退耦,运放会更容易产生振荡。了解使用退耦电容的原因能够增加你对这个问题的理解和认知。

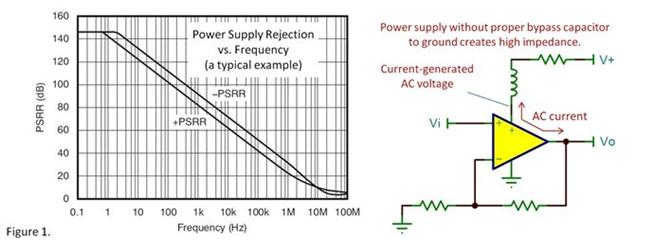

电源抑制比是运放抑制供电发生变化的能力。如图1所示,在低频段,运放的电源抑制比是非常高的,但是随着频率的增加,电源抑制比会减小。在高频段,较小的电源抑制比可能会导致运放振荡。

我们经常认为,外部的供电噪声会影响运放。但是,运放自身会产生一些问题。例如,负载电流来源于运放的供电。如果没有合适的退耦,运放的供电端的阻抗就会非常大。这会导致负载的AC电流在供电端产生一个AC电压,从而构成了一条无意的,不可控的反馈回路。供电端的电感能够放大该AC电压。在高频段,运放的电源抑制比比较低,这条无意的反馈回路能够引起振荡。

当然,运放内部电路也会带来一些影响。如果没有一个稳定的供电,内部电路的节点之间也可能会产生反馈回路。内部电路的设计是为了使运放工作得更稳定,供电端有较低的电阻。如果没有稳定的低阻抗的电源供电,运放的工作可能变得特别异常且不可预测。

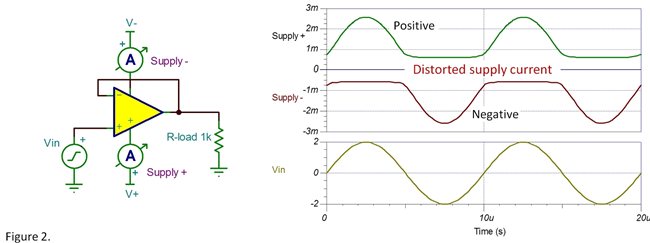

给运放的输入端加一个干净的正弦波,较差的退耦产生的反馈回路上可能是一个失真的正弦波。如图2 所示,在供电端的信号电流经常是失真的,因为它仅仅是正弦信号的一半。如果正端供电和负端供电的电源抑制比不相同,也会使输出波形失真。

如果负载电流很大,该问题会变得更加严重。电抗性负载会产生相位,使负载电流产生相移,这可能会加剧这个问题。容性负载在反馈回路上会产生额外的相移,很有可能会产生振荡。为了消除这些问题,我们需要较大容值的钽电容作为退耦电容,并且需要特别注意该电容的布局,应直接连接在供电引脚上,且越近越好。

当然,并不是所有的低质量的退耦都会使运放产生振荡。如果没有足够的正向反馈,或者相移并不是很大,并不会使运放振荡。但是,运放的性能会大大下降。较大的过冲,较长的建立时间会影响频率响应和脉冲响应。

在以前的博客中曾经讨论过,TINA或者其它的SPICE仿真工具不能很好地仿真出这些现象。SPICE中的电压源是相当稳定的,不会随着负载电流而产生变化。要想仿真出实际的供电阻抗非常难,并且结果是不准确的。电源抑制比的值用我们最好的模型macro来仿真,但是,反馈回路上的相位关系不可能完全准确。一般情况下,仿真是很有用的,但并不能准确地预测出上述现象。

你不应该成为一个偏执狂------没有必要对退耦太过要求。对一些特别敏感的情况和潜在的问题提高警惕就可以了。适当的理解和认知会使模拟设计变得更好。

谢谢阅读,欢迎评论。

我要赚赏金

我要赚赏金