最近学习了一个FPGA检测矩阵键盘的实例,分享给大家。

`timescale 1ns / 1ps

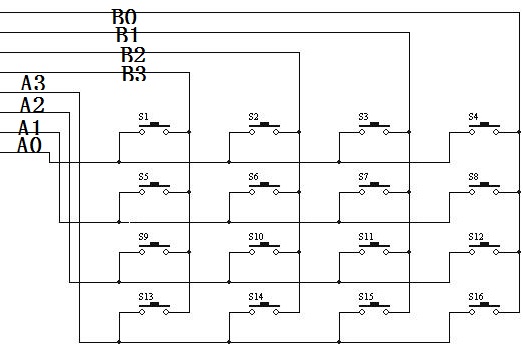

module KEY4(clk,A,B,R);

input clk;

input [3:0] A;

output [3:0] B;

output [3:0] R;//开发板的数码管有译码电路,直接输出二进制数即可。

reg [1:0] c;

reg [3:0] R,B;

always@(posedge clk)

begin

c<=c+1;

case(c)

0: B=4'B0111;

1: B=4'B1011;

2: B=4'B1101;

3: B=4'B1110;

endcase

case({B,A})

8'B0111_1110 : R=4'H0;

8'B0111_1101 : R=4'H1;

8'B0111_1011 : R=4'h2;

8'B0111_0111 : R=4'h3;

8'B1011_1110 : R=4'H4;

8'B1011_1101 : R=4'H5;

8'B1011_1011 : R=4'H6;

8'B1011_0111 : R=4'H7;

8'B1101_1110 : R=4'H8;

8'B1101_1101 : R=4'H9;

8'B1101_1011 : R=4'HA;

8'B1101_0111 : R=4'HB;

8'B1110_1110 : R=4'HC;

8'B1110_1101 : R=4'HD;

8'B1110_1011 : R=4'HE;

8'B1110_0111 : R=4'HF;

endcase

end

endmodule

我要赚赏金

我要赚赏金