ADI近期在搞一个“PCB设计大吐槽”的活动,看到“老司机”们的“倾诉”,菜鸟们可是能从中学到不少呢,今天咱不推活动,就看看“老司机”们的“倾诉”吧~当然你要想参加活动,那就移步至https://ezchina.analog.com/thread/15990

![]()

没做什么要求特别高的板子,一般都是布通就能OK,所以也谈不上有什么酸爽的回忆。倒是刚开始布板时喜欢用镜像功能现在记忆游戏,特别是一些芯片的封装,经常弄反,俗话说一遭被蛇咬十年怕艹绳,现在自己做封装总担心做反了。

![]()

镜像这是偶尔不小心会犯的错误,功能验证行的问题居多

刚开始布PCB的时候,会犯一下小毛病,如焊盘和敷铜混在一起,焊接的时候麻烦,受热慢,热量散失的快

功率器件和精密的小信号布线要分开,易受温度影响的器件也要和功率器件分开布等

![]()

第一次做一个高阻抗传感器前置放大器时候,由于传感器产生的电流很微弱,所以用了一个偏置电流fA级的运放,心想应该不会有什么问题。板子做出来测了测数据和理论值相差太大。翻阅资料才知道这种超低偏流的放大器要加保护环,而且要保证足够的绝缘。

![]()

第二版pcb在输入端加入了保护环,并且换成了陶瓷板,最后实测数据才与理论值相符,完美,哈哈

![]()

PCB设计要跟加工工艺相结合。生产部门的工程师经常抱怨研发工程师的PCB设计太差太糟糕,不是焊盘设计太小了,就是元件焊接空间不够,等等。有一天,作为PCB设计老鸟,被吐槽了。有个产品,用到很多贴片电解电容,加工后,发现部分电容引脚上的焊锡膏没有完全熔化。经过分析后,发现电解电容布局太贴近,成半包围布局,造成包围内的引脚没有完全受热,还有高的元器件引脚方向最好要和回流炉内热风的方向垂直。有了这个教训,以后PCB设计会注意到加工可靠性设计。

![]()

在学校的时候第一次帮老师画板子,用的AD软件自带的板子形状(也就是选择出一块背面是黑色的板形),根本不知道还要用keep-out layer或机械层做板形边框,文件发出去没多久就被厂家返回来了

![]()

我做无源晶振的SM-49封装时犯过低级错误。那次在给引脚PAD设定的助焊层时误以阻焊层的大小考虑,结果覆盖面大了。在板上,晶振周边通常铺地,而软件默认PAD与铺铜间距小于助焊层突出部分导致地的铜裸露出一小块。这种情形并不影响功能但在回流焊时却有短路的隐患

![]()

记得刚毕业做作新产品导入时,我首先拿到Gerber文件开了钢网,我也没在意各层的颜色按层名称开了正确的钢网(一般顶层是红色

底层是蓝色,但那次颜色刚好反了),拿到PCB我懵逼了,PCB厂家竟然是按颜色处理的,竟然连镜像的丝印也处理了! (希望能看明白我说的意思)

(希望能看明白我说的意思)

![]()

要用特氟龙接线柱再搭棚走线。当年那个滨松的光电二极管nA级的电流根本没想过那么多就随便用运放做出来,居然还能勉强用一下

![]()

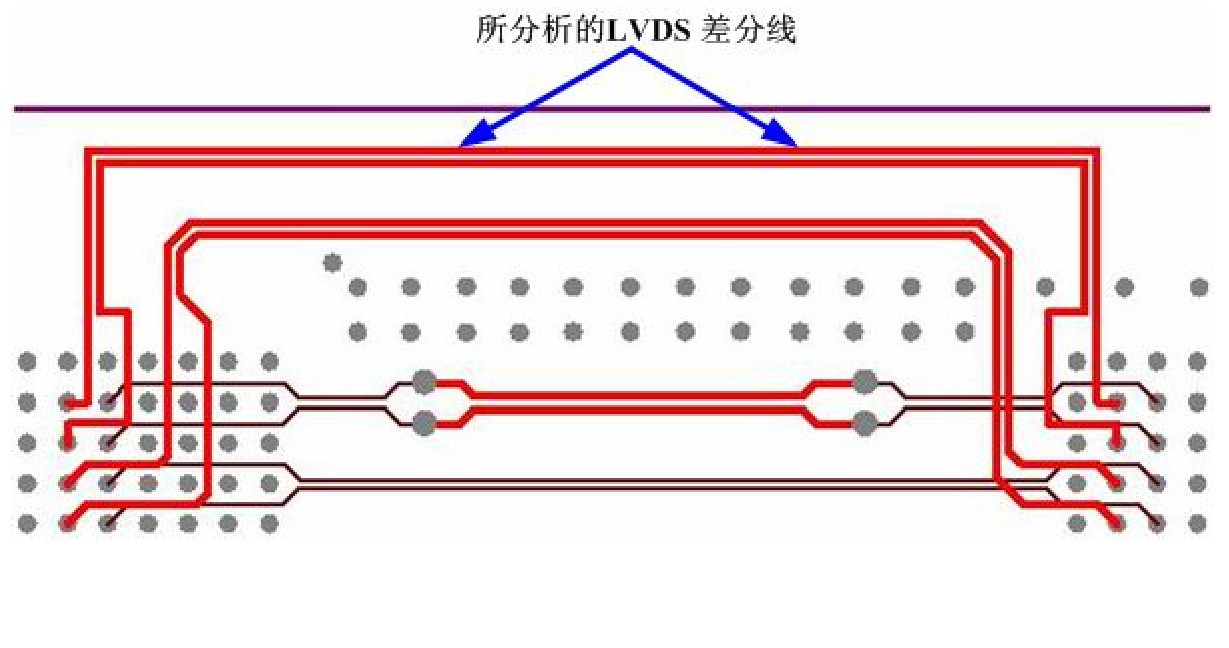

所要分析的差分对中两根走线长度不同,这就意味着差分对上的信号之间存在着相位差,它破坏了差分信号磁场对消的优点,且导致电磁干扰(EMI)的产生。差分对的走线长度不同还会导致差分阻抗的不连续。除此之外,该差分对 90o转弯将会引起阻抗不连续性,产生反射。

如果采用 45o转弯可以减小这种不连续性反射。背板中这段差分线的总长设计为77mm。这里我们有意加长差分对的长度,目的是观察 500Mbps 高速信号在背板较长的 LVDS 互连线中传输的状况,以确定这种高速信号较长距离传输的可行性;另一方面观察上述不连续性对高速数据传输的影响,从而找出影响高速信号传输性能的各种因素,以便采取措施,尽可能地优化高速

信号的传输特性,保证高速系统的可靠工作。

![]()

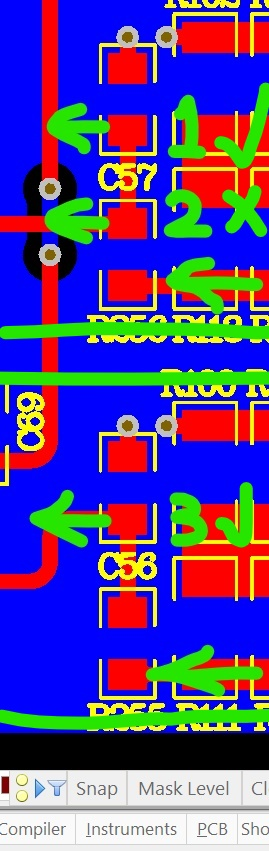

1、做RC滤波的时候,电容C的引线长了些,导致滤波效果不好,有好多高频毛刺,这是因为引线上存在电阻和寄生电感。从下图标记3的地方引出的信号明显好于从2处引出的信号,2处走线应改改到1处走线。

![]()

2、以前做过光电管信号检测,电流很小pA级别,当时用的电路还是官方推荐的,就是不行,后来才发现,PCB材质并不是绝对绝缘,还是存在一定的绝缘阻抗的,通过开槽的方法,有效提高了导线间的绝缘电阻,这都是坑啊

:lol

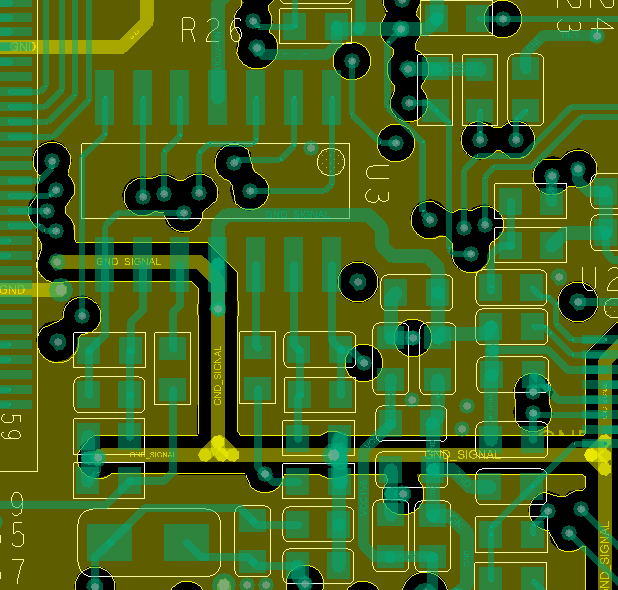

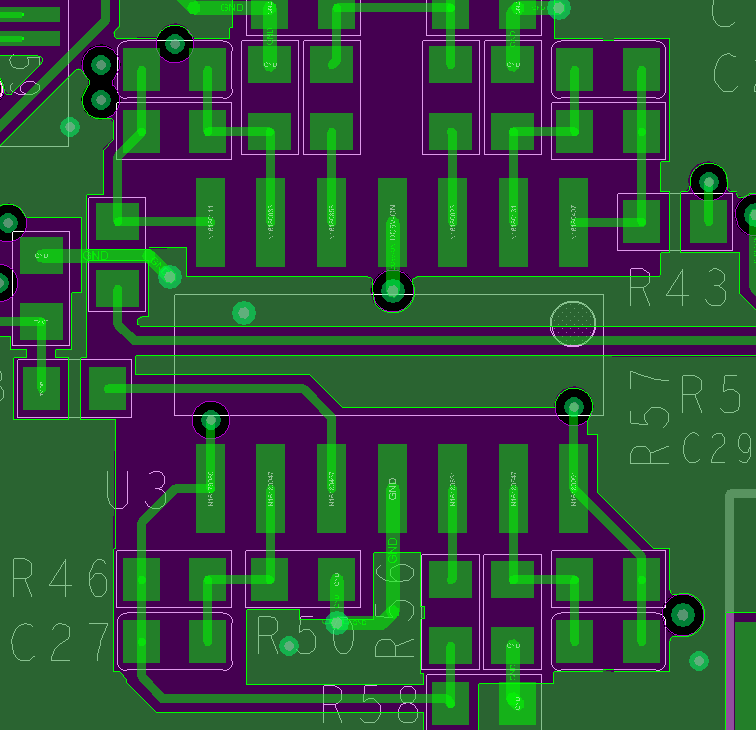

如图中U3是一个视频放大器,上图为修改之前,下图为修改之后,修改前视频输出有干扰,经过对PCB分析,发现原来在U3下面没有完整的地平面,放大器附近元器件布局较乱,后来修改布局,在U3下面保证了完整的地平面,这样视频输出无干扰。