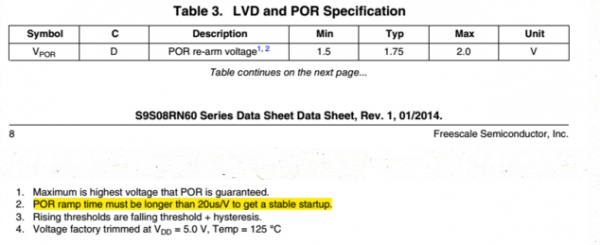

b. 某些MCU内部集成的POR上电复位电路对VDD/VCC的去耦电容(容值大小和温漂一致性)选择有一定的要求满足其POR上电爬升斜率(ramp slew rate)的要求。比如Freescale S08RN系列MCU对电源POR re-arm的要求:

b. 某些MCU内部集成的POR上电复位电路对VDD/VCC的去耦电容(容值大小和温漂一致性)选择有一定的要求满足其POR上电爬升斜率(ramp slew rate)的要求。比如Freescale S08RN系列MCU对电源POR re-arm的要求:

c. 对于MCU的电源芯片选择,不但要考虑其供电能力(对于汽车电子应用,一般根据datasheet计算出MCU最大工作电流,留2~3倍裕量,在500mA以内的选择LDO即可,大于500mA的一般选择DC-DC)和还要考虑其不同电源的上电时序(对于复杂MCU,比如Qorivva MPC57xx系列多核MCU),需要根据具体的MCU datasheet来选择和设计;

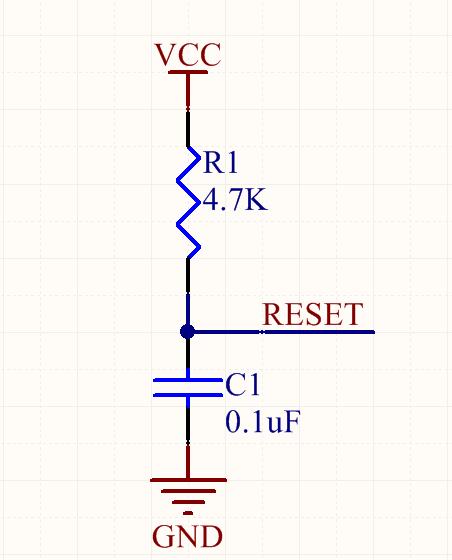

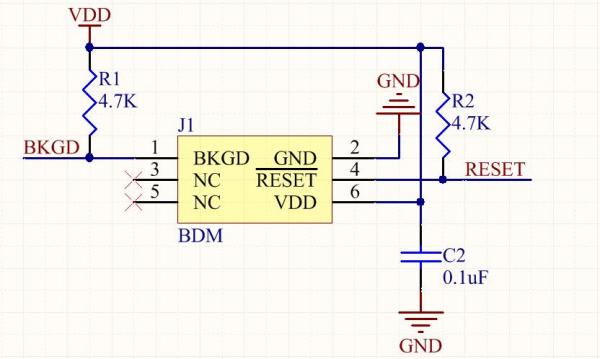

硬件设计tips:a. 关于复位电路的上拉电阻和滤波电容大小的选择,需要根据具体的MCU POR上电复位时序要求以及需要的滤波效果来确定;b. 当然,很多时候MCU的RESET管脚也与电源芯片的LVR输出管脚或者外部看门狗芯片的复位输出接在一些,这个时候就需要考虑:电源芯片的LVR阈值和MCU本身的LVR阈值是否阈值,如果电源芯片的LVR阈值高于MCU的LVR阈值,那么MCU就无法正常进入LVI中断;

硬件设计tips:a. 关于复位电路的上拉电阻和滤波电容大小的选择,需要根据具体的MCU POR上电复位时序要求以及需要的滤波效果来确定;b. 当然,很多时候MCU的RESET管脚也与电源芯片的LVR输出管脚或者外部看门狗芯片的复位输出接在一些,这个时候就需要考虑:电源芯片的LVR阈值和MCU本身的LVR阈值是否阈值,如果电源芯片的LVR阈值高于MCU的LVR阈值,那么MCU就无法正常进入LVI中断;MCU上电之后需要及时对外部看门狗芯片进行喂狗,以防止其溢出复位,保证MCU正常工作;

| MCU系列 | 内部时钟源/精度 | 外部时钟源 |

| S08系列 | 32.768KHz IRC/±2% | 4~20MHz无源晶振 |

| 1KHz 低功耗LPO/~% | ||

| S12(X)系列 | 1MHZ IRC/±1.3% | 4~16MHz无源晶振/有源时钟(仅S12X系列MCU) |

| 10KHZ低功耗自主时钟ACLK/±5% | ||

| MagniV s12Z系列 | 1MHZ IRC/±1.3% | 4~20MHz无源晶振 |

| 20KHZ低功耗自主时钟ACLK/±6% | ||

| Qorivva MPC56xx/57xx系列 | 16MHz FIRC/±5% | 4~16MHz无源晶振/有源时钟和32~40KHz RTC晶振 |

| 128KHz SIRC/±10% | ||

| KEA系列 | 32.768KHz IRC/±0.8% | 4~24MHz无源晶振(RANGE=0)或者31.25~39.0625KHz RTC晶振(RANGE=1) |

| 1KHz 低功耗LPO/~% | ||

| S32K系列 | 48MHz FIRC/±1% | 4~40MHz无源晶振/有源时钟 |

| 8MHz SIRC/±3% | ||

| 128KHz SIRC/±10% | 32.768KHz RTC晶振 |

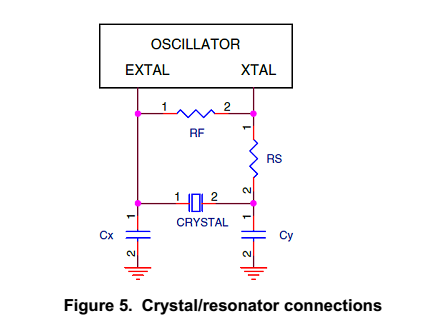

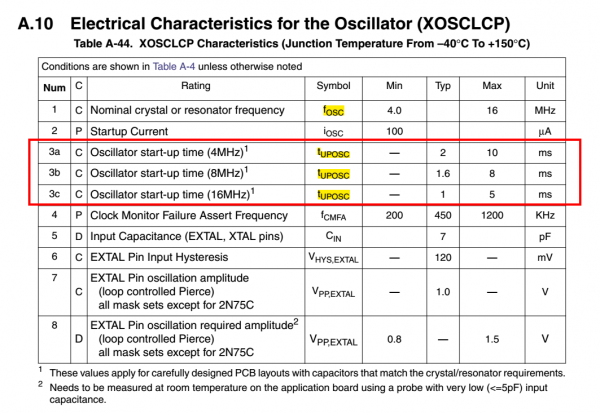

硬件设计tips:a. MCU的时钟(Oscillator)参数不同,一般在其datasheet的电气参数中给出,不同的晶振频率对于不同的启动时间,频率越高启动时间越短,但对外的EMC就越差,所以一般选择中间频率,然后通过内部时钟倍频模块(比如PLL)倍频到较高的MCU工作内核频率和总线频率;

硬件设计tips:a. MCU的时钟(Oscillator)参数不同,一般在其datasheet的电气参数中给出,不同的晶振频率对于不同的启动时间,频率越高启动时间越短,但对外的EMC就越差,所以一般选择中间频率,然后通过内部时钟倍频模块(比如PLL)倍频到较高的MCU工作内核频率和总线频率;

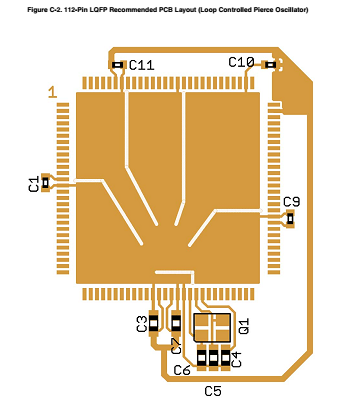

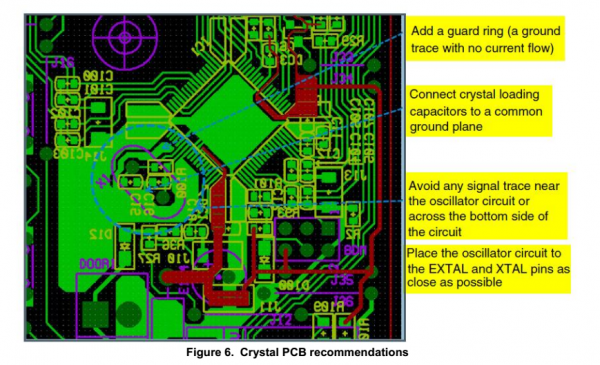

b. 在外部时钟电路设计时,为了提高其抗干扰能力建议:在外部晶振电路应该靠近MCU时钟管脚,走线越近越好,且外围覆铜包地。在时钟电路附件减少其他信号走线,特别是高数数字信号走线应该远离时钟电路以避免相互干扰。如下是一个推荐的MCU外部晶振时钟电路推荐PCB Layout:

b. 在外部时钟电路设计时,为了提高其抗干扰能力建议:在外部晶振电路应该靠近MCU时钟管脚,走线越近越好,且外围覆铜包地。在时钟电路附件减少其他信号走线,特别是高数数字信号走线应该远离时钟电路以避免相互干扰。如下是一个推荐的MCU外部晶振时钟电路推荐PCB Layout:

C. 在内部IRC时钟精度可以满足系统设计要求的情况下,尽量不要使用外部时钟。因为IRC时钟源不但功耗低,其对外的电磁辐射小、可干扰能力强,EMC特性好,同时也可以节省外部时钟电路的成本。

C. 在内部IRC时钟精度可以满足系统设计要求的情况下,尽量不要使用外部时钟。因为IRC时钟源不但功耗低,其对外的电磁辐射小、可干扰能力强,EMC特性好,同时也可以节省外部时钟电路的成本。d. 虽然MCU内部集成的PLL/FLL倍频单元可以将时钟倍频到datasheet规定的最大系统时钟和总线时钟频率,但在满足系统设计内核CPU计算速度和外设工作频率的情况下,尽量使用较低的系统时钟和总线时钟。一来可以降低对外的频率辐射,获得较好的EMC特性;二来可以降低MCU系统功耗(频率越高,时序逻辑电路的动态功耗也越大)。

| MCU系列 | 程序下载和调试接口 |

| S08系列 | BDM |

| S12(X)系列 | BDM |

| MagniV s12Z系列 | BDM |

| Qorivva MPC56xx/57xx系列 | JTAG/NEXUS |

| KEA系列 | SWD |

| S32K系列 | JTAG |

| 管脚(#) | 符号定义 | 功能定义 |

| 1 | BKGD | BDM协议同步信号和数据信号(双向通信) |

| 2 | GND | 信号地 |

| 3 | NC/PDO | 悬空,不接/分析(Profiling)数据输出* |

| 4 | RESET | 复位信号 |

| 5 | NC/PDOCLK | 悬空,不接/分析(Profiling)数据输出时钟* |

| 6 | VDD | 目标MCU电源(输出--供电/输入--目标MCU上电检测) |

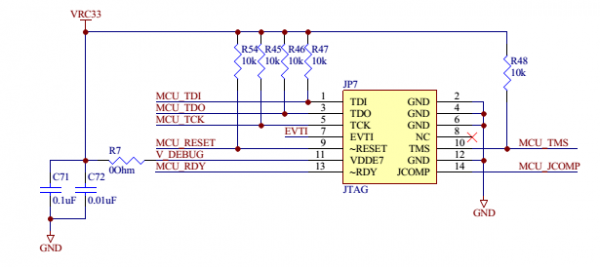

4.2. JTAG接口JTAG--Joint Test Action Group--联合测试工作组,是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA和32位MCU器件等。标准的JTAG接口4条JTAG功能信号线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线,具体定义如下表:

4.2. JTAG接口JTAG--Joint Test Action Group--联合测试工作组,是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA和32位MCU器件等。标准的JTAG接口4条JTAG功能信号线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线,具体定义如下表:| 符号定义 | 功能定义 |

| TMS | 测试模式选择 |

| TCK | 测试同步时钟 |

| TDI | 测试数据输入(MCU-input, Debugger--output) |

| TDO | 测试数据输出(MCU-output, Debugger--input) |

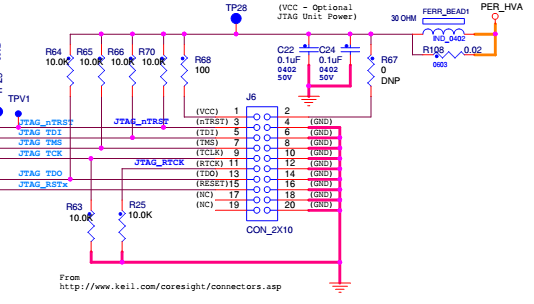

适合于ARM Cortex M4F内核的S32K系列MCU和Cortex A5内核的MAC57D5xx(Halo)系列MCU的20-pin JTAG典型电路如下:

适合于ARM Cortex M4F内核的S32K系列MCU和Cortex A5内核的MAC57D5xx(Halo)系列MCU的20-pin JTAG典型电路如下:

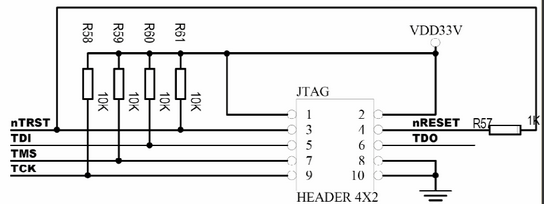

除此之外,常用的还有10-pin的JTAG接口,其典型电路如下:

除此之外,常用的还有10-pin的JTAG接口,其典型电路如下:

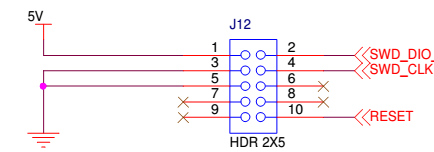

4.3. SWD接口SWD--Single Wire Debug单线调试,是ARM推出针对其ARM Cortex M系列内核的调试协议,其相较于传统的JTAG调试协议,接口信号线只有2根--单线时钟SWCLK和单线数据输入输出SWDIO,占用MCU的I/O更少,不但设计更加简单,在同样的封装下可提供更多的用户I/O,同时其又与JTAG接口兼容复用,如下表;

4.3. SWD接口SWD--Single Wire Debug单线调试,是ARM推出针对其ARM Cortex M系列内核的调试协议,其相较于传统的JTAG调试协议,接口信号线只有2根--单线时钟SWCLK和单线数据输入输出SWDIO,占用MCU的I/O更少,不但设计更加简单,在同样的封装下可提供更多的用户I/O,同时其又与JTAG接口兼容复用,如下表;| JTAG | SWD | 功能定义 |

| TMS | SWDIO | 单线数据输入输出,用于控制信息数据和调试数据接收以及程序下载串行传输 |

| TCK | SWCLK | 单线时钟,用户通信同步 |

| TDI | 未使用 | |

| TDO | 未使用 |

硬件设计tips:a. 下载和调试接口电路应该靠近MCU放置,避免过长走线;b. 尽快BKGD和TMS、TCK、TDI及TDO在MCU内部有弱上电,但还是建议设计下载和调试接口电路在外部加上4.7K~10KΩ的上拉电阻,以保证其工作稳定;

硬件设计tips:a. 下载和调试接口电路应该靠近MCU放置,避免过长走线;b. 尽快BKGD和TMS、TCK、TDI及TDO在MCU内部有弱上电,但还是建议设计下载和调试接口电路在外部加上4.7K~10KΩ的上拉电阻,以保证其工作稳定;c. 建议在下载和调试接口电路的电源VDD/VCC管脚上加一个0.1uF的滤波电容,以保证电源的稳定;

对于JTAG/SWD接口,TMS/SWDIO和TCK/SWCLK上的一系列脉冲信号也可能导致MCU进入debug模式,CPU内核和外设无法正常工作;

以上就是今天跟大家分享的内容。希望对大家有用。

本微信公众号已经发布的个人原创精品----嵌套嵌入式系统技术文章链接如下,欢迎大家参考学习,并转发分享:

汽车电子expert成长之路公众号系列文章列表

浅谈嵌入式MCU开发中的三个常见误区

浅谈嵌入式 MCU 软件开发之应用工程的堆与栈

浅谈嵌入式MCU软件开发之中断优先级与中断嵌套

浅谈嵌入式MCU软件开发之代码风格与代码优化

浅谈嵌入式MCU软件开发之startup过程详解(从复位向量到main函数之前的准备工作)

浅谈嵌入式MCU软件开发之startup过程详解(在CodeWarrior 5.1 中实现RAM自定义初始化)

浅谈嵌入式MCU软件开发之S12(X)系列MCU 中断ISR在CodeWarrior 5.1 IDE 中的三种写法

浅谈嵌入式MCU硬件设计之MCU最小系统电路

S12(X)系列MCU的片上存储器资源与分页访问机制详解(一)

S12(X)系列MCU的片上存储器资源与分页访问机制详解(二)

使用 Cyclone 离线编程器对 S12(X)和 MagniV S12Z 系列 MCU 片上 NVM 编程

Qorivva MPC56xx/57xx系列MCU的模式控制与切换(片上外设资源使能与功耗控制)

S32DS 使用 tips--使用Flash from file下载S19或elf文件

CodeWarrior IDE使用tips之map文件详解

CodeWarrior IDE使用tips之prm链接文件详解(自定义存储器分区以及自定义RAM数据初始化与在RAM中运行函数)

胡恩伟NXP汽车电子FAE

我要赚赏金

我要赚赏金