现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。1 FPGA 常用配置方式

(1)边界扫描JTAG 方式。单板调试阶段常用JTAG 模式,该方式需要控制器,FPGA 等芯片JTAG 接口构成菊花链,且在该模式下,控制器其他功能不能使用。

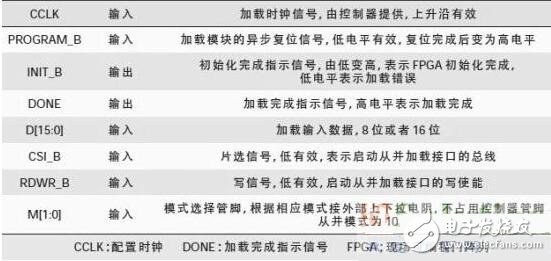

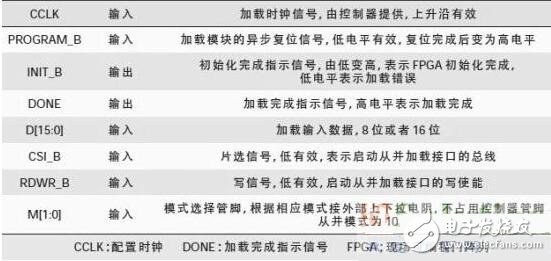

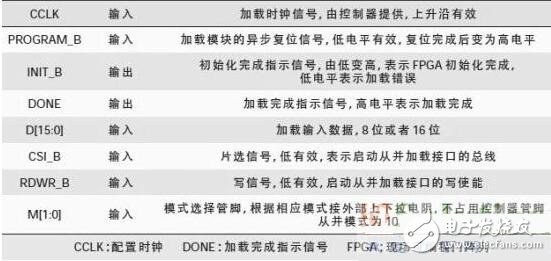

(3)主从方式。该方式最主要的缺点是配套使用的FLASH](4)从并方式。即文章中探讨的FPGA 加载方案。2]以Xilinx 公司Spartan - 6 系列FPGA 为例,与从并加载相关的管脚如表1 所示。

表1 从并加载管脚名称由表1]

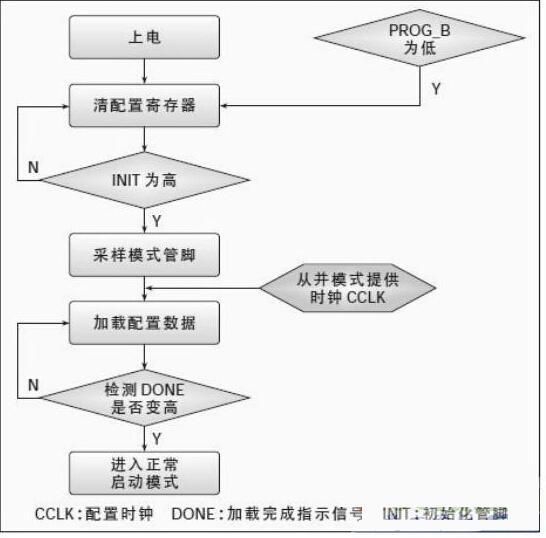

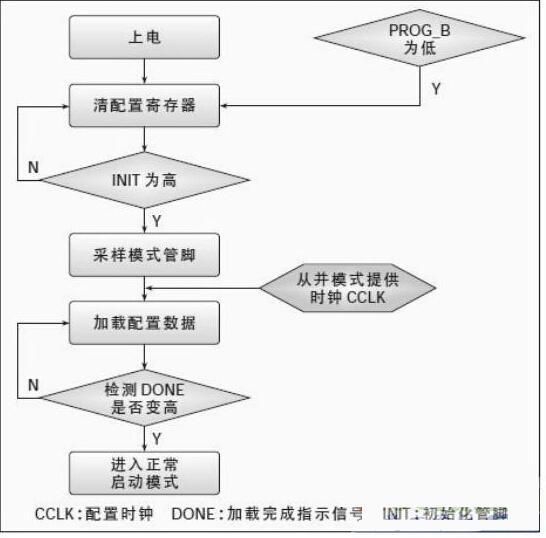

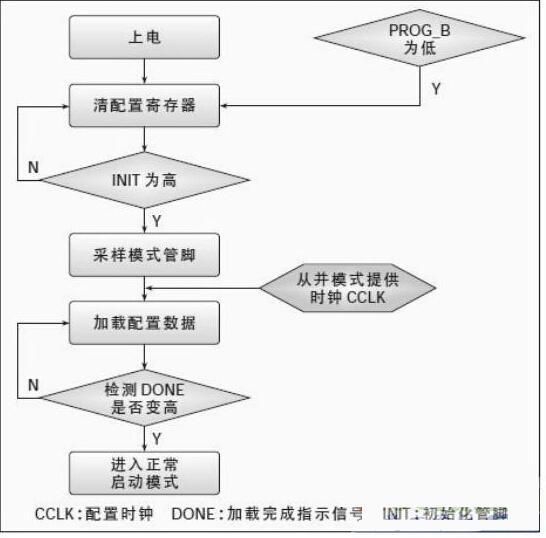

图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH 中搬移到DDR 颗粒;真正需要加载时,再通过DDR2 接口将配置数据搬移到CPU 的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。

图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH 中搬移到DDR 颗粒;真正需要加载时,再通过DDR2 接口将配置数据搬移到CPU 的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。

图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH 中搬移到DDR 颗粒;真正需要加载时,再通过DDR2 接口将配置数据搬移到CPU 的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。

图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH 中搬移到DDR 颗粒;真正需要加载时,再通过DDR2 接口将配置数据搬移到CPU 的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。

图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH 中搬移到DDR 颗粒;真正需要加载时,再通过DDR2 接口将配置数据搬移到CPU 的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。 我要赚赏金打赏帖

我要赚赏金打赏帖